界面形成手法による SiO<sub>2</sub>/β-Ga<sub>2</sub>O<sub>3</sub>(001)バンドアライメントの違いの考察 Investigation of SiO<sub>2</sub>/β-Ga<sub>2</sub>O<sub>3</sub>(001) band alignment differences by interface formation processes

<sup>1</sup>東京大学大学院工学系研究科マテリアル工学専攻, <sup>2</sup>東京大学大学院新領域創成科学研究科物質系専攻, <sup>3</sup>物材機構 ○武田大樹 <sup>1</sup>, 女屋崇 <sup>2</sup>, 生田目俊秀 <sup>3</sup>, 喜多浩之 <sup>1,2</sup>

<sup>1</sup>Dept. of Materials Engineering, The Univ. of Tokyo, <sup>2</sup>Dept. of Advanced Materials Science, The Univ. of Tokyo, <sup>3</sup>NIMS ○D. Takeda <sup>1</sup>, T. Onaya <sup>2</sup>, T. Nabatame <sup>3</sup> and K. Kita <sup>1,2</sup>

E-mail: takeda@scio.t.u-tokyo.ac.jp

【はじめに】 $\beta$ -Ga<sub>2</sub>O<sub>3</sub>の MOS 構造の特性を理解する上で絶縁膜とのバンドアライメントの定量的な把握が欠かせないが、過去の報告値には一貫性がなく、系統的な再評価が必要である。我々は既に、 $\beta$ -Ga<sub>2</sub>O<sub>3</sub>(001)自身のバンドダイアグラムを正しく決定することで、SiO<sub>2</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>(001)スタックにおいて、それぞれのバルクの物性のみから予想されるバンドオフセットの推定値( $\Delta E_{V,Bulk}$ )と、実際のバンドオフセットの測定値との違いを議論してきた[1-2]。本研究では、異なる成膜手法や様々なアニール条件を用いて形成したスタックについてバンドオフセットを評価し、形成手法によるバンドアライメントの違いについて考察した。

【実験方法】n型の $\beta$ -Ga<sub>2</sub>O<sub>3</sub>(001)エピウェハを希釈 HF 中で洗浄後、SiO<sub>2</sub>を2つの方法で成膜した。1つ目は~ $10^{-2}$ PaのO<sub>2</sub>雰囲気中で Si を蒸着源とする電子線(EB)蒸着であり、もう1つは((CH<sub>3</sub>)<sub>2</sub>N)<sub>3</sub>SiH (TDMAS)を原料とする原子層堆積(ALD)法である。ALD 法は基板温度300°Cで、酸素プラズマを用いて行った。これら2つのSiO<sub>2</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>(001)スタックに対し、600°C または1000°Cで1~3時間のアニールを行った後、XPS 価電子帯スペクトルから既報と同様の方法[1]で価電子帯オフセットを決定した。

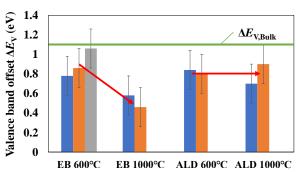

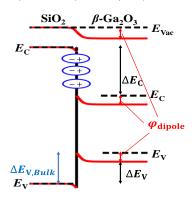

【結果及び考察】Fig. 1 に EB 蒸着および ALD 法によって成膜を行った  $SiO_2/\beta$ - $Ga_2O_3(001)$  のそれぞれの価電子帯オフセットについてアニール条件による違いを示す。EB 蒸着、ALD 法ともにアニール時間による価電子帯オフセットの顕著な違いは見られなかった。ALD 法を用いた場合アニール温度による価電子帯オフセットの変化はほとんどなかった。それに対して、EB 蒸着では価電子帯オフセットが顕著に小さくなった(伝導帯オフセットの増大を意味する)。Fig. 2 に示す通り、一般にバンドアライメントは、それぞれの材料の持つ価電子帯端エネルギー準位の差(バルク項( $\Delta E_{V,Bulk}$ ))と、界面に形成されるダイポール効果(界面項( $\varphi_{dipole}$ ))の 2 つの因子で決定される。ALD 法の場合はバルク項が支配的である一方、EB 蒸着の場合には、アニール温度に応じて界面構造が敏感に変化しており、界面項が無視できないと解釈できる。尚、本研究の一部は JSPS 科研費の助成により行われた。[1] 武田、喜多、第69回応用物理学会春季学術講演会、24a-E302-13(2022). [2] D. Takeda and K. Kita, IWGO2022, Pos 1-36(2022).

Fig. 1 Variation of valence band offset as a function of annealing temperature after deposition by EB or ALD.

Fig. 2 Band alignment of  $SiO_2/\beta$ -Ga<sub>2</sub>O<sub>3</sub> considering the effect of interface( $\varphi_{dipole}$ ).