# Top-down Fabrication of Ge/Si core/shell Nanowire Channels for Vertical-type Field Effect Transistors

#### International Center for Materials Nanoarchitectonics (MANA), National Institute for Materials Science

### (NIMS)<sup>1</sup>, Univ. of Tsukuba<sup>2</sup>

## °Chao Le<sup>1,2</sup>, Yonglie Sun<sup>1</sup>, Wipakorn Jevasuwan<sup>1</sup>, Naoki Fukata<sup>1,2</sup>

#### E-mail: chaole0903l@gmail.com

#### Introduction

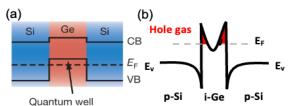

Nowadays Field Effect Transistors (FETs) has a significantly wide range of application in electronic devices. In this case, higher performance types of FETs are required. The structure of the FET and using materials, are very important. For the structure, scaling the size and increase the number of gates can significantly improve the performance. However, dopant impurities affect the carrier mobility. To solve problems caused by scaling, core/shell structure nanowires (NWs) was appeared to our sight[1]. We decided to use undoped Ge as a core and Boron-doped Si as a shell. The mobility of Ge is greater than Si, so we chose Ge as the core. On the other hand, there are energy bandoffsets between Ge and Si and the trap-shaped structure will be formed in the heterojunction. Depending on the Fermi level position, hole gas can be accumulated in the quantum well [2]. (Fig.1)

In this study, we focused on top-down method to fabricate vertical type Ge/Si core/shell NWs and demonstrate hole gas accumulation in the NW as evidence of successful fabrication.

#### **Experimental section**

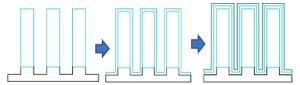

500~600 nm Ge layer were deposited onto p-Si substrate by Chemical Vapor Deposition (CVD). Then the Ge layer was covered by a resist layer using spin coating and patterns with five kinds of different diameters were formed by EB lithography. MgO layers were then deposited on to the resist as a mask. After lifting off the mask, we performed Bosch Etching to remove the area without MgO to form NWs. The NWs were loaded into CVD chamber again to form i-Ge shell and p-Si shell. (Fig.2)

#### **Results and discussion**

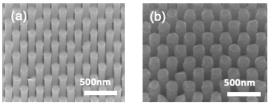

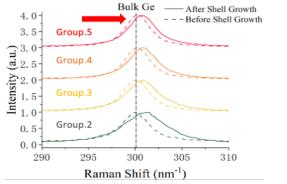

SEM observation and Raman spectra analysis were used to characterize the fabricated structure and demonstrate hole gas accumulation. The SEM images showed the comparison between before & after the shell formation (Fig.3). The Raman result showed the change of Ge peak position after the shell formation. The reason is the stress effect caused by the different lattice constants between Ge and Si crystals. The Ge optical phonon peak also showed asymmetric broadening due to the Fano effect. We fitted the Ge optical phonon peak by using Fano equation[3] and analyzed the Fano parameters of q and  $\Gamma$ . As a result, we successfully demonstrated the hole gas accumulation in the i-Ge region of the i-Ge/p-Si core/shell NWs.

#### References

- [1] Xiang J, Lu W, Hu Y, et al. Nature, 441 (2006) 489.

- [2] Fukata N, et al. ACS Nano, 9 (2015) 12182.

- [3] Zhang X, Jevasuwan W, Sugimoto Y, et al. ACS Nano, (2019) 13403.

Fig 1. (a) Quantum well formation caused by the connection of Ge and Si with different band energy level, it can confine carriers. The quantum well in this Si/Ge/Si structure has a raised shape, indicate the main carriers are holes. (b) Energy band curving caused by the Si/Ge/Si heterojunction, due to the hole gas accumulation in quantum well.

Fig 2. The experiment process of fabricating i-Ge/p-Si core/shell NW by using Chemical Vapor Deposition

**Fig 3.** SEM figures of group 4 (actual diameter: 90 nm) Ge nanowire (GeNW) array compare between **(a)** before shell growth, **(b)** after shell growth.

**Fig 4.** Comparison of Raman spectra of group 2~5 GeNW arrays between before & after shell formation. The Ge peak shows an upshift after the shell growth, because the stress effect between the Ge/Si core-shell structure due to different lattice constants of Ge and Si.