## Digest of Tech. Papers The 7th Conf. on Solid State Devices, Tokyo, Sep. 1975

A-3-2

Micro-probe Auger Analysis

of Si Migration in Al Metallization for LSI

T. Inoue, S. Horiuchi, H. Shimizu\*, and T. Ishida\*\*

Toshiba R & D Center, Electrotechnical Lab.\*, Nippon Electric Varian Co.\*\* Kawasaki, Kanagawa Tanashi, Tokyo\* Fuchu, Tokyo\*\*

The failure analysis is very important to improve the yield and reliability of LSI circuits. For a past few years, many investigators have studied about Al metallization failure mechanism with scanning electron microscopy  $(\text{SEM})^{1),2}$  and electron probe micro-analysis  $(\text{EPMA})^{3)}$ . This paper describes about the application of the micro-probe Auger electron spectroscopy (AES) to the analysis of metallization failure at Al-Si contacts which is one of the serious failure modes in LSI.

Usually, Al metallization is subjected to a heat treatment at between 400°C and 500°C to obtain good ohmic contacts after Al interconnection definition. However, during the heat treatment, silicon dissolves into aluminum and migrates in the Al metallization away from the contacts while pits grow into the silicon to a depth sufficient to short out underlying junctions. The amount of Si which dissolves into the aluminum depends on the temperature and time of the heat treatment, the conduction type of the silicon, the crystallographic orientation of the substrate, and the metallization thickness.

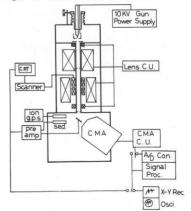

Recently, AES has been proved to be useful for in-line process control for LSI fabrication<sup>4)</sup>. However, it is still difficult to analyze small areas on LSI chips by using a conventional AES equipment due to a large beam diameter and non-imaging mechanism. The newly developed micro-probe Auger analyzer<sup>5)</sup> is most suitable for the analysis of Al-Si contacts in LSI since it has an excellent spacial resolution of less than 1 µm and analyzing areas can be imaged. The principle of the micro-probe AES is illustrated schematically in Fig. 1. Electrons accelerated

at 10 kV are focused to be a beam diameter of less than 1  $\mu$ m with magnetic type condenser and objective lenses. The electron spot is scanned and a secondary image or an absorbed current image is observed on the cathode ray tube (CRT). The electron spot can be stopped at any position on the image and Auger analysis of this point can be performed with a cylindrical mirror analyzer (CMA). This apparatus has following AES operation modes; 1) point analysis, 2) in-line analysis and 3) Auger electron imaging. Combination with an ion gun makes it possible to obtain in-depth profiling. This equipment is evacuated to  $10^{-9}$  Torr range with ion pumps.

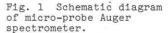

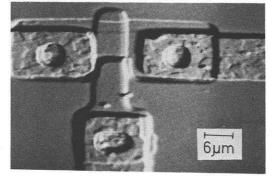

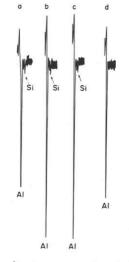

In this experiment, the samples were prepared by using conventional n-channel Si-gate technology. The substrates used were 20  $\Omega$ -cm, (100) oriented, boron doped p-type Si wafers and phosphorus diffusion was performed to form the diffused layers such as source and drain regions of MOS transistors. Al was evaporated 1 µm in thickness. After Al interconnection definition, Al metallization was heat treated under the various conditions of heat treatment temperature and time. The photograph in Fig. 2 was taken in SEM mode with the micro-probe AES equipment after Ar ion milling for 90 min and shows the feature around the contact holes. The sample was heat treated at 450°C for 90 min in N<sub>2</sub> ambient. The cross sectional view at the contact hole is illustrated in Fig.3. The analyzed positions were about 5 µm apart from each other and indicated by arrows in the figure. Figure 4 shows the Auger spectra taken in point analysis mode with the micro-probe AES equipment at the positions mentioned above. It is clear that the Si/Al Auger peak height ratio decreases with the distance from the contact hole. This fact shows the migration of Si in the Al metallization during the heat treatment.

More data taken under the various conditions and on the in-depth profiles will be given at the conference.

## References

- 1) G. L. Schnable, Proc. IEEE 57 ('69) 1570

- 2) R. J. Anstead and S. R. Floyd, IEEE Trans. Electron Devices ED-16 ('69) 380

- 3) J. O. McCardin and H. Sankur, Appl. Phys. Letters 19 ('71) 524

- 4) T. Inoue, S. Horiuchi, S. Yoshii, and Y. Tanuma, Proc. 6th Conf. Solid State Devices, Tokyo, ('74), Suppl. J. Japan. Soc. Appl. Phys. <u>44</u> ('75) 329

- 5) K. Hayakawa, H. Okano, S. Kawase and S. Yamamoto, J. Appl. Phys. 44 ('73) 2575

Fig. 2 Scanning image of transistor in LSI.

Fig. 4 Auger spectra taken at the positions indicated in Fig. 3.

Fig. 3 Cross section at a contact hole.