Digest of Tech. Papers The 7th Conf. on Solid State Devices, Tokyo, Sep. 1975

## B-2-3 DESIGN AND EVALUATION OF 64K-BIT MAGNETIC BUBBLE MEMORY CHIP

M. Hiroshima, A. Asano, S. Yoshizawa, N. Saito, and M. Kasai Central Research Laboratory, Hitachi, Ltd.

Kokubunji, Tokyo 185

It is urgently desired to realize mass capacity magnetic bubble memory chips when their practical level applications are considered. Up to present, 16k-bit chips have been developed and satisfactory operations are confirmed 1),2). Basing on these results, we have fabricated major-minor organized 64k-bit chips. All the device functions have been examined and found fully operational at a rotating field frequency of 100kHz with a reasonable bias field margin. In this paper, we describe the design of 64k-bit chips and report the results of the operation.

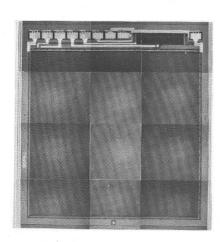

In Fig.1, a photograph of the 64k-bit chip is shown. The basic chip design has been modified only insofar as a bit size and detector circuits are concerned; the functions of replicate/annhilate, generation and transfer remain as described for the 16k-bit  $chip^2$ . There are 128 minor loops. Each minor loop contains 513 bits with a bit size of  $20\,\mu$ m x  $20\,\mu$ m. The detailed dimensions of propagation circuits are listed in Table 1. Those optimum values g, w, and s are determined by examining propagation performance of various circuits with different pattern element sizes. Two fish-bone detectors are placed adjacently in the chevron stretcher. These are so arranged as to do noise-cancelling in an efficient way<sup>3)</sup>.

The LPE film is of  $(YSm)_3(FeGa)_50_{12}$  with a demagnetized strip width of 4.7  $\mu$  m.

The chip tested was fabricated with no defects. Namely, all minor loops operated normally. The overall operating bias field margin diagram is shown in Fig. 2. The measurements were carried out in a memory module. Typically a margin of 10% was observed. The detailed results on all device functions will be presented.

This work is contracted with the Agency of Industrial Science and Technology, Ministry of International Trade and Industry, as a part of the National Research and Development Program "Pattern Information Processing System".

## REFERENCES

1) P. I. Bonyhard et al., IEEE Trans. Mag., MAG-9, 433 (1973)

- 2) M. Hiroshima et al., 1974 IECE Conf. No.267

- 3) P. C. Michaelis et al., IEEE Trans. Mag. MAG-11, 21 (1975)

Table ]. T-Bar circuit parameters

| Period $\lambda$ | 20 µ m  |

|------------------|---------|

| T-Bar gap g      | ].3 µ m |

| Bar width w      | 2.6 µ m |

| Spacing * s      | ].] µ m |

| T-Bar thickness  | 4000 Å  |

|                  |         |

<sup>\*</sup> Distance between the circuit and the LPE film

Fig.]. The 64k-bit memory chip. The chip size is  $6.5 \, \text{mm} \times 6.0 \, \text{mm}$ .

Fig. 2 Operating margins.