Digest of Tech. Papers The 7th Conf. on Solid State Devices , Tokyo, Sep. 1975 E-2-3 Note on Limitations in MOS LSI's from a Design Viewpoint

## Hisashi HARA

Toshiba Reserch and Development Center 1, Komukai Toshiba-cho, Saiwai-ku, Kawasaki, 210

Along with recent rapid progress towards high density integration of semiconductor devices, one pays attention to the fundamental limitations by various physical phenomena<sup>1-5)</sup>. Hoeneisen and Mead<sup>1)</sup> proposed a silicon-gate MOS transistor of minimum size in MOS LSI's from a fundamental design viewpoint. In their discussion are neglected effects of device temperature and scattering in channel length, both of which are basically important to determine the minimum device size in LSI's. On the other hand, Dennard et al<sup>3)</sup> present a device scaling principle on a basis of present day MOS transistors used in MOS LSI's. The scaling approach is well generalized but the scaling relationship cannot be applied exactly for a gate threshold voltage ( $V_T$ ). Deviation from the relationship in case of low resistivity substrate should be noted especially for a short-channel MOS device of a low supply voltage.

Here we discuss the limitations of MOS LSI's from a similar design viewpoint but by taking into consideration the effects of temperature rise of the device and its nonuniform distribution on the chip and also the effects of scattering in channel length of actual devices on the chip.

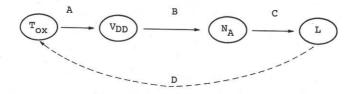

The most important parameters in MOS LSI design are channel length (L),thickness of gate oxide  $(T_{OX})$ , substrate impurity concentration  $(N_A)$  and supply voltage  $(V_{DD})$ . These parameters are related to one another through gate breakdown, drain avalanche breakdown, gate turn-on characteristics and so on. We propose a method to determine values of  $T_{OX}$ ,  $V_{DD}$ ,  $N_A$  and L, which is schematically shown in Fig.l. At first  $T_{OX}$  is assumed and then  $V_{DD}$  is taken as high as possible under the conditions of A (see Fig. 1), in order to obtain the shortest switching time.  $N_A$  and L are also determined considering successively the condistions B and C. The results are as follow:

$T_{ox} \simeq 100 \text{ Å},$

ş

$$V_{DD} \approx 3 V,$$

$N_A \approx 5 \times 10^{16} \text{ cm}^{-3},$

L ≃ 0.35 µm

Other parameters such as diffusion depth, distance between two diffusion layers, crosssectional area of metal lines, power dissipation density and switching speed will be presented at the Conference.

-103-

A l. gate oxide breakdown

2. conductance between gate electrode and substrate

B 1. drain avalanche breakdown

2. effect of device temperature rise on  ${\tt V}_{\rm T}$

C 1. modulation of channel length

short-channel effect due to scattering in device channel length

- D 1. Power dissipation density

- 2. switching speed

Fig. 1 Diagram Illustrating Relationship among  $T^{}_{\rm OX},~V^{}_{\rm DD},~N^{}_{\rm A}$  and L.

## References

- B. Hoeneisen and C.A. Mead, Solid State Electronics, <u>15</u>, p. 819 (1972)

- B. Hoeneisen and C.A. Mead, Solid State Electronics, <u>15</u>, p. 891 (1972)

- R.H. Dennard et al., IEEE J. of Solid-State Circuits, SC-9, p. 256 (1974)

- J.T. Wallmark, Electronic Engineering, <u>47</u>, No. 564, p. 52 (1975)

- 5) R.W. Keyes, Proc. of IEEE, <u>63</u>, p. 740 (1975)