Digest of Tech. Papers The 8th Conf. (1976 International) on Solid State Devices, Tokyo

A-1-3 Stepped Electrode Transistor: SET

Tetsushi Sakai, Yoshio Sunohara, Yutaka Sakakibara, Junichi Murota Musashino Electrical Communication Laboratory Nippon Telegraph and Telephone public Corporation, Tokyo, Japan

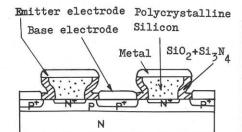

A completely new structure of bipolar transistor was devised where high performance can be achieved without using precise photolithography and metalization techniques. The transistor is called Stepped Electrode Transistor or SET.

Figure 1 shows the structure of SET, in which the arsenic doped polycrystalline silicon which is processed to have a shape of inverse trapezoid is used as a

part of the emitter electrode. The edge of the inverse trapezoid serves to form a

shadow in making the base and emitter electrode through evaporation. The emitter

electrode is separated from the base electrode electrically as the shaded area

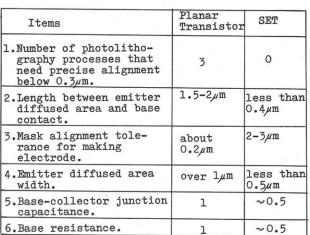

makes a gap between them. The characteristics of SET are compared with those of a

conventional planar transistor in Table 1.

To fabricate SET, double layers of polycrystalline silicon of about 0.6 $\mu$ m thick are deposited on the base diffused layer through CVD process. The upper non-doped layer is of 0.2 $\mu$ m thick and the lower layer with 0.4 $\mu$ m thickness is highly doped with arsenic (lxl0<sup>21</sup>atoms/cm<sup>3</sup>).A masked etch leaves inverse trapezoid polycrystalline silicon with overhanging sides on the roof top of the emitter electrode, because highly doped polycrystalline silicon is etched 10 times faster than non-doped one in the HF-HNO<sub>3</sub>-H<sub>2</sub>O system.

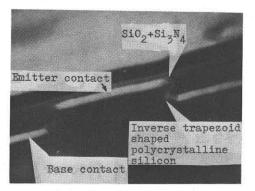

An unmasked ion-implantation process is used to selectively increase the susceptibility for etching of the unshadowed insulating layers  $(SiO_2+Si_3N_4)$ , i.e., the base contact and emitter contact windows. (Fig.2) The etching speed of the area implanted with boron ions  $(1x10^{15}/cm^2$  at 40KeV) is 2 to 3 times faster than the unimplanted area in the buffered HF solution for  $SiO_2$  film whereas 3 to 4 times faster in the boiled  $H_3PO_A$  for  $Si_3N_A$ film.

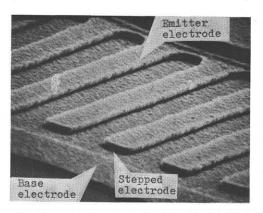

Figure 3 shows a scanning electron micrography of SET. Figure 4 shows the frequency characteristic of  $|S_{21}^e|$  and  $|H_{21}^e|$ , where cut off frequency of  $|S_{21}^e|$  is 8.4GHz. This frequency is higher than that of the planar transistor by about 2GHz. The emitter area of this transistor is about 350 $\mu$ m<sup>2</sup>.

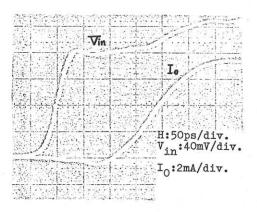

Figure 5 shows the switching characteristics of integrated transistor in which rise time is 150psec. The emitter area is about  $40\mu\text{m}^2$ .

The author would like to acknowledge the continuing guidance and encouragement of Drs.M.Watanabe.H.Toyoda.M.Hirai and J.Sudou.

Fig.1 SET structure.

Table 1. SET Features compared to the conventional same size planar transistor.

Fig.2 Cross-sectional view after a selective etching process.

(scanning electron micrography)

Fig. 3 Scanning electron micrography of SET.

Fig.4 |S<sub>21</sub>|, |h<sub>21</sub>| frequency characteristics.

Fig.5 Switching characteristic of SET. (IC)