Digest of Tech. Papers

# The 8th Conf. (1976 International) on Solid State Devices, Tokyo

# Nonvolatile Semiconductor Memory

Yoshio Nishi and Hisakazu Iizuka

A-3-7 (INVITED)

> Toshiba Research and Development Center Tokyo Shibaura Electric Co., Ltd. Kawasaki, Kanagawa

Semiconductor memory with nonvolatility has been widely studied with much interest, and several attempts have been tried to explore feasibility of an erasable read only memory (EROM), a nonvolatile read write memory (NVRWM), optical data storage, content addressable memory, discrete analog signal processing etc. Physical mechanism of nonvolatile data storage in various kinds of device structures has been also extensively studied, which has strongly stimulated rather basic research on the emission, injection and transport phenomena of electronic charges in the silicon-insulator systems. The purpose of this paper is to describe the recent progress in the nonvolatile memory devices and to discuss various features of these devices. Although there might be many interesting subjects in the field of amorphous memory, we would restrict our scope within the silicon technology.

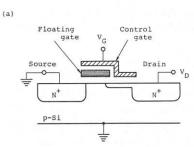

There are two typical device structures; (a) a metal-insulator-oxide-silicon (MIOS) structure and (b) a floating gate structure, both of which are utlizing the change in the threshold voltage of MOS transistor due to increase/decrease of charges in the gate insulator region to store the data with nonvolatility.

# MIOS devices

Nonvolatility comes from the electronic charges which are being captured at the traps in the insulator, (I), unless otherwise being released by the external voltage applied to the gate. Since the writing/erasing speed strongly depends upon the mechanism of charge transfer through the oxide layer, most of the MIOS devices have tunnelable oxide of approximately 20 Å thick which results in faster speed compared to other mechanisms. The speed is again accelerated by introducing excess traps in the insulator, which has been achieved by the modified structures of metalinsulator-metal-oxide-silicon<sup>(1)</sup> and metal-insulator-silicon-oxide-silicon<sup>(2)</sup>. The insulator is usually silicon nitride (MNOS) and sometimes aluminum oxide (MAOS). The writing/erasing of an information is by the direct tunneling of either electrons or holes through the ultra thin oxide in most of the cases, but a combination of the direct tunneling and the avalanche injection was tried to make single polarity writing.<sup>(3)</sup> Typical writing/erasing speed is in the order of 10<sup>-3</sup> to  $10^{-5}$ sec at 30 volts, and is much faster in case of the modified structures. As the EROM or the electrically alterable ROM (EAROM) MIOS gives rise to satisfactory characteristics, and 256-, 1024- and 2048-bit LSI memory have been developed already. On the other hand significant problem has been pointed out when one expects to use the MIOS device as an NVRWM, which is the performance degradation during writing/erasing cycles. After 10<sup>5-8</sup>cycles, the threshold voltages for both "1" and "0" levels start changing and the retentivity also starts degrading, and thus the NVRWM has been difficult to be practically realized. The only approach to solve the problem is to utilize the MIOS memory to back up a conventional volatile memory, where the MIOS is operated only when power shortage occurs and the endurance of more than  $10^{5-8}$  cycles would not be required any more. A 256-bit NVRWM has been developed by this approach. (4) The other interesting combination of MIOS with CCD has been proposed and will be a candidate for a nonvolatile memory with very high bit density<sup>(5)</sup>. As far as the physical mechanism is concerned, there still remain many unrevealed aspects even in the characterization of traps, and some of them essentially require better understanding of the silicon-silicon dioxide system.

# Floating gate devices

In the structural point of view of the floating gate EROM transistors, there are two types: a floating gate structure (FAMOS)<sup>6</sup> and a stacked gate structure (SAMOS)<sup>(7)</sup>. The hot carrier injection type EROM's are divided into two groups in terms of programming method, one is avalanche injection and the other is non-avalanche injection.<sup>(8)</sup> The former uses electron injection from the avalanche plasma induced at the drain junction, and the latter uses the injection of hot electrons accelerated during transit in the channel or the injection of electrons by bulk p-n junction (ATMOS)<sup>(9)</sup>.

In the case of the avalanche injection, rather high voltage is required to program the memory. On the other hand, the hot carrier injection is more desirable for memory application because of possibility of reducing the programming voltage. The channel accelerated injection method was proposed by Dill et al. <sup>(10)</sup> for the MNOS structure device.

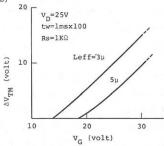

In Fig.1 is shown the relationship between the control gate voltage,  $V_{G}$ , and the threshold voltage shift,  $\Delta V_{TM}$ , in the <u>channel injection type MOS erasable</u> (CHIME) memory transistor. It is clear that the control gate voltage is effective to control  $\Delta V_{TM}$  and the effective channel length,  $L_{eff}$ , has large influence on the generation of hot electrons. Though the ease in the hot electron generation means the possibility of poor memory retention, it has been revealed that the transistors having the effective channel length of longer than  $3\mu$ m is reliable enough for PROM applications.

Structure of memory transistor Fig.1 CHIME memory transistor

#### References

(1)D.Kahng, W.J.Sundburg, D.M.Boulin and J.R.Ligenza: Bell Syst.Tech.J.53(1974)1723.

(2)M.Horiuchi:IEDM Abstracts 24.2(1972)Washington, D.C.

(3)Y.Uchida et al.: IEEE J.Solid State Circuits SC-10(1975)288.

(4)S.Saito et al.: Proc. 7th Conf.Solid State Devices (1975)185.

(5)M.H.White, D.R.Lampe, J.L.Fagan, F.J.Kub and D.A.Barth: IEEE J.Solid State Circuits SC-10(1975)281.

(6)D.Frohman-Bentchkowsky:Solid State Electronics <u>17</u>(1974)517.

(7)H.Iizuka et al.: IEEE Trans. Electron Devices ED-23(1976)379.

(8)Y.Tarui,Y.Hayashi and K.Nagai:Proc. 5th Conf.Solid State Devices (1973) 348.

(9) J.F.Verway and P.Kramer: IEEE Trans. Electron Devices ED-21(1974)631.

(10)H.G.Dill and T.N.Toombs: Solid State Electronics 12(1969)981.