Digest of Tech. Papers The 9th Conf. on Solid State Devices, Tokyo  $\mathrm{A}\!-\!7\!-\!4$  High Power Gate Turn-Off Thyristors

M. Azuma, A. Nakagawa, K. Takigami Toshiba Research and Development Center Kawasaki, Kanagawa, Japan

High power gate turn-off tyristor (GTO) development is one of the recent topics in the field of power electronics, because of the remarkable merit wherein forced commutation is not required for inverter and chopper applications. In several previous publications on high power GTO's, maximum gate turn-off currents (I<sub>ATO</sub>) in the 50 to 200 Ampere range have been reported. This paper describes design considerations for increasing  $I_{\mathrm{ATO}}$  beyond the above values, as well as the results of characterization carried out on the developed device units.

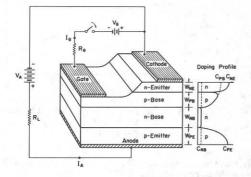

Figure 1 shows the schematic configuration of a mesa-type GTO-segment, including impurity doping profiles and other design parameters. An actual GTO-unit consists of a plurality of the segments, which are parallel-connected to each other.

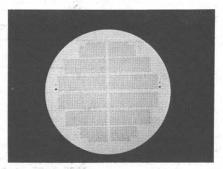

As a result of numerous experimental fabrications and characterizations, the mask pattern shown in Fig. 2 was determined. It consists of 260 emitter fingers 4 mm in length and 300 microns in width.

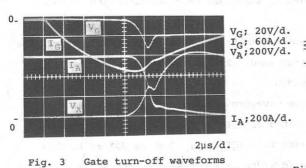

Figure 3 shows an example of the waveforms during the gate turn-off transient. Operational turn-off gain, defined as (IA/IG, peak), is around 4. This value depends upon gate current rising rate  $(dI_G/dt)$ , which is 30A/µs in this example. Anode voltage rising rate  $(dv_A/dt)$  is suppressed by the snubber circuit to an appropriate value, in order to decrease the switching loss.

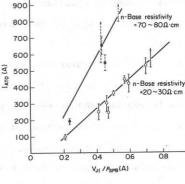

Figure 4 shows experimental IATO vs. (VJ1/0SPB) characteristics with n-base resistivity  $\rho_{\rm NB}$  as a parameter, where  $V_{\rm J1}$  stands for the gate-cathode breakdown voltage, and  $\rho_{\text{SPB}}$  stands for the p-base layer sheet resistance. Theoretical

## Fig. 1 GTO-segment configuration

Fig. 2 Mask pattern for GTOunit

-81-

estimation of  $V_{\rm J1}$  can be made on assumptions of the Gaussian doping profile and the linearly-graded p-n junction, while  $\rho_{SPB}$  can be calculated as a function of the doping profile and the carrier mobility. As is shown in the figure,  $I_{\mathrm{ATO}}$  can be increased by increasing (V\_{J1}/ $\rho_{\rm SPB})$  . This fact is similar to one obtained by Wolley. Another way of increasing  $I_{ATO}$  is to increase  $\rho_{NB}$ , which is, to our knowledge, a new result. By making  $(V_{{

m J1}}/

ho_{{

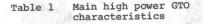

m SPB}})$  sufficiently high, excess carriers are efficiently removed from the p-base, thus resulting in a high  $I_{ATO}$ . It is assumed that the dependence on  $\rho_{\rm NB}$  is due to a wide depletion layer formation Main characteristics for the fabricated devices during the turn-off process. are given in Table 1.

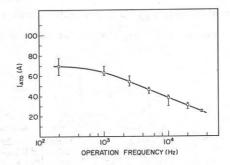

Another group of test samples were fabricated for I ATO vs. frequency characteristics evaluation. Figure 5 shows a result for the 3 Ohms load resistance, 30 percent duty.

| Forward blocking voltage<br>(Tj=115°C)                         | 1300V |

|----------------------------------------------------------------|-------|

| Maximum gate turn-off<br>current(Tj=110°C)                     | 600A  |

| On-state voltage(I <sub>A</sub> =600A)                         | 1.5V  |

| Surge on-state current<br>(50Hz, sinusoidal one-cycle<br>peak) | 3500A |

| Latching-Holding current                                       | 2A    |

| Gate turn-on time                                              | 10µs  |

| Gate turn-off time<br>(Tj=110°C, I <sub>A</sub> =600A)         | 12µs  |

| Operation turn-off gain<br>(Tj=110°C, I <sub>A</sub> =600A)    | 4     |

Fig. 4

Maximum gate turn-off currents vs. (V<sub>J1</sub>/ $\rho_{SPB}$ ) char-acteristics with n-base resistivity as a parameter.

REFERENCES

- 1. T.C. New et al., IEEE Trans., Electron Devices, vol.ED-17, pp.706-710, Sept. 1970 2. E.D. Wolley et al., 1973 IEEE Conference Record, pp.251-257

- 3. M.Kurata, 1974 Power Electronics Specialists Conference Record, pp.125-133 4. E.D. Wolley, IEEE Trans., Electron Devices vol. ED-13, pp.590-597, July 1966