## Digest of Tech. Papers The 10th Conf. on Solid State Devices, Tokyo

## ${ m A}-1-2$ N-channel Si-gate MNOS Device for High Speed EAROM

Yuji Yatsuda, Takaaki Hagiwara, Ryuji Kondo, Shinichi Minami and Yokichi Itoh Central Research Laboratory, Hitachi Ltd.,

Kokubunji, Tokyo 185, Japan

In recent years, MNOS devices have been the subject of extensive research.<sup>1)2)</sup> The tangible result has been that several electrically alterable nonvolatile memory have appeared on the market.<sup>3)</sup> However, all of these MNOS memory LSI's are p-channel Al-gate type and retain read cycle limitations owing to the cell structure. Their read access time is greater than 650 ns and their fabrication process is no longer compatible with advanced LSI technology. The purpose of this work is to develop an n-channel MNOS device which has no read cycle limitations as well as to develop a new Si-gate fabrication technology which produces high speed EA memory LSI's.

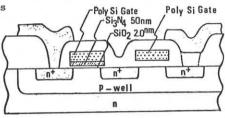

Our memory cell consists of two transistors per bit, i.e. a Si-gate MNOS memory transistor and a Si-gate enhancement mode switching transistor. This configuration frees our device from read cycle limitations. The cross section of the cell is shown in Fig. 1. The MNOS gate is a layered structure of 2.0nm thick tunnellable SiO<sub>2</sub>, 50nm Si<sub>3</sub>N<sub>4</sub> and 0.3 µm poly Si.

An outline of processing steps is as follows: The starting Si wafer is n-type (100), not epitaxial; a memory part and peripheral MOS circuits are formed in each p-type well; MOS gates are prepared by patterning the first poly Si layer; then in the memory part, thin  $\text{SiO}_2$ ,  $\text{Si}_3\text{N}_4$  and the 2nd poly Si layers are successively formed and patterned to make MNOS gates; finally, the N<sup>+</sup> layer is prepared by self aligned phosphor implantation.

In conventional Al-gate MNOS's, a thick SiO<sub>2</sub> layer has been widely used near the source and/or drain junctions. These so called dualgate or trigate devices, are equivalent to the serially connected common gate memory and non-memory transistors. When read addressing, a certain gate bias higher than Vth of the memory part is applied to the common gate and unwilling weak writing occurs in the memory part.

In the Si-gate MNOS transistor no thick  ${\rm SiO}_2$  is used, permitting a large Vth window. The Vth<sub>W</sub>(write state) is  $\geq 2$  volts and Vth<sub>E</sub>(erase state) is  $\leq -3$  volts, at initial write or erase conditions. At read out, addressed gate of the switching MOS transistor is V<sub>DD</sub>(5 volts), whereas the MNOS gate is still 0 volts. Consequently, unwilling weak writing during read out does not take place thereby eliminating read cycle limitations.

In the device, anomalous positive Vth shift caused by applying negative gate voltage<sup>4</sup> which results in the instability of poly  $Si-Si_3N_4$  interface is not observed.

The Si-gate self aligned structure facilitates a memory cell smaller than conventional Al-gate dual or trigate devices. The memory cell of our test devices was

-5-

further reduced to 17.5x17  $\mu m^2$  by 4  $\mu$  technology.

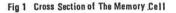

Retentivity is the most important characteristics of MNOS memory LSI's. The Vth change for the device stored under various conditions is shown in Fig.2. The decay rate M= $\partial$ Vth/  $\partial \log_{10}$ t at room temperature storage after 10<sup>4</sup> rewrite cycles is 0.2. Even at 125°C, M is about 0.2 for Vth<sub>E</sub>(<0) and 0.45 for Vth<sub>W</sub>(>0). From the results, a 10-year unpowered data

Retention characteristics

Fig 2

storage capability has been confirmed at 125°C, with further nonvolatility testing now in progress.

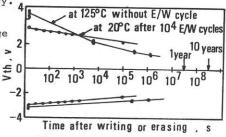

The dependence of write and erase characteristics on the thin  ${\rm SiO}_2$  thichness are shown in Fig.3. With 2.0 nm  ${\rm SiO}_2$  devices, pulse width necessary for writing is 100 µs and erasing is 3ms. Test devices containing a memory array with addressing and I/O circuits have been fabricated. The device can be operated by a single 5volt power supply, thus, a read access time of less than 200 ns has been measured.

The Si-gate MNOS device is compared to a conventional Al-gate MNOS in Table 1. <u>Conclusions</u> The main features of our EA memory devices are summarized as follows:

[1] An n-channel MNOS device is proposed which can be prepared by a Si-gate self aligned process together with Si-gate E/D MOS transistors for the peripheral circuit.

[2] By using a two transistor (MNOS+switching MOS) per bit configuration, read cycle limitation is removed. The cell size is smaller than conventional Al-gate MNOS devices.

[3] The memory device has high speed programming characteristics; write time is about 100µs and erase time is less than several ms. A 10-year nonvola- Fig

tility is confirmed in unpowered condition at 125°C.

[4] Read access time of less than 200 ns has been obtained by a single 5-volt power supply.

[5] The application of this technology should realize large scale EAROM and EA memory on chip devices in the near future.

Authors wish to thank N. Hashimoto, Dr. S. Kubo, Y. Hatsukano, K. Uchiumi and M. Fukuyama for their support and encouragement.

References 1) J. J. Chang, Proc. IEEE <u>64</u>, 1039 (1976)

2) Y. Nishi et al., Proc. The 8th Conf. S.S.D. Tokyo, 191 (1976).

3) S. Saito et al., Proc. The 7th Conf. S.S.D. Tokyo, 185 (1975).

4) P. C. Y. Chen, IEEE, Trans. <u>ED-24</u>, 584 (1977).

| Table 1                          | COMPARISON OF MNOS          | DEVICES                  |

|----------------------------------|-----------------------------|--------------------------|

| PROCESS                          | P-CH. A1-GATE               | N-CH. Si-GATE            |

| POWER SUPPLY<br>(READING CYCLES) | -10 V                       | +5 V                     |

| ACCESS TIME<br>(TYPICAL)         | 650 ns<br>(CLOCK INTERFACE) | 200 ns<br>(FULLY STATIC) |

| DEVICE / BIT                     | 1 or 2                      | 2                        |

| CELL SIZE                        | 650 μm <sup>2</sup>         | 300 µm <sup>2</sup>      |

| READ CYCLE<br>LIMITATION         | 10 <sup>6</sup> ~11         | NO LIMITATIONS           |