## Digest of Tech. Papers The 10th Conf. on Solid State Devices, Tokyo A - 1 - 3 Suppression of Anomalous Drain Current in Short Channel MOSFET Masami Konaka, Hiroshi Iwai, and Yoshio Nishi Research Laboratory, NEC-TOSHIBA Information Systems Inc. Horikawa-cho 72, Kawasaki, Japan

Increasing sensitivity of MOSFET characteristics to two-dimensional geometry, as a consequence of the scaling-down approach, essentially gives rise to several problems such as difficulty in controlling the threshold voltage and the current voltage characteristics. This paper describes two-dimensional analysis of the scaled-down MOSFET with deep ion implantation into channel region to reveal a role of the ion implanted layer on suppression of the broadening of Log  $I_D - V_G$ slope and anomalous excess drain current in the subthreshold region as well as modification of the short channel effects in threshold voltage, and, finally, derives optimum condition for the ion implantation which can allow us larger tolerance in designing very short channel MOSFET.

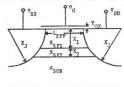

Schematic cross section of the n-channel MOSFET is shown in Fig.1, where  $N_{SUB}$ ,  $N_{SF1}$  and  $N_{SF2}$  are the accepter impurity concentrations in the layers, respectively.  $X_1$ ,  $X_2$  and  $X_J$  are the thicknesses of the two doped layers and the junction depth, respectively.  $T_{OX}$  is the gate thick-

ness, and  $L_{EFF}$  the channel length.  $V_{DD}$ ,  $V_{BB}$  and  $V_{C}$  are the drain voltage, the back gate bias and the gate voltage, respectively. Two basic equations, Poisson's equation and the current continuity equation, were numerically solved by means of Stone's iterative method.

Fig.2 shows some examples of calculation in comparison with experimental

Fig.2. Experimental and calculation log I vs V with V by as a parameter for a uniform substrate impurity profile.

results, which demonstrates excellent agreement. Fig.3 shows typical examples of calculated In - V<sub>G</sub> characteristics for various effective channel lengthes with and without deep channel ion implantation. We should note that broadening of a slope in the subthreshold region and excess drain current become more significant with decreasing channel It is very clear that length. both amount of the excess drain current and the slope of Log I y<sub>c</sub> characteristics are drasticlly improved in case of the ion implanted device with  $\mathbf{L}_{\text{EFF}}$  of

-7-

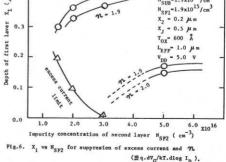

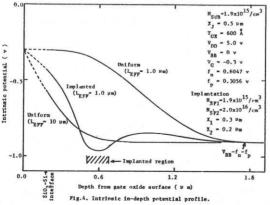

even as small as 1.0 µm. The remainder of the paper will be dedicated to how to interprete the role of ion implanted layer and how to optimize the ion implantation for designing very short channel MOSFET and VLSI. Potential distributions in several MOSFETs are shown in Fig.4. Note that the potential for  $L_{RFF}^{}=1$  µm stays at relatively high level until 1.0 to 1.2 µm in-depth, while the one for longer LEFF drops down quickly with increasing thickness. The ion implanted device with L<sub>EFF</sub> = 1 µm behaves as if it had relatively longer channel length. Thus, the anomalous drain current which is due to a punch-through current in deeper region, shoud be effectively suppressed by the deep-ion implantation of accepter impurity as well as the slope of Log  $I_{D}$  -  $V_{C}$ characteristics. The slope of Log  $\rm I_D$  -  $\rm V_G$  characteristics in the subthreshold region is calculated as a function of the depth of ion implanted layer for various concentrations of  $N_{\rm SF2}$ , and Combinations for  $N_{SF2}$  and the depth  $X_1$  show certain optima for minimizing the plotted in Fig.5. inverse slope n as clearly seen in the figure. Since electron current becomes strongly localized along the surface with increasing back gate bias, the effect of ion implantation on the slope and the excess drain current tends to be less sensitive in comparisn with the zero back gate bias. From Fig.5 and behaviors of anomalous drain current, one can obtain optimum areas surrounded by several X1 - NSF2 curves as described in Fig.6. Consequently, both slope of Log ID - VC characteristics and additionaldrain current in the subthreshold region can be significantly improved by

2.5

choosing appropriate combinations for dose and projected range for ion implantation of accepters into channel region.

The authors wish to thank Dr. K. Natori and Dr. L.M. Dang for valuable descussions.

References

(1) R.H. Dennard et al. : IEEE J. Solid State Circuits, SC-9 (1974) 256.

(2) M.S. Mock : Solid State Electronics, 16

-8-

$N_{SP1} = 1.9 \times 10^{15} / cm^3$  $X_2 = 0.2 \ \mu m$  $x_{j} = 0.5 \mu m$  $x_{0x} = 600 Å$ - 1.0 µm EFF = 5.0 V 2.0 ; N<sub>SF2</sub>=1.5x10<sup>16</sup>/cm<sup>3</sup> ; N<sub>SF2</sub>=2.0x10<sup>16</sup>/cm<sup>3</sup> ; N<sub>SF2</sub>=3.0x10<sup>16</sup>/cm<sup>3</sup> 2 X ; N<sub>SF2</sub>=5.0x10<sup>16</sup>/cm<sup>3</sup> ; N<sub>SF2</sub>=1.0x10<sup>17</sup>/cm<sup>3</sup> 0 VBB = 0.0 V 0 1.0

N<sub>SUB</sub>=1.9x10<sup>15</sup>/cm<sup>3</sup>