## $\mathsf{A}-\mathsf{5}-\mathsf{1}$ A NEW FIELD ISOLATION TECHNOLOGY FOR HIGH DENSITY MOS LSI

Tadashi SHIBATA, Susumu KOHYAMA and Hisakazu IIZUKA

TOSHIBA Research and Development Center

Tokyo Shibaura Electric Co., Ltd. Kawasaki, JAPAN

A unique field isolation technology has been developed for n-channel MOS LSI's which has several advantages over the conventional coplanar (also known as LOCOS) technology.

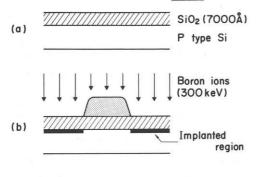

The essence of the new technology is schematically shown in Fig.1. The field oxide of about 7000 Å thickness is firstly grown on a P-type silicon wafer. Then field boron implantation is performed through the field oxide with accerelation energy of 300 keV. The photoresist masks prevent transistor regions from being implanted. The reverse etching technique using HF gas, known as DryOx process, (1) is introduced to remove the oxide right beneath the photoresist, which defines the field oxide, self-aleigned to the boron implanted region. Thereafter the conventional silicon gate technology follows.

Test transistors, ring oscillators and LSI's were fabricated by both technologies, the new technology and the coplanar technology, using the same set of masks. The device characteristics are compared as follows.

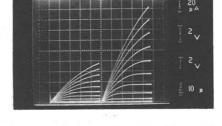

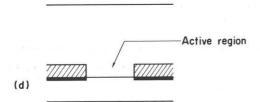

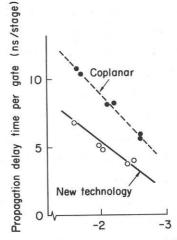

Fig.2 shows the current voltage characteristics of the transistor, where W/L =4 $\mu$ /50 $\mu$  on the mask. The transistor transconductance,  $g_m$ , is nearly doubled by the new technology. The propagation delay times of the ring oscillator are shown in Fig.3. About 40% reduction in delay time is achived. The aspect ratio of the load transistor is W/L=4 $\mu$ /4 $\mu$  on the mask. Smaller  $g_m$  and larger delay time in the coplanar technology are caused by the shrinkage of transistor region due to bird's beak formation. (2) It is concluded that the new technology can achive higher packing density under the same photolithography limitaion, because of the precise opening of the transistor region.

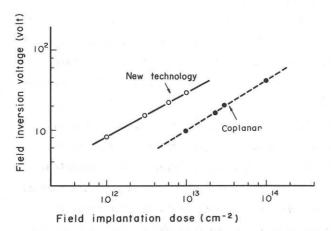

The boron dose dependence of field inversion voltage is shown in Fig.4.

In order to verify the feasibility of the new technology a 16-bit microprocessor, the Arithmetic Control Unit of TOSBAC 40L (Fig.5.), was fabricated.

The typical cycle time of 270 ns is obtained by the new technology, while that of the coplanar sample is 300 ns. The comparable device yield is also achived.

The authors wish to thank International Plasma Corporation for etching the samples.

- (1) R.L. Bersin and R.F. Reichelderfer, Solid State Technol., 78, April 1977.

- (2) E. Bassous, H.N. Yu and V. Maniscalo, J. Electrochem. Soc. 123,1729(1976)

- (3) K. Yoshida, I. Yamazaki, K. Doi, S. Horiuchiand T. Shibata, IEEE J.

Solid-State Circuit, SC-11, 696(1976)

Photo resist

Fig.2. I-V characteristics; the coplanar technology(left), the new technology (right). W/L=  $4\,\mu/50\,\mu$  in the mask.

(C)

Fig.1. Fabrication process of the new technology.

D-mode transistor threshold voltage (Volt)

Fig. 3. Propagation delay times of 25 stage E/D ring oscillator.

Fig.5. Microphotograph of the Arithmetic Control Unit of TOSBAC 40L.

Fig. 4. Boron dose dependence of field inversion voltage.