Digest of Tech. Papers The 11th Conf. (1979 International) on Solid State Devices, Tokyo

A - 4 - 2

A High Speed Schottky 4k-bit PROM using Diffused Eutectic Aluminum Process (Deap) Toshitaka Fukushima and Koji Ueno IC Division, Fujitsu Lid. 1015 Kamikodanaka, Nakahara-ku, Kawasaki, Japan

Althouth fuse-blown type PROMs are widely used, potential advantages of passive isolation have not fully shown up with these devices. Namely, their cell size, for example, is still large because dominant area is used for fuses on the surface.

This report will describe a high speed 4096 bit bipolar shorted-junction type schottky TTL PROM, which is, instead, successfully fabricated by the use of passive isolation techniques named "Shallow V Groove" (SVG) and "Isolation by Oxide and Polysilicon" (IOP). These two techniques resulted in drastic improvement especially in both of cell size and speed by the factor of 1/2 and 2, respectively, as compared to those of our current gold doped device.

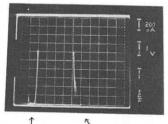

Programming of this shorted-junction type device is based on the "Deap" thechnique. By application of reverse current to the cell, temperature increases at the junction. When the temperature reaches to a certain point, then, aluminum-silicon eutectic is formed and it diffuses from the surface of emitter to base region resulting in short of the junction. This technology is named "Diffused Eutectic Aluminum Process" (Deap). Once eutectic forms bridge over the junction, the power dissipation there drops down (see Fig.1) and temperature decreases rapidly. This quenching effect stops further diffusion of eutectic and remains base-collector junction undestroyed.

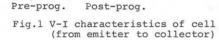

The SVG and the IOP are formed by using an anisotropic etch in (100) orientation silicon. Depth of the groove is a exclusive function of width of the etching window on the surface. The width of the SVG is designed so that bottom of the groove reaches top part of  $n^+$  buried layer. And that of the IOP is arranged so that the groove separates each island (see Fig.2)

For Deap PROM, a cell is a minimum size open-base npn transistor. Therefore it is essentially smaller in size than a cell of fuse-blown type devices. In addition, the SVG technique prevents both side-diffusion of p-type base and its depletion layer spread to eliminate mainly parasitic effect between cells in a same island (in the same word line). Because of these this technology realized a small cell size of 14 x 26  $\text{um}^2$  (0.564 mil<sup>2</sup>), which is 42.1% of that of the current device (see Fig.3).

The IOP also contributes to achieve higher packing densities and smaller

-75-

chip size. To isolate a 3 um thick epitaxial layer passively, the IOP has more advantages than other technology such as Isoplanar, because the depth of isolation is determined by width of etching window, and the groove is chemically etched at the same process steps with the SVG.

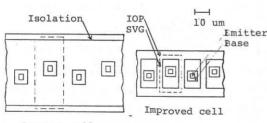

After all, even with conventional mask design rules, the 4096 bit Deap PROM is built in a size 3.3 x 3.1 mm<sup>2</sup> chip (see Fig.4). This figure is only 7.5% increase in size from current 2048 bit device (3.4 x 2.8), and 77.3% of that of 4096 bit (4.9 x 2.7).

The memory organization is 1024 words by 4 bits. Access time obtained by schottky TTL circuitry is 25 nsec (see Fig.5), which is 1.8 times faster than current 4096 bit device. Power supply current is 90 mA. Required energy of programming pulse is proportional to cell size and it is reduced to 120 mA x 20 v x 10 usec, which is 57.1% of current one.

Al Doped poly-Si Emitter Poly-Si Si0, Base p-sub.

Fig.2 Cross section of SVG and IOP

Current cell

Pre-prog.

Fig.3 Surface view of cell

Fig.4 Photomicrograph of chip surface

Input output Fig.5 AC characteristics