Digest of Tech. Papers The 11th Conf. (1979 International) on Solid State Devices, Tokyo  $\mathrm{C-\!\!\!-2-5}$  Current Injection Logic Gate with Four Josephson Junctions

> Susumu TAKADA, Shin KOSAKA, and Hisao HAYAKAWA Electrotechnical Laboratory 5-4-1 Mukodai-Machi, Tanashi, Tokyo 188, Japan

Josephson quantum interferometer devices are potential elements for high performance computers because of their fast switching speed and very low power dissipation<sup>1)</sup>. Recently, a Josephson interferometer logic device which is gated by an injection current, instead of a magnetic field of the control line, has been reported<sup>2)</sup>. This current injection logic device is very attractive for logic elements because it has higher gain and wider operating margin.

In this paper, we report a novel current injection logic device in which four Josephson junctions are directly coupled each other. In this device, inductances do not dominantly act on switching of the gate since switching is essentially determined by a phase balance between individual Josephson junctions, which allows us to choose the loop inductance as small as possible. This feature of the present device has the possibility to realize faster switching speed and smaller device size since the time delay and the space of the inductance can be eliminated<sup>3</sup>).

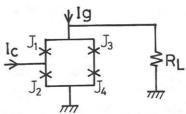

The four-junction switching gate is schematically shown in Fig. 1. As shown in the figure, the control current is injected into the device at the intermediate point between  $J_1$  and  ${\rm J}_{2}$  and the gate current is biased at the symmetric feed point in the loop. In this configuration, the switching threshold can be calculated by using the Josephson phase-current relationship, i.e.,

| $I_1^0 \sin\theta_1 + I_c = I_2^0 \sin\theta_2$               | , | (1) |

|---------------------------------------------------------------|---|-----|

| $I_{g} = I_{1}^{0} \sin\theta_{1} + I_{3}^{0} \sin\theta_{3}$ | , | (2) |

| $I_3^0 \sin\theta_3 = I_4^0 \sin\theta_4$                     | , | (3) |

| $\theta_1 + \theta_2 = \theta_2 + \theta_1$                   | , | (4) |

and

where  $I_1^0$  and  $\theta_1$  are the critical current and the phase of ith junction, respectively. The calculated threshold curve in the  $I_{g}-I_{c}$  plane is shown in Fig. 2. In this calculation, we assume all of the junctions have the same critical current, i.e.,  $I_1^0 = I_2^0 = I_3^0 = I_4^0 = 2$  mA. Switching operation can be performed by using the regions where both  ${\rm I}_{\rm g}$  and  ${\rm I}_{\rm c}$  have the same polarity. In

these regions the slope of the threshold curve is greater than unity, which means that the gain of the gate becomes higher than the conventional Josephson tunneling logic gate.

Fig.1. Four-junction switching device.

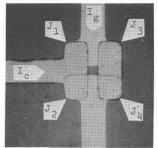

Experimental devices were fabricated with Pb-In alloy by using rf sputter-oxidation technique. Figure 3 shows a photograph of the experimental gate. Each junction size was 20 µm x 20 µm.

The switching threshold curve was measured by using pulses for driving  $I_g$  and  $I_c$ , and results are plotted in Fig. 4. As shown in the figure, the measured threshold curve is in good agreement with the calculated one shown in Fig. 2. We have found that there are several modes when the gate switches into the voltage state. In relatively large  $\mathrm{I}_{\sigma}$  regions, the gate generates the voltage equal to  $2V_{\sigma}(V_{\sigma}; \text{the gap voltage})$  when the gate switches. The threshold of this mode is marked by 'o' on the threshold curve in Fig. 4. Decreasing  $I_{g}$ , the gate begins to generate the gap voltage  $V_{g}$  in the transition(the threshold of this mode is marked by '•'). Interesting features appear in the regions marked by  $' \nabla'$ . In these regions, only  ${\bf J}_{1}$  and  ${\bf J}_{2}$  switch to the voltage state and generate

Fig.3. Photograph of switching device.

Fig.4. Measured threshold curve.

voltages with opposite polarities each other, so that the gate remains in the zerovoltage state. These behavior can be systematically explained by a dynamic analysis of the gate.

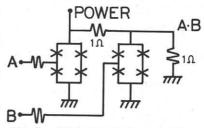

Employing this switching gate, a family of logic functions such as AND,OR, and INVERT can be easily achieved. Figure 5 shows an experimental AND logic gate con-

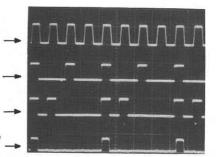

sisting of two switching gates. The result of the experimental operation of the AND gate is shown in Fig. 6. In this preliminary experiment, the gate is operated with a clock cycle of 1 kHz. As shown in Fig. 6, the operation of AND function is consistently performed.

In conclusion, we have proposed a novel Josephson switching gate controlled by current injection and measured switching POWER threshold characteristics which are in good agreement with the calculation. We have also demonstrated the AND gate successfully B using these switching gates.

OUTPUT 1)H.H. Zappe, Appl. Phys. Lett. 27, 432(1975). (A•B) 2)T.R. Gheewala,Appl.Phys.Lett.<u>33</u>,781(1978). 3)T.Yamashita et al.,J.Appl.Phys.(to be published).

Fig.5. AND gate test circuit.

Fig.6. Experimental operation of the AND gate.