## Digest of Tech. Papers The 12th Conf. on Solid State Devices, Tokyo

## B-3-3 P-Column Gate Field Effect Transistor

K. Asai, Y. Ishi-i, Y. Kawasaki and K. Kurumada Musashino Electrical Communication Lab., NTT Public Corporation

3-9-11 Midori-cho, Musashino-shi, Tokyo 180, Japan

A new structure for a GaAs J-FET (P-Column Gate FET) is proposed, employing p-type column shaped gates in an active n-layer on a semi-insulating substrate where the current flows through channel spaces between the gate columns with results of 17 mS of g<sub>m</sub> for prototype.

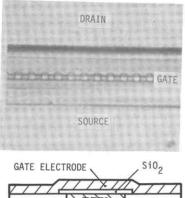

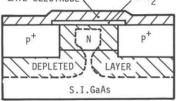

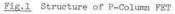

Figure 1 shows a microphotograph of and cross-sectional view of proposed P-Column FET. The channel is mainly controlled by depletion layers extending laterally from the columns at both sides of each channel and the columns completely reach the semi-insulating i-layer. It should be noted that the channel can be confined within n-layer near the n-i interface because of junction contour curves inward since the n-dopants decrease towards the i-layer. Moreover, MIS structure at the gate electrode metal on insulator/n-layer enables additional gate action. The gate pinch off voltage is predominantly determined by column sidewall distances and is controll-able with lithography independently on n-layer thickness. Be ion implantation<sup>(1)</sup>was carried out through the lithography resist with windows corresponding to the P-Columns to be formed. The typical parameters are as follows.

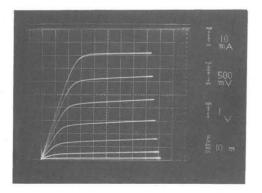

Energy: 100 keV, Dose:  $5 \times 10^{14}$  cm<sup>-2</sup>, Projected Range: 0.28 µm, Lateral Spreading of Be: 0.87 µm, Annealing Temp./Time: 600 °C/20 min., N-layer Thickness/Density: 0.18 µm/2.8×10<sup>17</sup> cm<sup>-3</sup>. Figure 2 shows an example of I-V curves for FET fabricated with 2 µm window size which results in ~3.7 µm P-Column diameter due to the lateral stretch of the implanted Be by 100 keV. No hysterisis on I-V was observed despite of the buffer-less n-layer on bulk i-substrate, presumably due to the channel confinement mentioned above. For 100 µm of equivalent gate width (n-channel number×n-layer thickness×2), was obtained 17 mS of transconductance being higher than in case of ordinary MESFETs with the same 100 µm gate width. Gate action in P-Column FET is made by two kinds of depletion swing, i.e. one at the column side walls and the other at the MIS surface structure. The MIS partition on g<sub>m</sub> has linear dependence on n-surface length along the column lines but the column side wall partition on g<sub>m</sub> has none on that length. Thus Fig.3 implies g<sub>m</sub> is sustained by combination of the above both partition, disclosing a merit of P-Column structure.

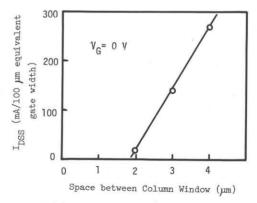

Column spaces vs I<sub>DSS</sub> (per 100 µm equivalent gate width) is plotted in Fig.4, where horizontal axis is the interspaces between 2 µm column windows. Linearity shown here between the interspace and I<sub>DSS</sub> verifies that photolithographic controll of the interspaces between the columns can determine the pinch off voltage regardless of n-layer thickness, namely normally-off FETs for logic is easily realized by the column structure without n-layer thickness controll.

Estimated  $f_{\rm T}(=g_{\rm m}/2\pi C_{\rm GS})$  from measured  $g_{\rm m}$  and  $C_{\rm GS}$  is about 3 GHz for the column diameter of 3.7 µm fabricated as the first trial. Assuming  $g_{\rm m} \propto (\text{column diameter})^{-1}$  and  $C_{\rm GS} \propto (\text{column diameter})$ ,  $f_{\rm m}$  is improved to about 30 GHz by realizable column diameter of about 1 µm which is possi-

- 75 -

ble by less lateral stretch of Be with lower energy (e.g. 30 keV) implantation and 0.5  $\mu$ m column window size of resist utilizing electron beam lithography.

Acknowledgements: This work has been made through incorporation with Y. Honda, S. Nojima, K. Shimada and Y. Imai, and by encouragements and discussion with Prof. J. Nishizawa, Drs. M. Watanabe, M. Fujimoto and M. Ohmori. Reference (1) S. Nojima, JJAP, <u>18</u>, pp.1079, 1979.

(a) Plan View: Distance between source and drain is 8 µm. Column window size and the interval are 2 µm both.

(b) Cross-sectional View: P-type regions laterally spread from the window of mask by about 0.87  $\mu m.$  Broken line is depletion edge at P-N junction and also by surface MIS effect.

Space between Column Window (µm)