Extended Abstracts of the 16th (1984 International) Conference on Solid State Devices and Materials, Kobe, 1984, pp. 15-18

# Invited

### **Refractory Metals and Silicides for Si MOS VLSI's**

# S. Iwata

Central Research Lab., Hitachi, Ltd.

Kokubunji, Tokyo

Various properties of refractory metals and their silicides are first compared. Then, some of the problems encountered when using metals like Mo and W are discussed. The stability of metal/SiO<sub>2</sub>/Si at high temperatures is compared for these metals, showing W to be superior to Mo as a gate metal. It is also shown that mobile ion contamination can be made extremely low in vacuum-melted sputter targets of these metals, making these refractory metals very attractive for VLSI use.

### I. Introduction

With the increase in the integration density of LSI's, refractory metal silicides are beginning to be used in place of poly Si for MOS gates and interconnects. This is due to the increase in the RC delay, if poly Si, which has low electrical conductivity, is to be used. Furthermore, in the near future when VLSI's of megabit level appears, it is expected that pure refractory metals, with higher conductivity, will be used, replacing poly Si and metal silicides.

In this paper, various properties of these metals and their silicides will first be compared as materials for VLSI applications. Then, some of the problems encountered when using such metals as Mo and W will be discussed.

#### II. Materials for future VLSI's

Many requirements must be satisfied if a material is to be used as MOS gates and interconnects. Among the properties to be considered are electrical conductivity, heat resistance, adhesion to  $\operatorname{SiC}_2$ , oxidation resistance, gate material/ $\operatorname{SiO}_2$ /Si stability, and low impurity content. A comparison of some of these properties for refractory metals, their silicides, and poly Si is shown in Table 1.

At present, silicides/poly Si("polycide")/Si0<sub>2</sub> Si MOS structures using such silicides as MoSi<sub>2</sub>, WSi<sub>2</sub>, etc. are being considered or used for MOS VLSI's.<sup>1)-3)</sup>The sheet resistance for these polycides is  $1-10 \Omega/\Box$ . However, it is considered imperative that silicides without poly Si underneath or refractory metals will be used for megabit-level VLSI's.<sup>4</sup> Some of the problems associated with using these metals will next be discussed, since their eventual use is inevitable, there are many problems for these metals, and many studies have already been reported on silicides.<sup>1)-3)</sup>

## III. Problems for refractory metals

The sheet resistance well below  $l \Omega/\mu$  is possible if such metals as Mo and W are used.<sup>5)-7)</sup> However, there are man<sub>y</sub> problems to be solved before they can be used. Although these metals have high conductivity and high melting point,

| Table | 1 | Comparison | of | materials | for | VLSI |

|-------|---|------------|----|-----------|-----|------|

|-------|---|------------|----|-----------|-----|------|

| material                                   | silicon       | polycide                                          | silícide                                                             | pure metal      |                         |

|--------------------------------------------|---------------|---------------------------------------------------|----------------------------------------------------------------------|-----------------|-------------------------|

| examples                                   | poly Si       | MoSi2/polySi<br>TaSi2/polySi<br>WSi2/polySi, etc. | MoSi <sub>2</sub> ,<br>TaSi <sub>2</sub> ,<br>WSi <sub>2</sub> ,etc. | Мо              | w                       |

| electrical<br>resistance<br>(Ω/□)          | poor<br>(~30) | fair<br>(1-10)                                    | fair<br>(1- 10 )                                                     | good<br>( < 1 ) | good<br>( < 1 )         |

| adhesion<br>to SiO <sub>2</sub>            | good          | good                                              | good                                                                 | fair<br>~good   | good<br>(sputtered<br>W |

| material/SiO <sub>z</sub> /Si<br>stability | good          | good                                              | fair<br>~good                                                        | fair<br>~ good  | good                    |

| oxidation<br>resistance                    | good          | fair<br>~good                                     | fair                                                                 | poor            | poor                    |

i) they cannot withstand high-temperature oxidizing ambients, ii) they cannot be used as mask against ion channeling during ion implantation for a self-aligned gate process, and iii) many studies regarding reliability are still required.

A number of studies have been reported on the solution of the first two problems.<sup>6),7)</sup> In all these studies, sputtered Mo or W is used, because of the fairly good adhesion to  $\text{SiO}_2$  obtained by sputtering. Oxidation of these metals can be prevented if annealing is carried out in an inert or reducing ambient. However, Si cannot be oxidized in this ambient, as is done in the conventional Si process. A new heat treatment using a  $H_2/H_2O$  ambient makes this Si oxidation possible without oxidizing these metals.<sup>7)</sup> Ion channeling during ion implantation can be prevented by forming a layer of PSG or WO<sub>x</sub> on W<sup>7</sup>, or by nitriding Mo.

The problems connected with reliability, namely, the stability of the metal/SiO<sub>2</sub>/Si structure will now be considered.

(1) High-temperature stability of metal/Si0 $_{

m o}/Si$

As gate oxides become thinner, the stability of metal/SiO<sub>2</sub>/Si becomes extremely important, since any reaction involving the metal,  $SiO_2$ , and Si may result in the degradation of MOS characteristics. Accordingly, the stabilities of Mo/ and W/SiO<sub>2</sub>/Si were compared as follows:

First, these two structures were annealed at 500-1100°C, and their surfaces were examined by ESCA. The analysis indicated the presence of Si on the surface of Mo/SiO<sub>2</sub>/Si after annealing in N<sub>2</sub> at 1100°C (1000°C in H<sub>2</sub>), whereas no Si was detected on the surface of W/SiO<sub>2</sub>/Si.

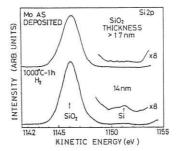

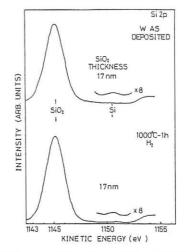

Secondly, surface analysis of  $\mathrm{SiO}_2$ , after chemically removing the metals, showed the  $\mathrm{SiO}_2$ thickness to be decreased for  $\mathrm{Mo/SiO}_2/\mathrm{Si}$  after annealing at 1000°C in H<sub>2</sub>, whereas no such changes were observed for  $\mathrm{W/SiO}_2/\mathrm{Si}$ , as shown in Figs. 1 and 2. This thickness was obtained from the intensity ratio of oxidized and unoxidized Si peaks (by ESCA). This thickness decrease is believed to be due to localized reduction of SiO<sub>2</sub>, rather than a uniform decrease in the SiO<sub>2</sub> thickness.

Corresponding to these results, the breakdown

Fig.l Si2p spectra for Si0<sub>2</sub> surface in Mo/Si0<sub>2</sub>/Si

Fig.2 Si2p spectra for Si0<sub>2</sub> surface in  $W/Si0_2/Si$  voltage of the  $W/Si0_2(20 \text{ nm thick})/Si$  structure was found to be about 6 V, as compared with 1 V for the  $Mo/Si0_2/Si$  structure, after annealing at  $1000^{\circ}$ C for 1 h in H<sub>2</sub>. These results and the fact that adhesion to Si0<sub>2</sub> was better for W than for  $Mo^{7)}$  show W to be more suitable for a gate metal than Mo.

(2) Mechanism of metal/SiO2/Si reaction

It was first thought that the above results were due to metal/SiO<sub>2</sub> reactivity. However, this conclusion became doubtful when the following points became clear:

i) Si, found on the surface of  $Mo/SiO_2/Si$ , was all oxidized Si, even if annealing was done in vacuum ( $1x10^{-5}Pa$ ), where Si is usually not much oxidized.

ii)  $\text{SiO}_2$  could be reduced to Si in  $\text{H}_2$  if  $\text{H}_20$  content was less than a few ppm. This reduction became less if there was Mo on the  $\text{SiO}_2$ , and less so if the metal on the  $\text{SiO}_2$  was W.

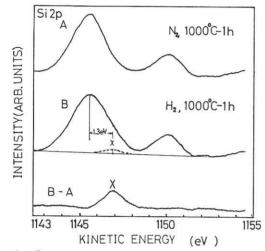

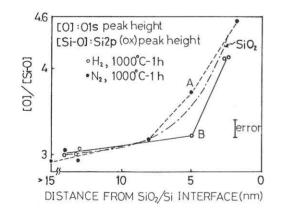

iii) When any instability of the  $Mo/SiO_2/Si$ structure was observed, more changes were found inside the  $SiO_2$  nearer to the  $SiO_2/Si$  interface than at the  $Mo/SiO_2$  interface Fig. 3 shows the difference in the Si2p ESCA spectra at a distance of 5 nm from the Si0<sub>2</sub>/Si interface after annealing in H<sub>2</sub> and in N<sub>2</sub>. For Mo/Si0<sub>2</sub>/Si annealed in H<sub>2</sub>, the Si0<sub>2</sub> was found to be partially reduced to Si0<sub>x</sub> (x<2), indicating Mo/Si0<sub>2</sub>/Si to be less stable in H<sub>2</sub> than in N<sub>2</sub>. This is supported by the result shown in Fig. 4, which indicates that, after annealing in H<sub>2</sub>, the O-to-Si ratio in the oxide becomes less than that for Si0<sub>2</sub> as the Si0<sub>2</sub>/Si interface is approached.

Fig.3 Comparison of Si2p spectra for Si0<sub>2</sub>(5 nm from Si0<sub>2</sub>/Si interface;see Fig.4) after annealing in N<sub>2</sub> and H<sub>2</sub>

Fig.4 Depth profile of Ols/Si2p(oxidized) ESCA peak ratio inside Si0<sub>2</sub> in Mo/Si0<sub>2</sub>/Si

iv)  $MoO_x$  or  $WO_x$  is found at the metal/  $SiO_2$  interface after deposition.<sup>7)</sup> This  $MoO_x$  can be partly reduced to Mo if annealed in H<sub>2</sub> at 1000°C for 1 h, but the  $WO_x$  cannot be reduced by this annealing. This oxide possibly has an influence on the stability of the metal/SiO<sub>2</sub>/Si structure. v) Thermodynamic data show that both Mo and W

are not reactive with  $\operatorname{SiO}_2^{8}$ , as also expected from the study of Pretorius et al.<sup>9</sup>) They also show that a reaction between  $\operatorname{SiO}_2$  and Si to form SiO, or that between  $\operatorname{SiO}_2$  and H<sub>2</sub> may occur at around  $1000^{\circ} \text{ C.}^{8}$

These data suggest that a reaction between  ${\rm SiO}_2$  and Si to form SiO (or  ${\rm SiO}_{\rm X}$ ) or that between  ${\rm SiO}_2$  and H<sub>2</sub> may be more important than a metal/  ${\rm SiO}_2$  reaction. Furthermore, metal oxides, present at metal/SiO<sub>2</sub> interfaces, are considered to provide an oxidizing "atmosphere" for the various reactions which may occur in the metal/SiO<sub>2</sub>/Si structure, making SiO<sub>2</sub> more stable by their presence.

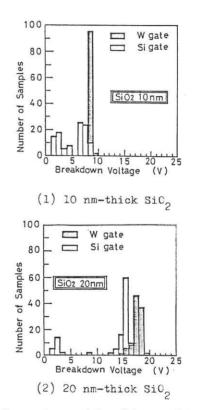

Fig.5 Comparison of breakdown voltages for W- and Si-gate MOS

Finally, the breakdown voltages are compared for W\* and Si gate MOS diodes with 10 or 20 nmthick  $\text{SiO}_2$  in Fig. 5. The figure shows the superiority of W as a gate material for use in VLSI's with thin  $\text{SiO}_2$ .

\* annealing done in  $N_2$  with a few ppm of  $O_2$

(3) Mobile ion contamination in metal/SiO<sub>2</sub>/Si

Mobile ion contamination must be kept low if a metal is to be used as a gate material. It is reported by Amazawa et al.<sup>10)</sup>that Na and U contents as low as 30 and 5 ppb, respectively, are realized in a vacuum-melted sputter target supplied by Nippon Mining Co.

Low Na and U contents can also be achieved for W (also by the same company). The results of chemical analysis for this W target is shown in Table 2, together with those for a commercially available conventional target. The table also

Table 2 Comparison of conventional and highpurity W targets

|              | i             | mpuriti | △V <sub>fb</sub> (V)* |                     |  |

|--------------|---------------|---------|-----------------------|---------------------|--|

| target       | Na            | к       | U                     | 3 MV/cm-200°C-30mir |  |

| conventional | 10-100        |         | 0.1                   | 0.5~2               |  |

| high-purity  | 0.01<br>~0.02 | <0.05   | 0.005                 | 0                   |  |

+ no PSG on W; error ± 0.02 V

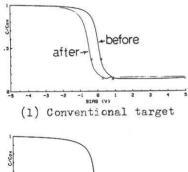

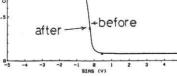

shows the change in the flat-band voltage  $\Delta V_{fb}$ after a BT (bias-temperature) test for MOS diodes with W sputtered from these targets. Fig. 6 shows the C-V (capacitance-voltage) curves before and after a BT (3 MV/cm-200°C-30 min) stress for the conventional and high-purity targets.  $\Delta V_{fb}$  for the MOS diodes fabricated using the latter was 0 V, compared with 0.5 V for the former.

(2) High-purity target

#### III. Conclusions

Various properties of refractory metals and their silicides for VLSI applications were discussed with emphasis on the stability of gate material/SiO<sub>2</sub>/Si in regard to high-temperature annealing and mobile ion contamination. It was shown that  $W/SiO_2/Si$  was more stable than Mo/ SiO<sub>2</sub>/Si during this annealing. Regarding mobile ion contamination, such impurities as Na in Mo or W can be made as low as 30 ppb or less, so that no shifts in V<sub>fb</sub> are observed after a BT test.

#### References

- M. Ishihara, T. Matsumoto, S. Shimizu, K. Mitsusada, and K. Shimohigashi, IEEE Int'l Solid-State Circuits Conf. Dig. Papers, p.74, Feb. 1982.

- B. L. Crowder and S. Zirinsky, IEEE Trans. Electron Devices, vol. ED-26, p.369, 1979.

- F. Mohammedi, K. C. Saraswat, and J. D. Meindl, Appl. Phys. Lett., vol. 35, p. 529, 1979.

- K. Tsuda, Nikkei Electronics, p.127, Feb.27, 1984.

- 5) D. Brown and R. J. Connery, IEEE Trans. Electron Devices, vol.ED-25, p.1302, 1978.

- 6) M. Kondo, T. Mano, H. Yanagawa, H. Kikuchi, and T. Amazawa, IEEE Solid-State Circuits Conf. Dig. Fapers, vol.21, p.148, 1978.

- 7) S. Iwata, N. Yamamoto, N. Kobayashi, T. Terada, and T. Mizutani, IEEE Trans. Electron Devices, vol.ED-31, Sept. 1984.

- Kubaschewski and C. B. Alcock, Metallurgical Thermochemistry(5th Ed.), Pergamon Press, Oxford, 1979, pp.378-384.

- R. Pretorius, J. M. Harris, and M-A. Nicolet, Solid-State Electronics, vol.21, p.667, 1978.

- 10)T.Amazawa, H. Oikawa, and H. Homma, Abstracts for Fall Meeting, Japan Appl. Phys. Soc., p.407, 1983.