Extended Abstracts of the 16th (1984 International) Conference on Solid State Devices and Materials, Kobe, 1984, pp. 359-362

# Invited

## **HEMT LSI Circuits**

M. Abe, T. Mimura, K. Nishiuchi, A. Shibatomi and M. Kobayashi Fujitsu Laboratories Ltd., Fujitsu Limited 1677, Ono, Atsugi 243-01, Japan

Self-aligned High Electron Mobility Transistor (HEMT) technology based on selectively doped GaAs/AlGaAs heterojunction structure for LSI circuits is described. Internal logic delay of 22 ps per gate at 77K was achieved at a fan-out of about 2, roughly three times faster than that of GaAs MESFET technology. HEMT 1Kb and 4Kb sRAM circuits have been successfully developed. HEMT 1Kb sRAM demonstrated address access time of 0.87 ns with power dissipation of 360 mW at 77K. Projected performance of HEMT 4Kb sRAM is sub-ns address access time using 1  $\mu$ m gate device and 2  $\mu$ m line process technology.

I. Introduction

The information processing in 1990 will need ultra-high-speed computers, requiring high speed LSI circuits with logic delays of sub-100 ps.1,2)

High Electron Mobility Transistor (HEMT) technology has opened the door on new possibilities for ultra-high-speed LSI/VLSI applications.<sup>3-6</sup>) Due to the super-mobility GaAs/AlGaAs heterojurction structure, HEMT is especially attractive for low temperature operations at liquid nitrogen temperature. In 1981, a HEMT ring oscillator with the gate length of 1.7  $\mu$ m demonstrated 17.1 ps switching delay with 0.96 mW power dissipation per gate at 77K, indicating that switching delay below 10 ps will be achievable with 1  $\mu$ m gate devices.<sup>4</sup>) Switching delay of 12.2 ps with 1.1 mW power dissipation per gate has already been obtained with 1  $\mu$ m-gate HEMT at room temperature.<sup>7</sup>)

This paper presents the recent advances in HEMT technology for high performance LSI circuits, i.e., self-alignment fabrication technology, HEMT performances, logic and memory LSI circuits.

II. Self-Alignment Fabrication Technology

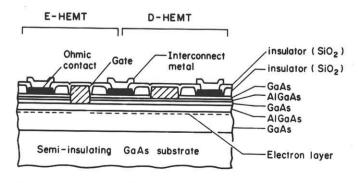

Figure 1 is a cross-sectional view of a typical self-aligned structure of enhancement-mode (E) and depletion-mode (D) HEMTs forming an inverter for DCFL circuit configuration. The basic epilayer structure consists of a 600 nm undoped GaAs layer, a 30 nm  $Al_{0.3}Ga_{0.7}As$  layer doped to 2 x 10<sup>18</sup> cm<sup>-3</sup>

with Si, and a 70 nm GaAs top layer successively grown on a semi-insulating substrate by MBE. The low field electron mobility was found from Hall measurements to be 7200 cm<sup>2</sup>/V.s at 300K and  $38000 \text{ cm}^2/V.s$  at 77K. The concentration of two Dimensional Electron Gas (2DEG) was 1.0 x 10<sup>12</sup> cm<sup>-2</sup> at 300K and 8.4 x 10<sup>11</sup> cm<sup>-2</sup> at 77K. A thin A1<sub>0.3</sub>Ga<sub>0.7</sub>As layer to act as a stopper against selective dry etching is embedded in the top GaAs layer to fabricate E-and D-HEMTs in the same wafer. By adopting this new device structure, we can apply the selective dry etching of GaAs to AlGaAs to achieve precise control of the gate recessing process for E- and D-HEMTs.

The fabrication of E/D-HEMT circuits starts with etching shallow mesa islands down to the undoped GaAs layer to localize the active region. Next the source and drain for E- and D-HEMTs are metallized with AuGe/Au eutectic alloy to

Fig. 1 Cross-sectional view of the self-aligned structure of E/D-HEMTs forming an inverter for DCFL circuit configuration.

form ohmic contact with the 2DEG. Then selective dry etching using an etching gas composed of  $CC1_2F_2$  and  $He^{8}$  is carried out to remove the GaAs top layer, exposing the top surface of the thin  $A1_{0.3}Ga_{0.7}As$  stopper. A significantly high selectivity ratio of more than 260 was achieved at a power density of 0.18 W/cm<sup>2</sup>, where the etching rate of GaAs was about 520 nm/min and that of AlGaAs was as low as 2 nm/min.

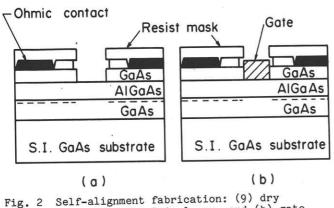

Figure 2 shows a step in self-aligned gate HEMT fabrication. Both the recessed structure to control the threshold voltage of the devices and the Schottky contact for the gate can be fabricated by using the same resist pattern, as shown in this figure. As a result, the Schottky gate contact and n-GaAs top layer for ohmic contact are self-aligned to achieve high speed performance.

### III. HEMT Device Performances

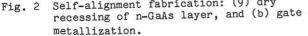

Figure 3 shows the gate length dependence of device characteristics. The values for  $V_{\mathrm{T}}$  and K were obtained by fitting the measured drain-current gate-voltage characteristics of the square root of drain-current versus gate-voltage relationship at Vds of 1 V. Dependence of K-factor and transconductance gm of E-HEMTs on gate length is measured at both 77K and 300K, and K is plotted in Fig. 3. Dashed line indicates  $L_g^{-1}$ -dependence of K-factor, estimated from the gradual channel approximation. Below 1 µm gate length at 300K,K-factor drops off from  $L_g^{-1}$ -dependence. Velocity saturation effect and parasitic source resistances probably play a significant role in these results. The 0.5 µm-gate E-HEMT at 77K exhibits gm of

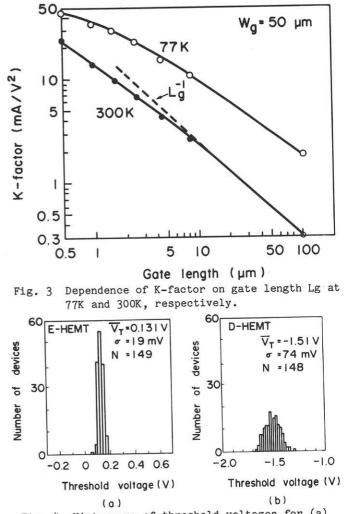

Fig. 4 Histograms of threshold voltages for (a) E-HEMTs and (b) D-HEMTs.

500 mS/mm, which is the highest value ever reported for any FET type device. No significant variation in threshold voltages with gate length was observed in the range from  $L_g = 10 \ \mu m$  to  $L_g = 0.5 \ \mu m$ . This indicates that reducing the geometry of HEMTs is an easily acceptable way to increase performance without causing problems regarding short channel effects.

Histograms of threshold uniformities for E- and D-HEMTs are shown in Fig. 4. The standard deviations in threshold voltages, measured for 149 E-HEMTs and 148 D-HEMTs distributed over an area of 15 mm x 30 mm, are 19 mV and 74 mV, respectively. The threshold sensitivity defined by the differential threshold voltage to the thickness of AlGaAs layer can be calculated based on the simple model, to be 70 mV/nm at  $V_T = 0.13$  V. As shown in Fig. 4(a), the deviation in the maximum to minimum threshold voltages for the E-HEMT is 140 mV. This corresponds to a

thickness deviation of only 2 nm over the wafer, indicating excellent controllability of MBE growth and the device fabrication process. The ratio of standard deviation of threshold voltage to the logic voltage swing (0.5 V for DCFL) is 3.8%. This strongly supports the viability of these technologies for realizing ICs with LSI/VLSI level complexities.

IV. Fundamental Logic and LSI Circuits

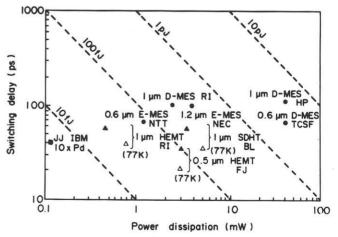

To evaluate the high speed capability of HEMTs in complex logic circuits, a single-clocked divide-by-two circuit based on the master-slave flip-flop consisting of eight DCFL NOR-gates, one inverter and four output buffers was fabricated. The circuit has a fan-out of up to 3 and 0.5 mm-long interconnects, giving a more meaningful indication of the overall performance of HEMT ICs than that obtained with a simple ring oscillator. The basic gate consists of 0.5 µm x 20 µm-gate E-HEMT and saturated resistors as loads. Divide-by-two operation is demonstrated at up to 8.9 GHz at 77K and up to 5.5 GHz at 300K.2) The values of 8.9 GHz and 5.5 GHz respectively correspond to internal logic delays per gate of 22 ps with power dissipation of 2.8 mW at 77K, and 36 ps with power dissipation of 2.9 mW at 300K, with an average fan-out of about 2. The speed-power performances of ring oscillators and frequency divider circuits are summarized in Tables I and II. Figure 5 compares switching delay and power dissipation of a variety of

#### Table I Ring oscillators speed-power performance for HEMT device approaches.

| Source         | (ref) | Approach |        | Gate<br>8i<br>( µm | length<br>width<br>xµm) |     | Switching<br>delay<br>(ps) | Speed-power<br>product<br>(fJ) | Fan-in<br>Fan-out |

|----------------|-------|----------|--------|--------------------|-------------------------|-----|----------------------------|--------------------------------|-------------------|

|                | (4)   | HEMT     | ( 77K) | 1.7                | x                       | 13  | 17                         | 16                             | 1/1               |

| Fujtsu         | (2)   | HEMT     | (300K) | 0.5                | x                       | 20  | 15                         | 18                             | 171               |

|                |       | HEMT     | (300K) | 0.5                | x                       | 20  | 25                         | 4                              | 171               |

| Thomson<br>CSF | (5)   | TEGFET   | (300K) | 0.7                | x                       | 20  | 18                         | 17                             | 171               |

| AT 8           | Tics  | SDHT     | ( 77K) | 1                  | x                       | 125 | 18                         | 141                            | 171               |

| Bell Lob. (6)  |       | SDHT     | (300K) | 1                  | x                       | 125 | 30                         | 135                            | 171               |

| Rockwell       | (7)   | HEMT     | (300K) | 1                  | x                       | 20  | 12                         | 14                             | 171               |

| Table II HE | MT frequency | divider | performance. |

|-------------|--------------|---------|--------------|

|-------------|--------------|---------|--------------|

| Source (ref)   | Device             | Circuit   | Max.freq. | Td   | Pd Td |

|----------------|--------------------|-----------|-----------|------|-------|

|                | approach           | approach  | (GHz)     | (ps) | (fj)  |

| Fujitsu (2)    | 0.5 µm HEMT ( 77K) | MS-FF,1/2 | 8.9       | 22   | 62    |

|                | (300K)             | (NOR)     | 5.5       | 36   | 104   |

| AT & T         | I µm SDHT (77K)    | D-FF, 1/2 | 5.9       | 34   | 170   |

| Bell Lab. (10) | (300K)             | (NOR)     | 3.7       | 54   | 173   |

| Rockwell (7)   | l µm HEMT (77K)    | D-FF, 1/4 | 5.2       | 38   | 30    |

|                | (300K)             | (NOR)     | 3.6       | 56   | 26    |

frequency dividers.<sup>2,7,10)</sup> The switching speed of HEMT is roughly three times as fast as that of GaAs MESFET.

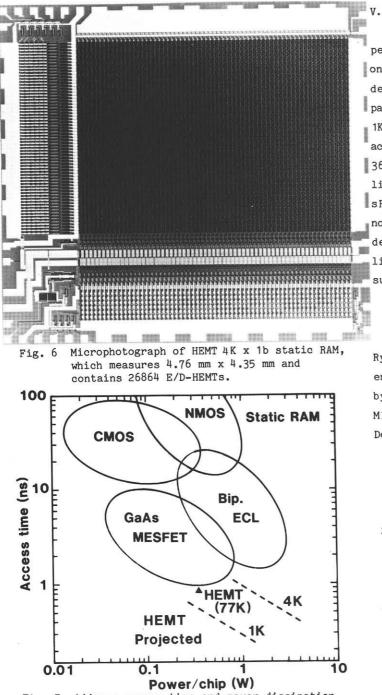

The HEMT 1K x 1b fully decoded static RAM has been successfully developed with E/D type DCFL circuit configuration.<sup>9)</sup> The memory cell is a 6-transistor cross-coupled flip-flop circuit with switching devices having gate lengths of 2.0 µm. For peripheral circuits, a 1.5 µm gate switching device was chosen. In order to obtain high-speed operation, sufficiently high operating current was assigned to peripheral circuits. As a result, peripheral circuits, with 15% of the total device count, dissipate 85% of the chip power. To obtain a good noise margin and guarantee stable logic operation in the HEMT DCFL circuit, which has a small logic swing, special attention was paid to the power supply. The RAM has a total device count of 7244. The design rule for these lines is 3 µm line width and spacing at minimum. Minimum size of the contact hole is 2 µm x 2 µm. The memory cell is 55 µm x 39 µm (2145 µm<sup>2</sup>), and the chip size is 3.0 mm x 2.9 mm. Normal read-write operation was confirmed both at 300K and 77K. At 300K, the row address access time was 3.4 ns and chip dissipation power P<sub>chip</sub> of 290 mW was obtained with a supply voltage  $\rm V_{dd}$  of 1.30 V. Sub-nanosecond access operation of access time of 0.87 ns with  $P_{chip}$  of 360 mW was achieved with  $V_{dd}$ of 1.60 V at 77K. With device parameters designed, HEMT 1Kb static RAMs will achieve sub-500 ps access operation with power dissipation of 1 W.

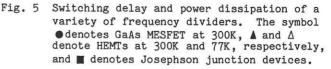

The HEMT 4K x 1b fully decoded static RAM has also been successfully fabricated using the technology described above, and tested. Figure 6 shows a microphotograph of the 4K x 1b sRAM. The memory cell is 55  $\mu$ m x 39  $\mu$ m, the chip is 4.76mm x 4.35 mm, and 26864 HEMTs are integrated in a 4K bit static RAM. Normal read-write operation was confirmed both at 300K and 77K. Figure 7 shows the address access time and power dissipation of sRAM. By using 1- $\mu$ m gate devices and 2- $\mu$ m design rule technology, subnanosecond address access time can be projected for the 4Kb sRAM.

#### Summary

Recent advances in HEMT technology for high performance LSI circuits are presented with focus on self alignment fabrication technology using new device structure, controllability in device parameters, logic and memory LSI circuits. A HEMT 1Kb sRAM has been developed to achieve address access time of 0.87 ns with power dissipation of 360 mW at 77K, using 1.5-µm gate devices and 3-µm line process. Under the same technology, HEMT 4Kb sRAM has also been successfully fabricated and normal read-write operation been confirmed. With device technology of 1-µm gate devices and 2-µm line process, HEMT 4Kb sRAM should achieve subnanosecond access operations.

#### ACKNOWLEDGMENT

The authors wish to thank Dr. T. Misugi, Dr. O. Ryuzan, Dr. M. Fukuta, and T. Kotani for encouragement and support. This work is supported by the Agency of Industrial Science and Technology, MITI of Japan in the frame of National Research and Development Project "Scientific Computing System".

#### REFERENCES

- M. Abe et al.: IEEE Trans. Electron Devices ED-29 (1982) 1088.

- M. Abe et al.: IEEE GaAs IC Symposium Tech. Digest (1983) 158.

- T. Mimura et al.: Japan. J. Appl. Phys., <u>19</u> (1980) L225.

- 4) T. Mimura et al.: Japan J. Appl. Phys., <u>20</u> (1981) L598.

- 5) P. N. Tung et al.: Electronics Lett., <u>18</u> (1982) 517.

- J. V. DiLorenzo et al.: Int. Electron Devices Meeting Tech. Digest (1982) 578.

- C.P. Lee et al.: IEEE GaAs IC Symposium Tech. Digest (1983) 162.

- K. Hikosaka et al.: Japan. J. Appl. Phys., <u>20</u> (1981) L847.

- 9) K. Nishiuchi et al.: ISSCC Digest Tech. Papers (1984) 48,314.

- 10) R. A. Kiehl et al.: IEEE Electron Device Lett., EDL-4 (1983) 377.