SOI / CMOS Gate Array by Laser Recrystallization

Tetsuo Izawa, Seiichiro Kawamura, Nobuo Sasaki, Motoo Nakano, Kunihiko Wada and Mitsumasa Ashida\*

IC Development Division and MOS Device Development Division\* Fujitsu Limited, Kawasaki 211

This paper describes 440-gate CMOS Gate Arrays fabricated by a laser recrystallized SOI (Silicon on Insulator) technology for the first time.

Recently, many investigations for SOI devices and techniques have been performed. Especially laser recrystallization is paid much attention as one of the most effective techniques for the realization of  $SOI/IC's^{1,2}$ . The realization of SOI/IC's is expected because of their characteristics of high speed and latch-up free etc. While some 3-D circuits as ring oscillators<sup>3</sup> and shift registers<sup>4</sup> have been fabricated as test devices, none has been called the integrated circuits indeed. It is difficult to make device-worthy silicon films on amorphous insulating layers with good reproducibility. Poor reproducibility causes poor yield of devices in a chip. However, by several improvements of annealing techniques and equipments, we can obtain bearable crystalline islands with good yield now. Then we succeeded in fabricating of SOI/IC's—440-gate SOI/CMOS Gate Arrays.

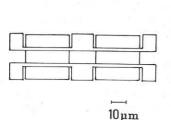

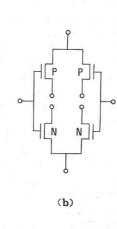

The Gate Array has 440 fundamental elements named Basic Cell (BC). A BC consists of two pairs of p-channel and n-channel MOSFET's with  $L = 2.8 \ \mu m$  and  $W = 30 \ \mu m$ . Fig.l shows a pattern and an equivalent circuit of a BC. The BC's are set in array of 55 rows and 8 columns. In periphery of the array of BC's, I/O cells are laid.

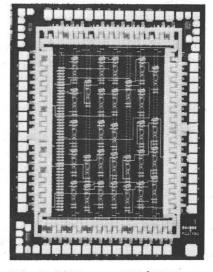

The fabrication process is as follows. A 0.4 µm thick layer of polysilicon over a thermally oxidized silicon film was recrystallized by using laser beam irradiation. We use some kinds of laser recrystallization techniques as the heat-sink method etc.<sup>5,6</sup>) During the recrystallization, the scanning cw argon ion laser beam was used with a power of 5-10 W. The silicon islands for p-channel and n-channel MOSFET's were doped by ion implantation with arsenic  $(2x10^{11}cm^{-2}, 80 \text{ keV})$  or boron  $(2x10^{11}cm^{-2}, 120 \text{ keV})$ , respectively. A 400 nm thick layer of gate oxide was grown by thermal oxidation. After the formation of polysilicon gate electrodes (0.4 µm thick), source and drain regions of MOSFET's were implanted with boron  $(1x10^{15}cm^{-2}, 35 \text{ keV})$  or arsenic  $(3x10^{15}cm^{-2}, 120 \text{ keV})$ . Then the wafers were annealed at 900°C nitrogen atmosphere for 40 minutes. Wiring was performed by using 2-level aluminum metallization technique. A finished sample is shown in Fig.2.

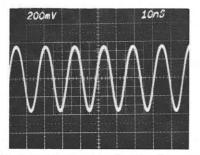

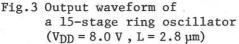

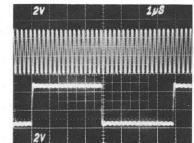

In this experiment, the circuits of ring oscillators (7-stage and 15-stage) and frequency dividers which have different stages (largest: 12-stage) were customized. Each stage of the frequency dividers consists of 10 BC's (i.e. 40 MOSFET's). Threfore, a 12-stage frequency divider has more than 480 MOSFET's, including I/O cells. Fig.3 and Fig.4 show output waveforms of a ring oscillator and a frequency divider, respectively. Fig.3 illustrates that the propagation delay time is 530 psec a stage at 8.0 V of power supply. This value is about 70% of that of a conventional Gate Array made on a single crystal silicon substrate. Threshold voltages are from -1.2 to -0.5 V for the

p-channel MOSFET's and from 0.5 to 1.2 V for the n-channel MOSFET's. Field effect mobilities are about 130  $\text{cm}^2 \cdot \text{V}^{-1} \cdot \text{sec}^{-1}$  for the p-channel MOSFET's and about 530  $\text{cm}^2 \cdot \text{V}^{-1} \cdot \text{sec}^{-1}$  for the n-channel ones. These values will be improved, as process conditions are improved.

By this attempt, we have good perspective of SOI technology application to IC's.

## REFERENCES

- 1) T.I.Kamins, IEEE IEDM Tech.Digest (San Francisco, 1982) 420(1982).

- 2) H.W.Lam, Proceedings to the CSSDM (Tokyo, 1983)12(1983).

- 3) N.Sasaki,S.Kawamura,T.Iwai,R.Mukai,M.Nakano and M.Takagi, the 15th Conf. Solid State Devices and Materials (Tokyo,1983) Late News A-3-7LN,Suppl.Extended Abstracts 24(1983).

- 4) S.Akiyama, S.Ogawa, M.Yamada, N.Yoshii and Y.Terui, IEEE IEDM Tech.Digest (Washington D.C., 1983) 352(1983).

- 5) S.Kawamura, N.Sasaki, M.Nakano and M.Takagi, J.Appl.Phys. <u>55</u> 1607 (1984).

- R.Mukai, N.Sasaki, T, Iwai, S.Kawamura and M.nakano, Appl. Phys.Lett. 44 994 (1984).

(a)

Fig.1 Basic Cell (a) Pattern (b) Equivalent Circuit

Fig.2 440-gate SOI/CMOS Gate Array

CLOCK (4MHz)

OUTPUT

Fig.4 Output waveform of a 5-stage frequency divider (Clock Frequency : 4 MHz, V<sub>DD</sub> = 5.0 V)