A New OEIC Fabrication Technique - Graded-Step Process - Applied to an AlGaAs/GaAs Monolithic Laser/FET

O. Wada, T. Sanada, H. Machida, S. Yamakoshi, H. Hamaguchi, T. Fujii, T. Horimatsu, and T. Sakurai

Fujitsu Limited, 1677, Ono, Atsugi 243-01, Japan

A new technique of fabricating optoelectronic integrated circuits (OEIC's) - Graded-Step Process - has been developed, in which problems in photolithography and interconnection processes previously caused by the existence of steep mesa steps on the substrate can be eliminated. This technique has been applied to integrate a low threshold current AlGaAs/GaAs quantumwell laser and GaAs FET drivers on a semi-insulating GaAs substrate, and a high sensitivity operation has been successfully demonstrated.

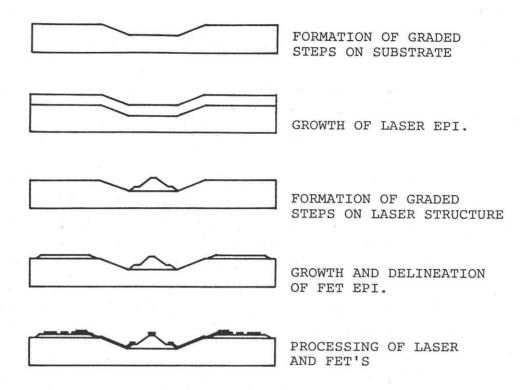

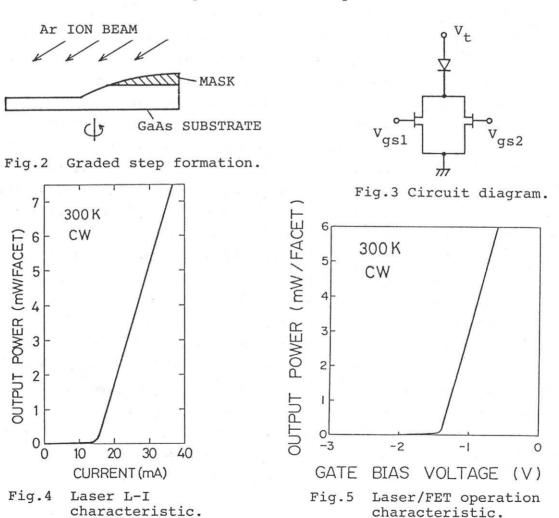

The present technique consists of key procedures as shown in Fig. 1. A channel having graded steps was first formed on the GaAs substrate by Ar ion-beam etching. A photoresist layer (AZ-4620) deformed at a high baking temperature (200°C) was used as a mask for etching as is illustrated in Fig. 2. Graded steps exhibiting a slope angle as small as 15 deg was generated even for a 9 µm channel depth. A quantum-well structure was then grown on the substrate by MBE, and a laser geometry was formed within the channel by applying the graded-step process. An FET epilayer was grown also by MBE and delineated similarly. Processing of the laser, FET's and interconnections resulted in a complete circuit as shown in Fig. 3.

The graded steps thus formed allow one to use conventional photolithographic technique with no additional tactics such as thickening the photoresist layer and therefore to realize an excellent yield in patterning fine geometries. A ridge-waveguide (3 µm wide and 300 µm long) laser and recessed-gate (2 µm long) FET's with the gate width of 680 µm were successfully formed in

the present circuit.

Figure 4 shows the light output versus current characteristic of the integrated laser. By the use of the GRIN-SCH single quantum-well (60 Å thick) structure, a low threshold current of 15 mA as well as a high differential quantum efficiency of greater than 60 % has been achieved. The performance of the circuit is shown in Fig. 6, in which the light output power is modulated by varying one of the gate input voltage (V<sub>S</sub>) with the other FET pinched-off. From this data a high sensitivity of 7.5 mW/V/facet has been determined, which owes to not only the high quantum efficiency of the laser but the high transconductance of the FET, both successfully realized by the present fabrication process.

both successfully realized by the present fabrication process.

The present research effort is part of a major research and development project on optical measurement and control systems, conducted under a program set up by the Ministry of International Trade and Industry's Agency of Industrial Science and Technology.

Fig.1 Fabrication procedure.

## A New InGaAsP/InP Heterobipolar Laser Transistor

Yoshihiro Mori, Jun Shibata, Yoichi Sasai, Nobuyasu Hase and Hiroyuki Serizawa Central Research Laboratory, Matsushita Electric Industrial Co., Ltd. Moriguchi, Osaka 570, Japan

Recently, optoelectronic integrated circuits (OEIC's) are actively studied<sup>1,2)</sup>. In order to realize a highly multi-functional OEIC, new devices with functions of light emission and electrical switching are desired to be realized. A double-heterobipolar transisitor (D-HBT), which consists of semiconductor compounds with direct energy gaps, is considered to be one of promissing devices for this purpose because of its capability of confining the photons in a layer<sup>3)</sup>. In this study, we have developed a new structure HBT which produces a stimulated emission from the base region. We report the fundamental characteristics of this device.

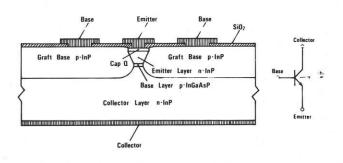

Figure 1 shows the schematic structure of the device. The wafer grown by LPE consists of four layers: n-InP (collector, 5µm), p-InGaAsP (base, active layer,  $\lambda g$ =1.3um, 0.2µm), n-InP (emitter, 4µm) and n<sup>+</sup>-InP (cap, 1µm). After a mesa structure was formed by chemical etching, the mesa was buried with p<sup>+</sup>-InP LPE layers. Au/Zn and Au/Sn were selectively deposited to give ohmic electrodes on p and n regions, respectively. This structure constructs a npn double-heterojunction bipolar transistor with p<sup>+</sup>-InP graft base layers.

When it operates in the saturation state of the transistor operation, holes are transversely injected into the p-quarternary base region from the graft base and a lot of electrons are vertically injected from the emitter into the collector through the base. Since the base region has a narrower band gap than that of InP, most of the holes and a part of the electrons are confined in the region and then recombine to generate photons. The photons are also confined in this region because the region has a higher refractive index than that of InP. Thus, laser oscillation occurs when the both types of carriers are injected sufficiently. In cut-off state, however, since holes are not injected, the collector current is very small and light emission does not occur.

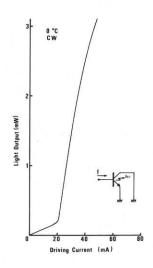

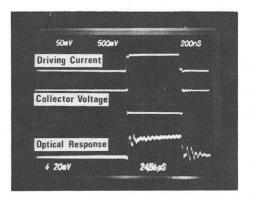

Figure 2 shows the current-voltage characteristics of the fabricated device. The  $h_{\overline{FE}}$  is higher than 300, and the collector resistance is less than  $10\Omega$ . Figure 3 shows the dependence of light output power on base current under no bias voltage. Laser operation was observed when the base current is larger than 20mA. The external differential quantum efficiency is found to be about 15 percent per facet. Figure 4 shows the response properties of the optical output and the collector voltage to the driving base current, here, the

collector was reversely biased through  $30\Omega$  series resistor.

In summary, we have demonstrated a new switching heterobipolar device - a laser transistor, which is able to control both optical emission and electrical current.

The authors wish to thank S. Horiuchi, T. Kajiwara and Y. Hori for their encouragements. The authors appreciate useful discussions with Prof. K. Iga, Tokyo Institute of Technology and Prof. M. Yamanishi, Hiroshima University.

## References

- 1) J. Shibata et al.: Ext. Abst. the 5th Int. Conf. Solid State Dev. Mat. (1984) C-2-2

- 2) H. Matsueda et al.: J. Lightwave Tech. LT-1, (1983) 368

- 3) Y. Arai et al.: IECE of Japan,

Tech. Rep. Group Electron. Device,

ED83-59 (1983) 17

100 mA

Fig.1. Schematic cross-sectional view of the new device and the equivalent circuit

Fig.2. Current-voltage characteristics

Fig.3. Light output vs. base current characteristic at no bias

Fig.4. Response characteristics of the collector voltage and the light output