# Effect of Grain Boundaries on the I-V Characteristics of P-Channel MOSFET/SOI

T.Nishimura, K.Sugahara, S.Kusunoki, and Y.Akasaka

LSI Research and Development Laboratory Mitsubishi Electric Corporation 4-1 Mizuhara Itami, 664, Japan

This paper reports on the effects of grain boundaries (GBs) on the electrical characteristics of p-channel MOSFETs fabricated in a silicon film on an insulating layer (SOI), for which the direction of GBs are precisely controlled by using the selective laser recrystallization technique.

For GB perpendicular to the current flow, the potential barrier height is measured from the temperature dependence of the device current. This explains the electrical characteristics induced by the presence of GB qualitatively in good agreement with the theoretical expectations. The trap density in GB interface is estimated to be  $1.9 \times 10^{-2}$ /cm<sup>2</sup>.

For GB parallel to the current flow, no remarkable effect is found on the I-V characteristics.

# 1. INTRODUCTION

Grain boundaries (GBs) in the channel region of MOSFETs fabricated in the silicon film on insulator (SOI) have remarkable influence on device characteristics. There have been several reports on the theoretical models of carrier transport and their experimental supports (1,2). However, since GBs were neither perfectly perpendicular nor parallel to the channel direction, and their number in the channel region was not controlled in the conventional laser recrystallized silicon film, experimental data has merely given the rough agreement to theoretical models (1).

In this paper we present the detailed evaluation of GB-effect on the p-channel MOSFET (PMOS) on SOI, which has not been reported yet, in which the direction of GB in the channel region was controlled by using the selective laser recrystallization technique (3,4).

# 2. SAMPLE PREPARATION

The starting material was 4-inch Si wafer with an 1.1 um thick thermally oxidized silicon dioxide  $(SiO_2)$  layer. A 0.5 um thick undoped polysilicon was deposited by LPCVD technique. Impurity doping was performed by phosphorus implantation. The 500 A thick LPCVD silicon nitride  $(Si_3N_4)$  was deposited on that material system, and patterned into parallel stripes of 5 um in width and 15 um in center-to-center spacing. The cw argon laser beam of 100 um diameter was rastered parallel to the stripes with a scanning speed and a trace-to-trace stepping of 25 cm/sec and 30 um, respectively. The substrate temperature was kept at 450 C during laser beam irradiation.

Due to the periodical antireflection effect of  $Si_3N_4$ , the given heat distribution controlled the grain growth in which the straight GBs were arranged beneath  $Si_3N_4$  stripes, and as a result, 15 um wide single crystal films sandwitched by GBs were obtained. After removing the  $Si_3N_4$  layer, the active region of MOSFETs were defined with aligning their location to the GB-arrangement. The thickness of the gate oxide was 600 A, and the side wall of the device island had additional oxidation cycle in order to avoide the parasitic transistor.

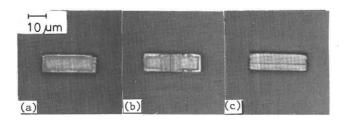

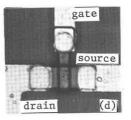

Successive fabrication steps were carried out with a conventional MOS-LSI technology. Figure 1 (a)-(d) show the several conditions of recrystallized silicon islands with and without GB, and the process finished form of PMOS/SOI. The channel dimension used in this study was 4.2 um in length and 7.7 um in width.

#### 3. EXPERIMENTAL RESULTS AND DISCUSSION

#### 3.1 GB perpendicular to the current flow

GB works as a potential barrier for carriers, which is caused by depletion of holes near the GB

due to trapping states at GB interface. Before strong inversion, there are few carriers in the channel to be trapped. Therefore the potential barrier is considered to be small. The maximum height of the potential barrier  $\Psi_B$  is given under condition of all the GB states being filled by channel carriers after strong inversion as

$$\Psi_{\rm B} = \frac{qN_{\rm ST}^2}{8\varepsilon_{\rm s}\bar{p}} \qquad (1)$$

where  $N_{\rm ST}$  is the trap density at GB interface, and  $\overline{p}$  is the average hole density in the channel. Since  $\overline{p}$  is a function of the gate voltage  $V_G$ ,  $\Psi_B$  also depends on the  $V_G$ . And it is also considered that  $\Psi_B$  depends on the doping concentration  $N_D$  of the channel region. This is because the increasing rate of the average channel carrier concentration as a function of gate voltage for PMOS having the higher doping concentration.

The current overcoming the potential barrier in the vicinity of GB is given by the classical expression of thermoionic emission (5) as

$$J_{T} \simeq A^{*} T^{2} \frac{\overline{p}}{N_{T}} \cdot \exp(-\frac{q\Psi_{B}}{kT}) \cdot (\exp(\frac{q\Psi_{T}}{kT}) - 1) \quad (2)$$

where  $A^*$  is the effective Richardson constant, and  $N_V$  is the effective density of states in the valence band.  $V_T$  is the voltage drop across the GB region which relates to the drain voltage  $V_D$ . If  $V_T$  is small, the equation (2) yields

$$J_{T} \approx \frac{q \bar{p} A^{*}}{k N_{v}} T \cdot \exp(-\frac{q \Psi_{B}}{k T}) \cdot V_{T}$$

(3)

Fig.1 Optical micrographs of recrystallized silicon islands with and without GB, and the process finished PMOS/SOI. The GBs were delinated by secco etching.

(a) no-GB, (b) one-GB perpendicular to channel, (c) one GB parallel to channel, (d) PMOS/FET

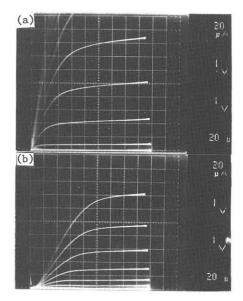

Fig.2 Typical I<sub>D</sub>-V<sub>D</sub> characteristics. (a) no-GB, (b) one-GB perpendicular to channel

In order to assess the GB effect on the electrical characteristics expected from above equations (1)-(3), following experiments were performed.

Figure 2-(a) and -(b) show typical  $\rm I_D-V_D$  characteristics of PMOS with no-GB and one-GB, respectively. The comparison of them clearly shows reduction of the channel conductance and exponential-like  $\rm I_D-V_D$  characteristics of PMOS with one-GB, supporting the equation (2).

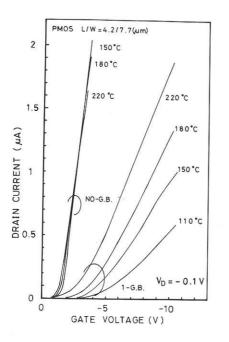

The temperature dependence of drain current  $I_D$  vs  $V_G$  was measured as shown in Fig.3. It was found that the drain current  $I_D$  varied sensitively with the temperature for PMOS with one-GB as compared with devices with no-GB. By reducing the drain voltage  $V_D$  suitable for equation (3), and plotting the data on log  $I_D$ -1/kT form, the potential barrier

Fig.3 Temperature dependence of the  ${\rm I}_{\rm D}{\rm ^{-V}_{G}}$  characteristics.

Fig.4 Measured and theoretically calculated potential barrier height.

height  $\boldsymbol{\Psi}_{B}$  depending on the gate voltage  $\boldsymbol{V}_{G}$  was obtained as shown in Fig.4. Although the potential barrier was decreased as the gate voltage became higher, it was found that there remained the potential barrier enough for scattering carriers. This result well explained the lower channel conductance of PMOS with one-GB even under relatively high gate voltage. The increase of

threshold voltage for PMOS with one-GB and the softening of the knee of the  $\rm I_D$  seen in Fig.3 were also well explained with the presence of the potential barrier, and with its variation depending on the gate voltage.

Maximum values of the potential barrier obtained in this study were 0.46 eV and 0.20 eV, for two samples with doping concentration of  $1.5 \times 10^{15}$ /cm<sup>3</sup> and  $1.2 \times 10^{16}$ /cm<sup>3</sup>, respectively. The doping concentrations were estimated from the threshold voltages of longer channel devices, since the recrystallized silicon film used in this study had the weak tendency of n-type impurity doping even for samples without phosphorus implantation.

In Fig.4, theoretical curves of the potential barrier on the gate voltage are also shown, that are obtained from the equation (1) using the assumed trap density of  $1.9 \times 10^{12}/\text{cm}^2$  and average carrier concentration  $\overline{p}$  calculated by the 2-carrier and 2-dimensional device simulator. The good agreement of the theory with the experiments indicated that the assumed value was properly consistent as the trap density in GB interface of the laser recrystallized silicon film, and was also in good agreement with the reported value for fine grain polysilicon(6).

Figure 5-(a) and-(b) show the distribution of threshold voltages of PMOS with no-GB and one-GB measured from whole 4 inch wafer, respectively. In

Fig.5 Distribution of measured threshold voltages in a 4-inch wafer from PMOS with (a) no-GB and (b) one-GB perpendicular to channel direction.

addition to the increase of average threshold voltage, the enlarged scattering was found in the PMOS with one-GB as compared with devices with no-GB. This is considered to be mainly due to the trap density in GB interface being not constant from one to another, but depending on the relative misorientation between adjacent crystal grains. Therefore it was indicated that the presence of GB in the channel led to the very poor reproducibility as well as poor controllability of the electrical characteristics of devices.

# 3.2 GB parallel to the current flow

For GB parallel to the channel direction, measured threshold voltages were almost the same values as the case of no-GB, as shown in Fig.6. And the channel conductance and the leakage current from source to drain of the device with one-GB were in the same level as those of the device without GB. These results indicated that the effective channel length was not altered, and contrasted with the case of n-channel MOSFET/SOI which has suffered drastic shortening the effective channel from length due to fast diffusion of source and drain dopants through GB (7,8). This is considered to be due to the lower diffusivity of boron in GB as compared with the arsenic or phosphorus (9) used in the n-channel devices.

Fig.6 Distribution of measured threshold voltages in a 4-inch wafer from PMOS with (a) no-GB and (b) one-GB parallel to channel direction. However, since the diffusion constant of boron in polysilicon was reported to be slightly higher than that in single crystalline silicon (10), which implied the fast diffusion through GB, the shorter channel PMOS may have the problem similar to the case of n-channel devices.

### 4. CONCLUSION

The detailed GB influence on the electrical MOSFET/SOI was characteristics of p-channel investigated, and the obtained results were in good agreement with the theoretical situation. The measured potential barrier well explained the electrical characteristics induced by the presence current flow the GB perpendicular to of The trap density was estimated to qualitatively. be  $1.9 \times 10^{12} / \text{cm}^2$ .

For GB parallel to the current flow, no remarkable effect was found on the electrical characteristics of p-channel MOSFET/SOI.

#### ACKNOWLEDGEMENT

The authors are grateful to Dr. H.Oka and Dr. H.Nakata for their interest and support of this research program. They also thank Dr. N.Kotani and Mr. S.Oda for their helpful discussion and support on the two carrier and two dimensional device simulation.

This work was performed under the management of the R&D Association for Future Electron Devices as a part of the R&D Project of Basic Technology for Future Industries sponsored by Agency of Industrial Science and Technology, MITI.

#### REFERENCES

Electron IEEE Trans. etal: 1) J.G.Fossum, Devices, ED-30,(1983)933 2) J.P.Colinge, etal; Devices, ED-30,(1983)197 3) J.P.Colinge, etal; Electron IEEE Trans. Phys. Lett.. Appl. 41(1982)346 4) T.Nishimura, etal; Extended Abstracts of the on Solid State Devices and 16th Conference Materials, Kobe, 1984 p527 5) J.Y.Seto; J.Appl.Phys., 46(1975)5247 6) H.Shichijo, etal; IEDM83 Extended Abstract p202 46(1975)5247 14th 7) T.Nishimura, etal; Proceedings of the Conference on Solid State Devices, Tokyo 1982 etal; IEEE Electron Devices Lett., 8) K.K.Ng, EDL-2(1981)316 Technol., 9) P.H.Holloway; Vac. Sci. J. 21(1982)19 Solid State Electronics., 10) S.Horiuchi, etal; 18(1975)529