# Advanced OSELO Isolation with Shallow Grooves for Three-quarter Micron ULSIs

Toru KAGA, Yoshifumi KAWAMOTO, Shin-pei IIJIMA, Yoshimi SUDOH and Yoshio SAKAI

CENTRAL RESEARCH LABORATORY, HITACHI Ltd. Kokubunji, Tokyo 185, Japan

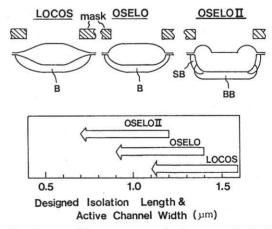

A three-quarter micron isolation process which is compatible with the LOCOS process is described. This new isolation utilizes an advanced offset local oxidation (OSELOII) process with shallow grooves. The OSELOII process is characterized by (1) a size-shifted thin  $\text{Si}_3N_{\parallel}$  mask identical to that used in the original OSELO process 1 for formation of bird's-beak-free oxidation, (2) the formation of shallow self-aligned Si grooves, and (3) a two-step boron implantation which eliminates leakage current along the isolation sidewall.

### Introduction

As device dimensions are scaled down to the submicron range, isolation technology becomes one of the most important subjects in order to produce ULSIS. For realization of submicron isolation, (1) reduction in the local oxidation bird's beak and (2) increase in effective isolation length, are necessary.

Several isolation technologies  $^{1)-6)}$  have been proposed in order to fulfill the above mentioned conditions. However, it was difficult to apply them to submicron ULSI fabrication because of process difficulties such as formation of a sidewall slope in the SWAMI type isolation<sup>3)</sup>, removing of "white ribbon" due directly to nitridation of silicon dioxide or silicon substrate in the SILO type isolation<sup>2)4)</sup>, and impurity doping on the sidewall of the silicon groove in trench type isolation<sup>5)6)</sup>.

This paper proposes a new isolation process OSELOII, which is compatible with the LOCOS process. The active MOS transistors and parasitic MOS transistors using OSELOII isolation are characterized.

OSELOI isolation technology has achieved both a reduction in the local oxidation bird's beak and an increase in effective isolation length.

### PROCESS

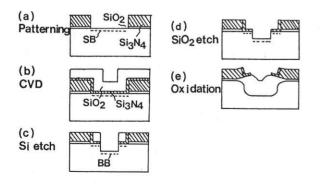

The OSELOI process is similar to the LOCOS

process shown in Fig.1 (a)-(e). First, Si<sub>3</sub>N<sub>4</sub> film for selective field oxidation is deposited on a thin pad of SiO2 and patterned (a). Next, thin  $Si_2N_{\mu}$  film for bird's-beak-free selective oxidation and SiO2 film are deposited by chemical vapor deposition (b). Sidewall spacers are, then, formed using reactive ion etching and 0.2um-deep Si grooves are formed by dry etching (c). Next, the SiO<sub>2</sub> film on the  $Si_3N_4$  layer is removed (d), and finally thick oxide is formed over the field region using selective oxidation (e). Using two-step implantation, boron doped regions are formed under the field oxide as a channel-stopper. The first implantation is made following process step (a) to avoid causing an inversion in the sidewall of the shallow grooves. The second implantation is made following process step (c) to avoid causing an inversion in the bottom of the shallow grooves.

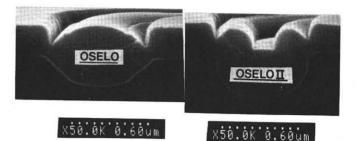

The final cross sectional SEM photograph of the OSELOII isolation is shown in Fig.2 compared with the previous OSELO isolation photograph, where the increased effective isolation length in the OSELOII structure is clearly shown.

## ELECTRICAL CHARACTERISTICS

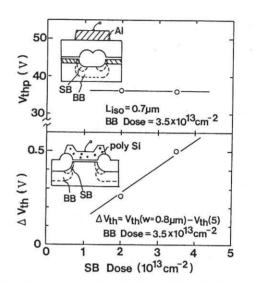

Threshold voltage  $\rm V_{thp}$  of parasitic field MOS transistors with 0.7um-wide designed isolation length and threshold voltage deviation  $\Delta \rm V_{th}$  of

narrow channel active MOS transistors are shown in Fig.3 as a function of the surface boron (SB) dose. Here,  $\Delta V_{th}$  is equal to  $V_{th}$ (0.8um-wide designed channel width) - V<sub>th</sub>(5um-wide designed channel width). Obviously,  $V_{thp}$  is independent of the SB dose; on the other hand,  $\Delta V_{th}^{}$  is almost linear to the SB dose.  $V^{}_{\mbox{thp}}$  and  $\Delta V^{}_{\mbox{th}}$  dependences on the bottom boron (BB) dose are shown in Fig.4. V<sub>thp</sub> increases as a function of the BB dose, whereas only  $\Delta \mathtt{V}_{\texttt{th}}$  has a weak dependence on the BB dose. Therefore,  ${\tt V}_{\rm thp}$  and  ${\tt \Delta V}_{\rm th}$  can be controlled by the BB dose and the SB dose, independently, which allows more freedom in designing process  $2*10^{13}$  cm<sup>-2</sup> and  $3.5*10^{13}$  cm<sup>-2</sup> are parameters. determined as an optimized SB dose and an optimized BB dose, respectively, in order to minimize narrow channel effects of the active transistors and minimize short channel effects of the parasitic field MOS transistors.

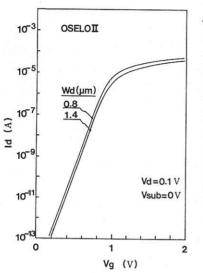

In the optimized OSELOII structure, the leakage current at the sidewall of isolation did not appear as shown in Fig.5, as neither did the hump<sup>7)</sup> characteristics due to the sidewall region's inversion.

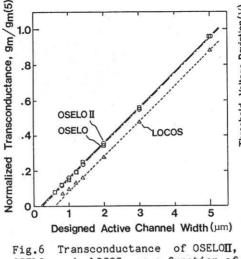

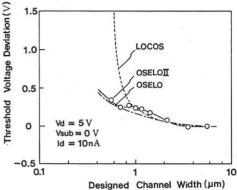

Fig.6 shows dependence of the normalized transconductance  $g_m^{\prime}/g_m^{\prime}(5)$  on the designed channel width, where  $g_m(5)$  is transconductance of an active transistor with effective 5um-wide channel width. Since g is proportional to the effective channel width, an extrapolated value of the measured points to the x-axis gives an electrical channel width shrinkage  $\Delta W$  from the designed channel width. As can be seen from Fig.6, AW of the LOCOS is 0.6um, whereas that of OSELO and OSELO∏ is 0.2um. This shows that a large improvement in the channel width narrowing can be obtained by the OSELOI structure. Furthermore, the bird's-beak-free structure in OSELOI exhibits a much smaller increase in  $V_{th}$  due to the narrow channel effect than the LOCOS structure as shown in Fig.7. The threshold voltage of the LOCOS transistor drastically increases in the region of the channel width below 1um due to the large  $\Delta W$ . On the other hand, in the OSELOII transistor, the narrow channel effect is reduced similarly to the previous OSELO's.

Consequently, by using the OSELOII structure, the current drivability of the narrow channel

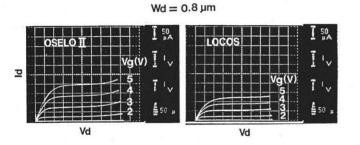

active MOS transistor can be significantly improved compared to that of the LOCOS structure as shown in Fig.8. In the OSELOII transistor with a three-quarter micron channel width, more than 60% larger drain current flows than that in the LOCOS transistor with the same design dimensions.

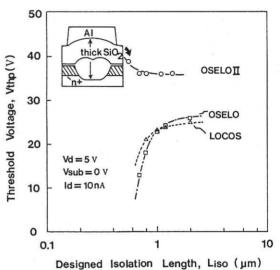

The short channel effects of parasitic MOS transistors are shown in Fig.9. The OSELOI structure features larger  $V_{thp}$  values and less short channel effects than the LOCOS and OSELO structures because the shallow grooves of the OSELOI structure increases the effective isolation length. Moreover, OSELOII provides unexpected improvement in self-feedback in short channels. That is, as the isolation length becomes less than 1um, the bird's heads at both edges of the isolation begin to approach each other and merge, thus increasing the effective field oxide thickness as shown in the inset of Moreover, because of its deep isolation Fig.9. depth and its sharp bottom edge shape, the electrical field strength from the aluminum gate electrode at the isolation bottom edge is reduced. Therefore, V thp in the short channel region becomes large enough to compensate for the lowering of V the due to the short channel effect.

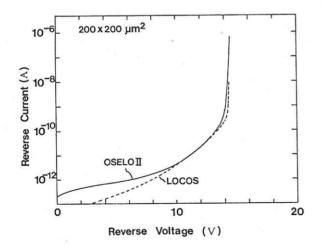

Fig.10 shows backward current-voltage characteristics of  $n^+$ -p junction diodes with a 200\*200um<sup>2</sup> area. In the small voltage region, the reverse leakage current of the OSELOII structure is several times larger than that of the LOCOS structure. This is considered to be due to the mechanical stress at the edge region of the OSELOII structure. Therefore, the field oxide thickness and the oxidation condition should be optimized to decrease such stress.

Perspective of the submicron isolation technology is shown in Fig.11, where the LOCOS, OSELO and OSELOI isolation technologies are compared. In the LOCOS structure, the minimum isolation size is limited by the narrow channel effect of the active MOS transistors, which results in a minimum isolation length of about 1.1um. In the original OSELO structure, the minimum isolation size is not limited by the narrow channel effect but is limited by the short channel effect of the parasitic MOS transistors. Therefore, OSELO is capable of producing 0.9um isolation. Since the OSELOI structure shows superior short channel effects of parasitic MOS transistors and small narrow channel effects of active MOS transistors, OSELOI is suitable for use in three-quarter micron isolation.

## SUMMARY

A new isolation technology, OSELOII, has been developed. This isolation process features: a LOCOS compatible process, an improvement in current drivability for narrow channel devices, and large threshold voltage of the parasitic field MOS transistors in the submicron range. These results demonstrate that the OSELOII isolation process is promising for three-quarter micron ULSI production.

## ACKNOWLEDGMENT

The author would like to thank Mr. T.Hayashida, A.Hiraiwa, N.Hasegawa and Y.Honma for their help in processing the wafers in this study.

#### REFERENCE

1) K. Nojiri, et al., Extended Abstracts of the 17th CSSDM, 1985, p.337

2) H-H Tsai et al., IEEE Electron Dev. Let. EDL-7, No.2, 1986, p.124

3) K.Y.Chiu et al., IEDM Technical Digest, 1982, p.224

- 4) J.Hui et al., ibid., 1982, p.220

- 5) T.Shibata et al., ibid., 1983, p.27

- 6) N.Kasai et al., ibid., 1985, p.419

- 7) K.Kurosawa et al., ibid., 1981, p.384

Fig.1 Fabrication process steps in OSELOII. SB: surface boron doped region. BB: bottom boron doped region.

Fig.2 Cross sectional views of OSELO and OSELOI obtained by SEM.

Fig.4  $V_{thp}$  and  $\Delta V_{th}$  dependence on BB dose.

Fig.6 Transconductance of OSELOH, OSELO and LOCOS as a function of designed channel width.

Fig.7 Threshold voltage of LOCOS, OSELO and OSELOII as a function of designed channel width showing the narrow channel effects.

Ld = 0.8 µm

Fig.8 Drain current vs. voltage characteristics of OSELOII and LOCOS transistors with a 0.8um designed channel width and a 0.8um designed channel length.

Fig.10 Backward current-voltage characteristics of  $n^+-p$  junction diodes.

Fig.9 Threshold voltage of parasitic field MOS transistors fabricated by using LOCOS, OSELO and OSELOII technology as a function of isolation length  $(L_{i,SO})$ .

Fig.11 Perspective on submicron isolation technology showing the minimum isolation length of LOCOS, OSELO and OSELOII structures. SB: surface boron doped region. BB: bottom boron doped region.