## Normally-Off MOS FETs Using Ultra Thin SOI Structured Si Film

Fumitoshi HATORI and Takuo SUGANO

Depertment of Electronic Engineering, University of Tokyo

7-3-1 Hongo, Bunkyo-ku, Tokyo 113, Japan

Normally-off MOS FETs have been built using ultra thin SOI structured Si film whose thickness is about 200Å. A new technique to form gate oxide is proposed here. That is,the Si film is oxidized thermally at low temperature(~800°C)for 30 minutes,and then  ${\rm SiO}_2$  film is deposited by plasma enhanced chemical vapor deposition. Fabricated devices showed good FET characteristics. The effective electron mobility  $\mu_{\rm eff}$  is about 2.0 cm²/Vs,and the threshold voltage  $V_{\rm t}$  is about 9.8V.

#### 1. Introduction

Recent development of VLSI requests reduction of device dimensions, and the gate length of Si MOS FETs will be reduced into sub-micron range. But MOS FETs of conventional structure show so called short channel effects, and so many kinds of new device structures to suppress the short channel effects, have been proposed. As one of them submicron gate MOS FETs on non-doped SOI(Silicon On Insulator) structured Si film, have been proposed by S.D.S.Malhi et al. (1) The device characteristics have been studied in our group using Monte Carlo simulation (2), and it has been concluded that this type of devices are promising as switching device for VLSI of next generation. However, if the gate length is reduced into submicron range, the thickness of the Si film must become several hundred angstrom to suppress punch through current.

In consequence a new technique to form gate oxide on ultra thin SOI structured Si film is required. Here a double layer technique using thermally grown ultra thin  ${\rm SiO_2}$  film and  ${\rm SiO_2}$  film deposited by plasma enhanced chemical vapor deposition, PECVD, is proposed, and the feasibility of this technique has been demonstrated by fabricating long channel (20 $\mu$ m) MOS FETs on SOI substrate.

## 2. Fabrication Procedure

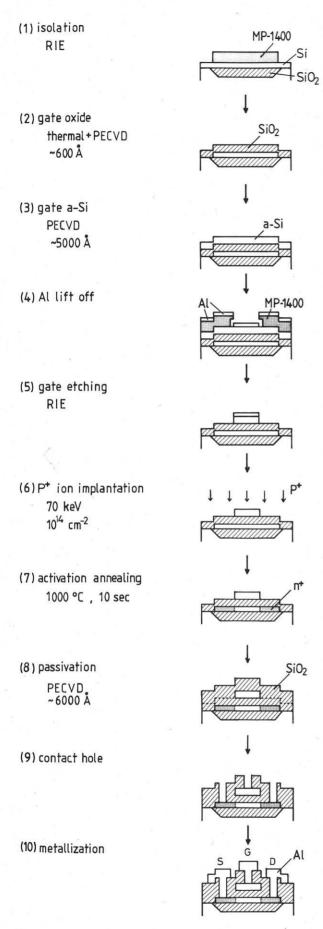

Figure 1 shows fabrication procedure of devices.

- (1) The Si films were patterned into square for isolation using reactive ion etching, RIE. The gas used in this process was CF<sub>4</sub>.

- (2) Gate oxide films were formed on the substrates using a technique which is described in section 3. The thickness of this film is about 600 Å.

- (3)Poly Si films for gate were formed on the gate oxide by PECVD using SiH<sub>4</sub>(5%)+PH<sub>3</sub>(0.05%)+Ar(~95%). The thickness of this film is about 5000 Å.

- (4),(5)The gate was formed by patterning poly-Si using RIE.

- (6) The source and drain were self-aligned to the gate poly-Si by implanting  $P^+$  at 70 keV. The dose of  $P^+$  was  $1\times10^{14}$  cm<sup>-2</sup>.

- (7) The implanted ions were activated by rapid thermal annealing, RTA.

- (8)SiO $_2$  films for passivation were deposited by PECVD using SiH $_4$ (10%)+Ar(90%) and N $_2$ O.

- (9) The contact holes were formed by chemical etching using buffered HF.

- (10) The aluminum pads were formed by evaporation.

The dimensions of the fabricated device are

Fig.1 Fabrication procedure

as follows. The gate length is 20  $\mu\text{m}$ , the gate width is 100  $\mu\text{m}$ , the thickness of the gate oxide is 600 Å, and the thickness of the Si film is 200 Å.

# 3. Characterization of Si Films and Si-SiO<sub>2</sub> Interface

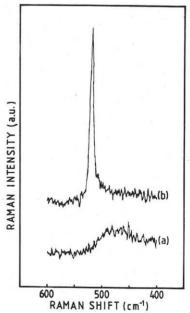

As SOI structured substrates, ultra thin Si films(~200Å), which were deposited on SiO2 films by PECVD using SiH<sub>4</sub>(90%)+Ar(10%) followed by 7.5 hrs annealing at 1100  $^{\circ}$ C in  $N_2$  ambient with capping SiO2, was used. The crystalline structure of those Si films was determined by Raman scattering. Figure 2(a) shows Raman scattering signal from asdeposited amorphous Si film, and (b) is from annealed one. This indicates that the Si films have changed from amorphous state to crystalline. The response of the single crystalline Si substrate beneath the SiO<sub>2</sub> film has not eliminated completely. However the response is not observed in Fig.2(a), and therefore the response is believed not to give any significant influence to the result shown in Fig.2(b).

Fig.2 Raman scattering signal from (a)as-deposited Si film and (b)annealed Si film

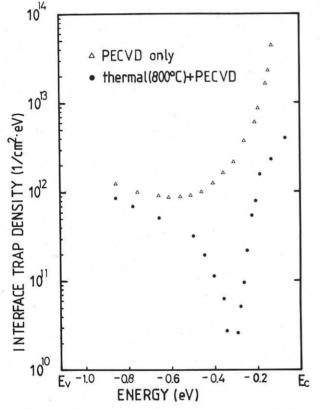

Because of very small thickness of the Si films, the oxidized depth of Si films must be controlled precisely. Therefore Si films were oxidized thermally at low temperature which was about 800°C for 30 minutes (pre-oxidation) and then SiO<sub>2</sub> films were deposited by PECVD. To measure the

interface properties, the double layer oxide were formed on single crystalline Si substrates whose resistivity was 5  $\Omega$ cm and of n type. Figure 3 is the density of interface trap states, which was measured by the Terman method. (2) The minimum density of interface trap states is about  $2.0 \times 10^{10}$  cm<sup>-2</sup>eV<sup>-1</sup>, and this is almost of the same order of magnitude obtained from Si-SiO<sub>2</sub> systems which were formed by thermal oxidation at high temperature.

Fig.3 Density of interface trap states between Si substrate and double layer  $\mathrm{SiO}_2$

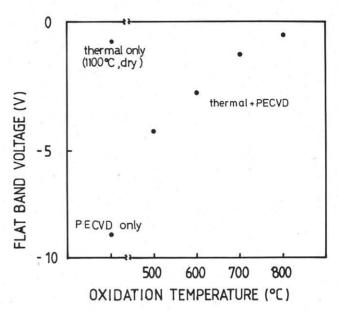

Figure 4 shows flat band voltage versus temperature of pre-oxidation. At 800°C flat band voltage is about the same as obtained from thermal oxidation at high temperature. From these characteristics it is concluded that this double layer SiO<sub>2</sub> film can be used as the gate oxide of MOS FETs, and is useful to fabricate MOS FETs on ultra thin SOI structured Si films.

## 4. Characteristics of MOS FETs and Discussion

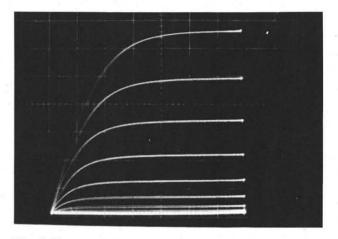

Figure 5 shows the curve tracer characteristics of a SOI MOS FET. The supplied voltage between the source and the drain was about 35 V, and between the source and the gate was 24V. The step of the gate voltage was 2V. The fabricated MOS

Fig.4 Flat band voltage versus pre-oxidation temperature

Fig.5 The curve tracer characteristics of a MOS FET

vertical 10 uA/div horizontal 5 V/div gate 0-24 V,step 2 V

Fig.6 The  ${\rm I}_{\rm DS}{\text{-V}}_{\rm GS}$  curve of the device

FETs are normally-off type devices. There is no hysteresis in this characteristics.

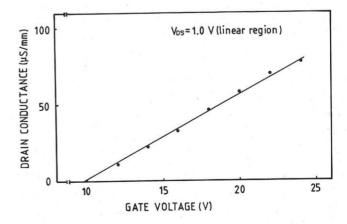

From the linear region of this characteristics(supplied voltage between the source and the drain is 1.0 V),we can obtain  ${\rm g}_{\rm D}{\rm -V}_{\rm GS}$  curve,where  ${\rm g}_{\rm D}$  means the drain-conductance and  ${\rm V}_{\rm GS}$  means the gate voltage.

From this we can obtain the effective electron mobility  $\mu_{\mbox{\footnotesize eff}}$  and the threshold voltage,using the following equation.

$$g_{D} = \frac{\partial I_{D}}{\partial V_{DS}} = \frac{Z}{L} \cdot \mu_{\circ r} \cdot C_{\circ x} \cdot (V_{GS} - V_{T})$$

where, Z is gate width(here 100 µm)

L is gate length(here 20 µm)

$\mu_{\text{eff}}$  is effective mobility

$C_{OX}$  is gate capacitance per unit area(here 54 nF/cm<sup>2</sup>)

${

m V}_{

m GS}$  is supplied voltage between the gate and the source

${

m V}_{

m DS}$  is supplied voltage between the drain and the source

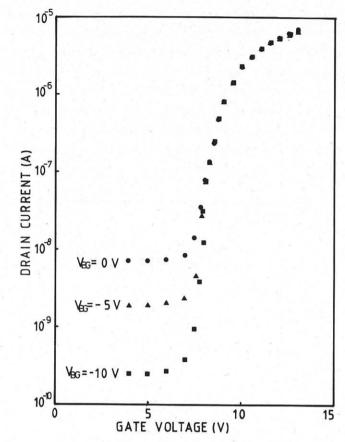

From these it has been found that  $\mu_{eff}$  is about 2.0cm<sup>2</sup>/Vs and the threshold voltage  $V_t$  is about 9.8 V. Figure 7 shows  $I_{DS}$ - $V_{GS}$  characteristics of this device, when the back gate bias is applied. Here  $I_{DS}$ - $V_{GS}$  and  $V_{BG}$  mean the drain current, the gate voltage and the back gate voltage, respectively. The decrease of the subthreshold leakage current with the increase of the back gate bias indicates that a conducting channel exists at the interface between the Si film and the SiO<sub>2</sub> substrate.

### 5. Conclusion

Double oxide layer technique using low temperature thermal oxidation and plasma enhanced chemical vapor deposition technique was successfully applied to fabricate normally-off MOS FETs in ultra thin Si film ( $\sim 200 \, \text{Å}$ ) on SiO<sub>2</sub> substrate. The devices showed good FET characteristics such as small saturation voltage and drain conductance, and the electron mobility is about 2.0 cm<sup>2</sup>/Vs. It is expected that this technique can be used to fabricate very short channel MOS FETs on SOI substrates.

Fig. 7 The back gate effect of the device

#### 6. Acknowledgment

The authors wish to thank Prof. T.Katoda and Mr. N.Hara at the Institute of Interdisciplinary Research, Faculty of Engineering, the University of Tokyo for their helpful discussions and technical assistances in Raman scattering experiments.

#### <References>

- (1)S.D.S.Malhi, H.W.Lam, R.F.Pinizzotto, A.H.Hamdi and F.D.McDaniel: IEDM 82,107

- (2)K.Throngnumchai,K.Asada and T.Sugano: IEEE Trans. ED, to be published

- (3)L.M.Terman:Solid-State Electron.5(1962),285