## Improvement of Silicon Surface Quality by H<sub>2</sub> Anneal

Y. Matsushita, M. Wakatsuki and Y. Saito

Semiconductor Materials Engineering Dept.

TOSHIBA Corporation

72, Horikawacho, Saiwai-ku, Kawasaki, 210, Japan

New simple technology using annealing in  $\mathrm{H}_2$  has been developed to improve the surface quality of silicon wafer. The  $\mathrm{H}_2$  anneal at 950 C or higher has drastic effects on both the suppression of OSF (oxidation induced stacking fault) and the improvement of DB (dielectric breakdown) failure. In addition, such a short time anneal as only 10 min. is effective enough. This effect is due to oxygen out diffusion enhancement by  $\mathrm{H}_2$  anneal.

#### 1. Introduction

Surface active area of a silicon wafer, which is used for VLSI ( Very Large Scale Integrated Circuit ) manufacture, must be kept defect free during manufacture process. If an imperfection like a micro scratch, a precipitate, a contamination and so on exists near and/or on the wafer surface, it acts as a cause of defect generation such as an OSF ( oxidation induced stacking fault ), a dislocation at edge of fine pattern and a breake down voltage failure of thin gate oxide. These defects are harmful to a device quality and reliability. For example, leakage current per an OSF, that has been measured by several researchers(1)-(5), is over several pA as shown in Table 1. If there is only one OSF in a chip of a charge coupled ( CCD ), an image defect must be observed on a screen. In addition, a device integration level comes to the higher, the defect density of the wafer surface area must be kept the lower.

| Authors             |        | Leak Current/OSF |

|---------------------|--------|------------------|

| Ravi et al.         | (1973) | 15-500 µА        |

| Tanaka et al.       | (1974) | 0.06- 6 µА       |

| Rozgoyi and Kushner | (1976) | 7- 33 pA         |

| Tanikawa et al.     | (1976) | 10 pA            |

| Ogden and Wilkinson | (1976) | 4-590 pA         |

Table 1. Leak current per one OSF.

The defect generation depends not only on the cleaness of device manufacture process but also on the crystalline quality of substrate silicon wafer surface. Howevere, it is very difficult to obtain a perfect silicon wafer, since a CZ (Czochralski-grown) silicon crystal, which is conventially used for a VLSI manufacture process, contains supersaturated oxygen. The supersaturated oxygen in silicon induces micro defects during a heat treatment (6). Therefore, it is very important to develop a treatment to make and to keep the wafer surface area perfect.

In a present study, we have developed a new simple method, which applies an annealing in  ${\rm H}_2$  ambient in order to improve the wafer surface quality.

#### 2. Experimental

# 2.1. Sample and H<sub>2</sub> anneal

Sample wafers used in the study are indicated in Table 2. The n-type wafers were mainly used because the n-type wafer is generally more difficult to supress the OSF generation than the p-type wafer. Both CZ and MCZ (Magnetic field applied Czochralski-grown) wafers were used in order to investigate the Si wafer with wide range of oxygen concentration.

The sample wafers were put into a vertical epitaxial furnace and annealed in  ${\rm H_2}$  ambient for 10 min. at a temperature 850 and 1150°C. Heat up

| No. |     | Type | Resistivity        | Oxygen Concentration                       |

|-----|-----|------|--------------------|--------------------------------------------|

| C-1 | CZ  | n    | 35-45 <b>Ω</b> ⋅cm | 16-18x10 <sup>17</sup> atm/cm <sup>3</sup> |

| C-2 | CZ  | р    | 6- 8               | 12-14x10 <sup>17</sup>                     |

| M-1 | MCZ | n    | 35-45              | 17.3-19.3x10 <sup>17</sup>                 |

| M-2 | MCZ | n    | 35-60              | 10.7-11.5x10 <sup>17</sup>                 |

| M-3 | MCZ | n    | 35-45              | 6.6- 7.2x10 <sup>17</sup>                  |

Table. 2. Characteristics of sample wafers. (Oxygen convergent factor; 4.81x10<sup>17</sup>)

rate and cool down rate were 0.5°C/sec. and 1°C/sec., respectively. Besides, Si etching was also carried out by flowing HCl gas of 500 cc/min. for 1 min. at an annealing temperature. 2.2 OSF density evaluation

Both as-recieved and  $\rm H_2$  annealed wafers were oxidized in dry  $\rm O_2$  at  $1000^{\rm o}{\rm C}$  for 16 hr. After the oxide remove, the wafers were preferentially etched by Wright solution and the OSFs on the mirror surfaces were observed by an interference optical microscope. Impurities in the oxide films were analyzed by using the flameless atomic absorption spectrophotometry (AA) with a vapor phase decomposition method (VPD) $^{(7)}$ , in order to invetigate the relation between the OSF density and the impurity concentrations.

# 2.3. Dielectric breakdown ( DB ) field measurement for thin oxide film

A thin oxide film on the wafer surface with and without  $\rm H_2$  anneal was formed by heat treatment in dry  $\rm O_2$  at  $1000^{\rm o}{\rm C}$ . The oxide film thickness was 28 nm. A 400nm poly Si layer was deposited by LPCVD method and diffused with phosphorus. The poly Si was patterned and  $4x2.5 \, {\rm mm}^2$  capacitors were produced. The DB field of the capacitor was defined as the applied field at which the current was over  $0.15 \, \mu \, {\rm A}$ .

### 3. Experimental results

### 3.1. H<sub>2</sub> pre-anneal effect on OSF generation

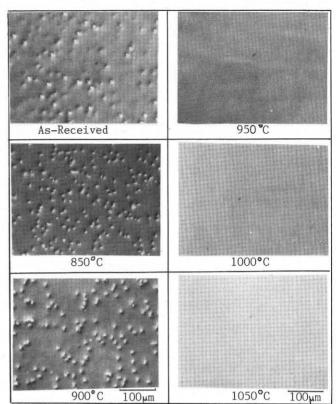

Figure 1 shows the Wright etching / optical micrographs of the wafers after oxidation at  $1000^{\circ}$  C for 16 hr. in dry  $0_2$ , when the pre-anneal temperature in  $\mathrm{H_2}$  ambient was changed. Figure 2 shows the relation between the OSF density after oxidation and the pre-anneal temperature in  $\mathrm{H_2}$  ambient. When the pre-anneal temperature is  $900^{\circ}$  C or lower, the OSF density in the annealed wafer is nearly same as that in the as-received wafer. When the pre-anneal was carried out at a temperature not lower than  $950^{\circ}$ C, however, the

Fig. 1. Etching/micrograph of sample wafer annealed in H<sub>2</sub> after oxidation at 1000°C.

Fig. 2. OSF density as a function of annealing temperature in H<sub>2</sub>.

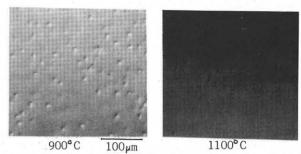

Fig. 3. Etching/micrograph of sample wafer etched by HCl gas followed by H2 anneal after oxidation at 1000°C.

OSF density was drastically decreased. For example, in the sample C-1, the OSF density, that is as high as  $4.2 \times 10^4 \text{cm}^{-2}$  in as-received wafer, is suprisingly decreased to a level lower than 10 cm<sup>-2</sup> in the wafer pre-annealed at  $1100^{\circ}\text{C}$  in  $\text{H}_2$  ambient. On the other hand, in the sample M-2, which does not induce so many OSFs ( $5 \text{cm}^{-2}$ ) in as-received wafer, almost all OSFs can be suppressed by applying the  $\text{H}_2$  pre-anneal at  $1100^{\circ}$  C. Therefore, the  $\text{H}_2$  anneal at  $950^{\circ}\text{C}$  or higher can be a pre-oxidation gettering process for OSF, regardless of the OSF density induced in the as-received wafer.

When the sample wafers were subjected to lmin. HCl etching followed by  $\rm H_2$  anneal for 10 min., the OSF suppression effect was also recognized in the sample annealed at 950 °C or higher (Fig. 3). However, the wafer surface has not been always mirror but hazy.

## 3.2. Oxide DB failure improvement by $\mathrm{H}_2$ anneal

The DB fieled of 28 nm oxide film formed on the wafer as-received and annealed in  $\rm H_2$  was measured. Figure 4 shows the DB field as a function of anneal temperature in  $\rm H_2$ . Solid marks show the fraction of capacitors of which DB field was over 8 MV/cm (C-mode). Open marks indicate the fraction of capacitors whose DB field was between 1 MV/cm and 8 MV/cm (B-mode). When the  $\rm H_2$  anneal temperature was the higher, the C-mode ratio became the more. That is apparently recognized in the samples annealed in  $\rm H_2$  at 950°C or higher.

Fig. 4. DB field ratio as a function of  $\rm H_{2}$  anneal temperature.

Therefore, it is asserted that the wafer surface quality is remarkablly improved by applying the  ${\rm H}_2$  anneal.

#### 4. Discussion

It was recongnized that the surface quality was drastically improved by  $\mathrm{H}_2$  anneal at 950°C or higher, which was very effective for the OSF suppression and the thin oxide DB failure improvement. In addition, it was effective enough that the  $\mathrm{H}_2$  anneal time was as short as only 10 min. This effect has not been recongnized in other atomspheres like  $\mathrm{N}_2$  or  $\mathrm{O}_2$ .

In order to investigate the  $H_2$  anneal effect, metalic impurities in an oxide layer formed on the wafer annealed in  $H_2$  were analyzed by VPD/AA method. Figure 5 shows the impurity concentration in the oxide film formed on the wafer before and after H2 anneal. It is clear that the metalic impurity concentration on the after annealed in H<sub>2</sub> is higher than that on the as-recieved wafer. The metalic impurities on the wafer surface probably come from the epitaxial furnace during  ${\rm H}_2$  anneal. If the metalic impurity on the wafer surface makes an origin of the OSF generation or the DB failure, these experimental results could not be solved. That is, the metalic impurities as many as  $10^{11}$  -  $10^{12}$ atoms/cm<sup>2</sup> does not directly correlate to the OSF generation or the DB failure. If the contamination level gets higher, the OSF generation would be enhanced, but that is not pratical contamination level in the conventionally used wafer.

Fig. 5. Impurity concentration in oxide film formed on wafer befor and after H<sub>2</sub> anneal.

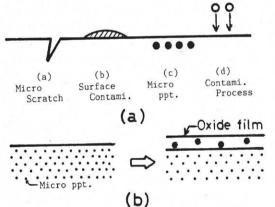

The origin of OSF is considered to be as follows (Fig. 6 (a)).

- (a) Micro scratch on the wafer surface.

- (b) Surface contamination.

- (c) Micro precipitate or micro defect existing near the surface area.

- (d)Contamination during device manufacture process.

The (a), (b) and (c) are problems in as-received wafer. The  $\mathrm{H}_2$  anneal is probablly effective on these problems. The micro scratch is annealed out during the heat treatment and the surface contamination, that would be composed by an organic compound, may be reduced by  $\mathrm{H}_2$ .

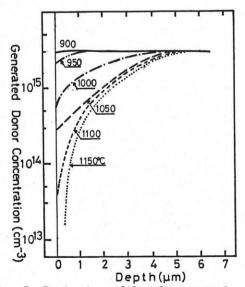

Moreover, the micro precipitate, that is a nucleus for oxygen precipitate, would be able to disappear perfectly near the wafer surface, because oxygen out diffusion is enhanced in  $\rm H_2$  ambient. In fact, oxygen outdiffusion is clearly observed after  $\rm H_2$  anneal for 10 min. at a

Fig. 7. Origins of OSF (a) and oxide DB failure (b)

Fig. 7. In-depth profile of generated oxygen donor concentration in  $\rm H_2$  annealed wafer after heat treatment at 450°C for 64 hr.

temperature higher than 950°C as shown in Fig. 7. Figure 7 shows the oxygen donor concentration induced by a heat treatment at 450°C for 64 hr. in dry  $0_2$  in the sample wafer annealed in  $\mathrm{H}_2$ . It is clear that the oxygen donor concentration is very low near the wafer surface, then the oxygen diffuses out there.

In addition, the micro precipitate near the wafer surface would be an origin of the thin oxide DB failure. Figure 6 (b) shows the model of the thin oxide DB failure proposed by Yamabe et al.  $^{(8)}$  The  $\rm H_2$  anneal is very effective on the DB improvement, because of the micro precipitate dissolution near the wafer surface.

#### 5. Conclusion

It is proved that the H<sub>2</sub> anneal at 950°C or higher is very effective on both the OSF suppression and the DB failure improvement of thin oxide film. Moreover, a short anneal time such as 10 min. is enough to get a good effect. The H<sub>2</sub> anneal effect is probablly due to oxygen out diffusion enhancement and micro precipitate dissolution near the wafer surface. This process can be applied as pre-oxidation gettering process.

### 6. Acknowledgment

The authors appreciate to Mr. Y.Yamabe and Miss M.Onodera for their cooperation to measure the DB field of thin oxide film.

#### 7. References

- (1)K.V.Ravi, C.J.Varker and C.E.Volk: J. Electrochem. Soc., 120,533 (1973)

- (2)K.Tanaka, G.Nakayama, M.Amano and Y.Yukimoto: Elecctrochem. Soc. 1974 Fall Meeting Ext. Abst.,#193, p472

- (3)G.A.Rozgonyi and R.A.Kushner: J. Electrochem. Soc., 123,570 (1976)

- (4)K.Tanikawa, Y.Itoh and H.Sei: Appl. Phys. Lett., 28, 285 (1976)

- (5)R.Ogden and Y.M.Wilkinson: J. Appl. Phys. 48,412 (1977)

- (6)Y.Matsushita: J. Cryst. Growth, 56,516(1982)

- (7)A.Shimazaki, H.Hiratsuka, Y.Matsushita and S.Yoshii: Ext. Abst. 16th Conf. Solid State Devices and Materials (Kobe,1984)p281

- (8)K.Yamabe, K.Taniguchi and Y.Matsushita: 21st Ann. Proc. Reliability Physics (1983),p184