Extended Abstracts of the 18th (1986 International) Conference on Solid State Devices and Materials, Tokyo, 1986, pp. 699-702

# D-11-3

## Improved Reliability in Amorphous Silicon Thin Film Transistors

Y.Kaneko, A.Sasano, T.Tsukada, R.Oritsuki and K.Suzuki Central Research Laboratory, Hitachi, Ltd. Kokubunji, Tokyo 185, Japan \* Mobara Works, Hitachi, Ltd. Mobara, Chiba 297, Japan

The threshold voltage shift of a-Si TFT's for various fabrication conditions is discussed. The fabrication conditions have been optimized to obtain an improved a-Si /SiN interface and deposition temperature is chosen between  $300^{\circ}$  and  $360^{\circ}$  in contrast to a conventional range of  $200-300^{\circ}$ . Estimation of the threshold voltage shift of our optimized samples is as low as -0.7V for a negative voltage stress of 20V for a supposed lifespan of  $10^4$  hours operation. This is guite acceptable for an LCD panel.

#### 1. Introduction

Recently, there has been considerable amount of study on amorphous silicon thin film transistors (a-Si TFT's) for application to active matrix liquid crystal display panels, whose features are feasibility of full-colored display, low power consumption, lightweight, etc. Some of the advantages of a-Si TFT's are good switching characteristics, capability of large area deposition, reproducibility, and a low temperature fabrication process. Our a-Si TFT's achieve a high ratio of Ion/Ioff exceeding 7 orders of magnitude with a subthreshold slope as steep as 0.3V/decade. It has been shown that these values are sufficient for a switching matrix application[1].

However, the instability of a-Si TFT's, i.e., the threshold voltage(Vt) shift during their operation, still poses a serious problem. This instability has been investigated in various stress voltage conditions. Above all, it has been found that the Vt shift is mainly caused by applying the gate voltage. The amount of Vt shift ( $\Delta$ Vt) as a function of time and temperature in addition to the gate bias has also been studied. These dependences have been formulated and used to estimate the  $\Delta$ Vt after a certain operating time, e.g., 10<sup>4</sup> hours[2].

It has been suggested[3] that the quality of interface between a-Si and silicon nitride(SiN) or

the density of charge trap levels at/near the interface plays an important role in the Vt shift. We have found that the fabrication condition of a-Si TFT's is closely related to the interface quality.

In this paper, we report the optimization of fabrication conditions to reduce the  $\Delta Vt$  by improving the interface quality between a gate insulator of SiN and a-Si. Also, the estimate of the threshold voltage shift of such optimized a-Si TFT's is presented.

#### 2. Experiment

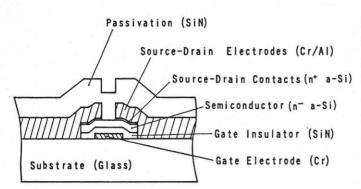

The cross-sectional view of a-Si TFT's is shown in Fig.1. The configuration of TFT's has a bottom gate staggered structure with a gate insulator of SiN. On the glass substrates, both SiN and a-Si film are deposited in an rf glow discharge of a gas mixture of SiH<sub>4</sub>-NH<sub>3</sub>-N<sub>2</sub> and that of SiH<sub>4</sub>-H<sub>2</sub>, respectively. Deposition is carried out at a substrate temperature between 200°C and 420°C.

The threshold voltage is defined as the gate voltage at the intersection of extrapolation of the saturation region in the √ Id vs. Vg curve as well as the voltage at which drain current corresponds to some value, e.g., 30nÅ. The amount of Vt shift is measured as the difference of Vt in before and after applying the stress voltage to

FIG. 1. Cross-sectional view of a-Si TFT.

the TFT's. The stress gate voltage is between -30V and 30V. The drain voltage has little relation to the Vt shift and is set to 0V. Before each measurement of the  $\Delta$ Vt, threshold voltage of a-Si TFT's is initialized by thermal annealing at 180°C for 30 minutes. This initialization procedure can be applied to the same sample more than ten times without deteriorating the device characteristics. Since amorphous silicon has high photoconductivity, all the measurements are carried out in the dark where the influence of photo-induced carriers are negligible [4].

#### 3. Results

### 3.1 Vt Shift of a-Si TFT's

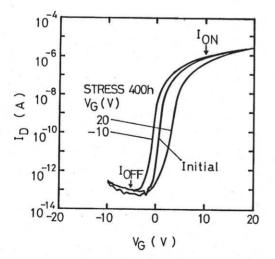

Figure 2 shows the Id vs. Vg characteristics of a-Si TFT's before and after dc gate bias stress of -10V and 20V for 400 hours. When a positive (negative) gate bias is applied to the TFT's, the

(SiN) Vt is positive(negative), which implies that the Vt shift of a-Si TFT's is mainly due to the charge trapping into a gate insulator of SiN[5]. The Source-Drain Contacts (n<sup>+</sup> a-Si) threshold voltage shift as a function of various stress conditions has been investigated, and as for the dc bias stress, the results can be summarized in the following formula,

$$\Delta Vt \sim \alpha \cdot Vg \stackrel{\beta}{\cdot} (\log(t))^{\gamma} \cdot \exp(-\Delta E/kT), \qquad (1)$$

where Vg is the stress gate bias, t the operation time of a-Si TFT's, T the absolute temperature, k the Boltzmann's constant,  $\Delta E$  the activation energy for charge trapping process and  $\alpha$ ,  $\beta$ , and  $\gamma$  the constants.

In the stress conditions between room temperature and 100°C, the value of  $\Delta E$  has been 0.3eV for both positive and negative gate bias. The constant  $\alpha$  depends on the fabrication conditions. The value  $\beta$  has been found to be 1.7 for Vg>0 and is 4 for Vg  $\leq 0$ . It has been confirmed that  $\gamma$ is equal to 2 for both signs of gate voltage up to 2,000 hours. The values of these constants besides  $\alpha$  did not scatter from run to run.

Constant  $\alpha$  has different values for positive gate bias stress and negative bias stress. It is desirable to lower  $\alpha$  for a negative bias, since the voltage shift under a negative bias plays a greater role than that under a positive bias which is a pulsed stress[2]. The lowered  $\alpha$  value to realize improved reliability in TFT's is obtained as described later.

3.2 Optimization of Fabrication Conditions

High quality of the a-Si/SiN interface is necessary to improve the reliability in a-Si TFT's. To achieve this, the optimization of fabrication condition has been proved to be effective. Particularly, two ways of optimization were developed. First, the volume ratios of N<sub>2</sub> and NH<sub>3</sub> to SiH<sub>4</sub> in depositing chamber has been found to have a great influence on the Vt shift under stress. As the volume ratio NH<sub>3</sub>/SiH<sub>4</sub> or N<sub>2</sub>/SiH<sub>4</sub> is increased, the  $\Delta$  Vt decreased sharply and the variation of the  $\Delta$  Vt becomes small gradually. This is interpreted as to what extent stoichiometry in SiN is achieved.

$\begin{array}{c}

10^{-4} \\

(4) \\

(7) \\

(7) \\

(8) \\

(9) \\

10^{-5} \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9) \\

(9$

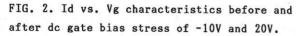

FIG. 3. Dependence of Vt shift on a-Si deposition temperature for 1,000 sec TFT operation.

which means the densities of trap levels are caused by the dangling bonds of Si atoms in the silicon-rich SiN film. Consequently, from the point of view of reliability, the volume ratios of material gases are important factors.

Secondly, a more important factor to attain high reliability is the deposition temperature. In contrast to a supposed optimum a-Si deposition temperature around 200-230°C, it has been found that a temperature range higher than 300℃ is a good choice as far as reliability is concerned. Figure 3 shows the Vt shift after 1,000 sec TFT operation as a function of a-Si deposition temperature. Reduction of the voltage shift is apparent in a range higher than 300°C for both signs of gate bias voltage. Figure 4 shows the dependence of drain current on deposition temperature. The on current(Vg=10V) decreases and the off current (Vg=-5V) increases as the temperature rises above 360℃. Below this temperature, a sufficient ratio of Ion/Ioff can be obtained indicating an optimum temperature range between 300℃ and 360℃. This temperature effect is speculated to be due to the reduction of the trap density at the a-Si/SiN interface by thermal annealing.

By the optimization described above, the  $\alpha$  value for the negative gate bias is lowered to

FIG. 4. Dependence of on current(Vg=10V) and off current(Vg=-5V) on a-Si deposition temperature.

less than one fifth the previous one[2], that is, 7.5×10<sup>3</sup>. The Vt shift for long term operation with a negative dc voltage of 20V can be estimated from the  $\Delta$ Vt for 1,000 sec by Eq. 1. For the samples fabricated at a deposition temperature of 320°C, the calculated shift is as low as -0.7V after 10<sup>4</sup> hours operation.

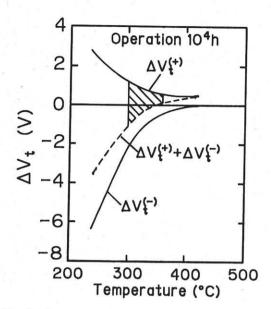

The threshold voltage shift of TFT's on the LCD panel can be estimated as follows. For the LCD panel with N gate scanning lines, TFT's are under positive bias for 1/N of operation time and under negative bias for almost the entire time. In the case N=1,000, a gate pulse height of 20V, a signal pulse of 20V from peak to peak, and 10<sup>4</sup> hours operation time, which are considered as reasonable values for normal use of an LCD, TFT's are under a positive bias of 20V for 10 hours and a negative bias of 20V for almost the entire time in 10<sup>4</sup> hours operation. The estimate of total threshold voltage shift can be obtained as the sum of the  $\Delta Vt$  for negative and positive bias. For our optimised a-Si TFT's fabricated at a deposition temperature of 300-360°C, the sum is less than 1V as shown in Fig. 5. For the LCD which can display gray scale, the total  $\Delta Vt$  is estimated to be between the above sum and the  $\Delta Vt$  for the positive bias(the shaded region in Fig. 5), which is also less than 1V.

FIG. 5. Estimation of Vt shift after  $10^4$  hours operation vs. a-Si deposition temperature.

### 4. Conclusions

The threshold voltage shift of a-Si TFT's for various fabrication conditions has been optimized to improve the quality of the a-Si/SiN interface. The optimum deposition temperature range is between  $300^{\circ}$  and  $360^{\circ}$ . The Vt shift of our optimized sample has been estimated to be less than 1V after a supposed lifespan of  $10^4$  hours, which is quite an acceptable value for LCD panels.

## ACKNOWLEDGEMENTS

The authors would like to thank H.Matsumaru, K.Tsutsui, Y.Tanaka, M.Fukasawa and K.Seki of Central Research Laboratory, Hitachi, Ltd. for their technical discussions and support in preparing the samples. We greatfully acknowledge the encouragement and support from Dr. S.Asai of Central Research Laboratory, Hitachi, Ltd. and H.Suzuki of Mobara Works, Hitachi, Ltd..

### REFFERENCES

- [1] K.Suzuki, H.Suzuki, T.Tsukada and H.Kawakami

Proc. Intn'l Display Conference, '85, 14 (1985).

- [2] Y.Kaneko, R.Oritsuki and T.Tsukada: Digest of Tech. Reports(I.E.C.E. of Japan), ED85-79 (1985) (in Japanese).

- [3] M.J.Powell: Appl. Phys. Lett., 43, 597 (1983).

- [4] J.Vaid and H.Fritzsche: J. Appl. Phys., 55, 440 (1984).

- [5] S.M.Sze: Physics of Semiconductor Devices (Jhon Wiely and Sons, 1981)2nd ed., Chap.7.