Extended Abstracts of the 19th Conference on Solid State Devices and Materials, Tokyo, 1987, pp. 179-182

# **MOS-FETs Fabricated by SPE-SOI Technology**

K. Kusukawa, M. Moniwa, E. Murakami, M. Miyao, T. Warabisako, and Y. Wada Central Research Laboratory, Hitachi Ltd., Kokubunji, Tokyo 185, Japan

Electrical characteristics of Si layers on SiO<sub>2</sub> obtained by seeded-lateral Solid Phase Epitaxy were evaluated as a function of distance from the seeding area. According to the two growth modes in lateral epitaxy, it was found that there are significant difference in the electrical characteristics of MOSFETs fabricated in those regions. A field effect (electron) mobility of about 700cm<sup>2</sup>/Vs was obtained for n-channel MOSFETs fabricated in the {110}-facet grown region. However, the electrical properties of MOSFETs fabricated in the {111}-facet growth region were not as good. The results suggest that the {110}-facet growth region is suitable for devices with a feature size of less than  $2 \mu$  m.

# 1. Introduction

Silicon-on-insulator (SOI) structures have been investigated intensively to realize 3-dimensional structures in an attempt to realize high speed, high packing density, and multi functions. Several methods of realizing SOI structures have already been proposed, such as liquid phase epitaxial re-growth of polycrystalline silicon using laser beam<sup>1)</sup> or electron beam<sup>2)</sup> irradiation, and buried oxide formation with oxygen ion implantation (SIMOX)<sup>3)</sup>. In fabricating 3-dimensional devices, it is extremely important not to affect the underlying device structure either thermally or mechanically. From this viewpoint, a low temperature process is required for the SOI process. One suitable technology is lateral solid phase epitaxial (L-SPE) growth. In this technology, an amorphous Si layer on an insulator is converted into single crystal silicon by epitaxial growth in the solid phase.

As the process can be carried out at a relatively low temperature around 600  $^\circ\!\!\!C$ , it

can be regarded as the most promising method for fabricating devices on top of underlying devices covered by insulators.

So far, several reports have appeared on L-SPE concerning the dependence of the growth length of the single crystalline area on crystallographic orientation<sup>4-5)</sup>, the cross sectonal TEM observation of the grown region<sup>6-7)</sup>, impurity-enhanced crystal growth in L-SPE<sup>8)</sup>, and so on. However, very little has been reported about the electrical characteristics of the grown are a<sup>9-10)</sup>.

The present paper describes the characterization of n-channel MOSFETs fabricated in an SOI structure formed by L-SPE. The discussion focuses especially on the relation between electrical characteristics and the crystallinity.

## 2. SOI Formation by L-SPE

A p-type,  $(100)Si(8-12\,\Omega\,cm)$  wafer was used as the starting material. The substrate was coated with 200nm-thick thermal SiO<sub>2</sub> arranged in stripe patterns. The patterns were formed perpendicular to

the <100> direction, which was the direction of the longest L-SPE growth. The substrate surface were cleaned prior to a-Si deposition using low energy Ar-ion beam sputtering with N<sub>2</sub> annealing at 680°C (60min). After surface cleanning, an a-Si layer was formed by electron beam deposition in an ultra-high vacuum (<2x10<sup>-7</sup>Pa) to a thickness of 0.45-0.6  $\mu$  m. Then the a-Si layer was annealed at 450 °C in ultra-high vacnum. L-SPE of the a-Si layer was carried out by N<sub>2</sub> annealing at 600°C.

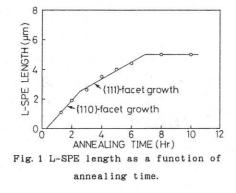

Single crystal growth length is shown in Fig. 1 as a function of annealing time. Single crystal growth occurs first vertically from the substrate surface in the {100}-facet growth mode and then laterally after over-riding the edge of SiO, pattern. There are two growth modes, in the lateral growth direction. The first is facet growth in the {.110} direction followed by facet growth in the {111} direction which continues until L-SPE stops.

The existence of such a growth mode has already been reported<sup>5)</sup>. In the case of Fig. 1, the growth length was  $2.5 \mu$  m for both the {110}-facet growth region and the {111}-facet growth region. Given this background, the annealing period for MOSFET fabrication was determined to be 7Hrs.

3. Fabrication of SOI-MOSFETs

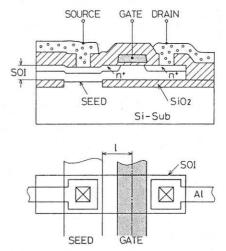

The MOSFETs shown in Fig.2 were fabricated on SOI structures formed by the

processes mentioned above.

After the etch-off device isolation process which leaves the SOI layer for MOSFET fabrication, B-ions were implanted  $(30 \text{keV}, 3 \times 10^{11} \text{ cm}^{-2})$  to make the SOI layer p-type for nMOS fabrication. MOSFETs (gate oxide thickness; 35nm) were then fabricated by means of the conventional poly-Si gate nMOS fabrication process. The gate length and the gate width of the MOSFETs was 1-10  $\mu$  m and 4-10  $\mu$  m. respectively.

To evaluate the electrical properties of the SOI layers. MOSFETs were fabricated in a grown layer by changing the location of the channel region.

Fig. 2 The structure of the SOI MOSFET.

Electerical characteristics of SPE-SOI MOSFETs

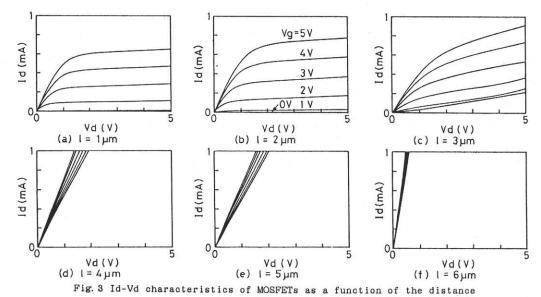

Drain current-drain voltage (Id-Vd) characteristics are shown in Fig. 3 as a function of distance (l) between the edge of the seeding region and the center of the Distance (l) was varied from 1 to gate. The electrical characteristics of 6 4 m. MOSFETs fabricated within 2 µm from the seed edge are quite ordinary and very much comparable to those for bulk MOSFETs. However, in the case of l larger than  $3\,\mu\,\mathrm{m}$  the fabricated MOSFETs showed an abnormal function. Subthreshold drain current, measured at a drain voltage and a gate voltage are 5V and OV, respectivery,

between the edge of the seeding region and the center of the gate.

a function of l, is plotted as and the results are shown in Fig. 4. The figure that leakage current also shows in the {111}-facet region and in the polycrystalline region is very much larger than that in the {110}-facet growth region. These results correspond to the facet growth mode, and only the MOSFETS fabricated in the {110}-facet growth region operate normally.

Two main reasons can be considered for the increase in leakage current. One is increase generationthe in carrier recombination velocity in the junction area due to an inferior crystallinity in the vicinity of the channel region. The other the possibility of an electrical is

short-circuit between the source and drain, arising as a result of enhanced inpurity diffusion, which was caused by high density (micro twins)<sup>4)</sup> crystal defects in the {111}-facet region and at grain boundaries the in polycrystalline region, during thermal processes.

To clarify the reason, leakage current dependence on *l* was measured for MOSFETs with a long gate length  $(4\mu m)$ . These MOSFETs are not influenced by even a rather large redistribution of impurities in the source and drain regions. The results are also shown in Fig. 4 in contrast with those for the  $2\mu$ m gate. The leakage current level is low compared with that for the and does not show *l* dependence 2µm case, with increasing distance from the seeding area. The result clearly shows that leakage current is not due to recombination centers but due drain-source to 8 short-circuit which originates from the enhanced impurity diffusion.

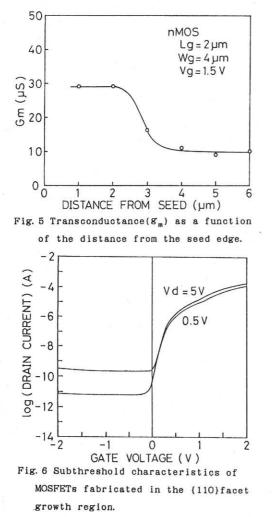

Transconductance (gm) was measured under a drain voltage of 0.1V. The result is plotted against l and is shown in Fig. 5. The figure shows that g<sub>m</sub> is almost approximately  $26\,\mu\,\mathrm{S}$  when l is constant at less than 2 µm. This value corresponds to mobility of 720cm<sup>2</sup>/Vs. a field effect

However,  $g_m$  decrease to  $10 \mu$  S when L becomes larger than  $3\mu$  m. This indicates that  $\mathfrak{S}_m$  characteristics, as well as leakage current characteristics, degrade in the {111}-facet growth region. With respect to the subthethold characteristics of MOSFETs fabricated in the {110}-facet growth region, the leakage current (drain current) at a drain voltage of 5V and at a gate voltage OV of was measured to be  $5 \times 10^{-11} \text{ A} / \mu \text{ m}$ and tailing factor was 85mV/dec. These values were obtained for more than 80% of the devices fabricated on a 100mm diameter Si wafer.

5. Conclusion

The electrical characteristics of n-cannel MOSFETs fabricated in the L-SPE SOI region were investigated. The differences in electrical characteristics between the growth modes in L-SPE were

MOSFETs fabricated in distinctive. the {111}-facet growth region have low channel mobilities and high leakage current. On the contrary, the electerical characteristics of MOSFETs grown in the {110}-facet growth region were shown to be quite suitable for LSI applications.

SOI structures formed by L-SPE in the {110}-facet growth direction is expcted to play an important rule in novel 3-dimensional device structures.

### Acknowledgements

The authors would like to express their appreciation to Drs. T. Hayashida and M. Ohkura for their thoughtful discussions.

#### References

- H. W. Lam. R. F. Pinizzotto and A. F. Tasch ; J. Electrochem. Soc. 128(1981)1981.

- T. Hamasaki, T. Inoue, I. Higashinakagawa, T. Yoshii, M. Kashiwagi and H. Tango; Proc. Conf. Solid State Device and Materials, Tokyo(1985)135.

- K. Izumi, M. Doken and H. Ariyoshi; Electron. Lett. 14(1978)593.

- Y. Ohmura, Y. Matsushita and M. Kashiwagi ; Jpn. J. Appl. Phys. 21(1983)L152.

- 5) M. Miyao, M. Moniwa, M. Ichikawa, A. Ishizaka, T. Doi, H. Sunamiand T. Tokuyama; Proc. Conf. Solid State Devices and Materials, Kobe, (1984)511.

- R. Drost and J. Washburn ; J. Appl. Phys. 53 (1982)397.

- Y. Kunii, M. Tabe and K. Kajiyama; J. Appl. Phys. 56(1984)279.

- L. Csepregi, E. F. Kennedy, T. J. Gallagher, J. W. Mayer and T. W. Sigmon; J. Appl. Phys. 48 (1977)4234.

- H. Ishiwara, M. Tanaka and S. Furukawa; Proc. Conf. Solid State Devices and Materials, Tokyo(1986)553.

- 10)M. Sasaki, T. Katoh and H. Onoda; Appl. Phys. Lett. 49(1986)397.