Extended Abstracts of the 20th (1988 International) Conference on Solid State Devices and Materials, Tokyo, 1988, pp. 141-144

# Characteristics of Bipolar Transistors with Various Depth n<sup>+</sup> Buried Layers Formed by High Energy Ion Implantation

A. Tamba, Y. Kobayashi, T. Suzuki<sup>\*</sup> and N. Natsuaki<sup>\*</sup>

Hitachi Research Laboratory, Hitachi Ltd.

4026 Kuji-cho, Hitachi-shi, Ibaraki 319-12, Japan

\* Central Research Laboratory, Hitachi Ltd., Kokubunji, Tokyo 185, Japan

Bipolar transistors having various depth  $n^+$  buried layers formed by high energy ion implantation are investigated in order to obtain various performance bipolar transistors in the same chip. BV<sub>CEO</sub> values are controlled and decreased with increasing oxide thickness by high-energy ion implantation in Si dioxide film of varying thicknesses. The maximum obtained BV<sub>CEO</sub> value is 7.8V. Base-collector leakage currents are very small when secondary defects are buried in the  $n^+$  buried layer. This method should be very effective for designing both BiCMOS and multi-function LSIs.

## 1. Introduction

BiCMOS LSIs are very promising LSIs because they have both high speed and low power dispersion characteristics<sup>1</sup>,<sup>7</sup>). High performance npn bipolar transistors used for BiCMOS LSIs require n<sup>+</sup> buried layers. Since n<sup>+</sup> buried layers are necessary for many processes, like Si epitaxial growth, layer formation production cost is high. Therefore the cost of n<sup>+</sup> buried layers has limited BiCMOS LSI technology application. Another drawback is that the performance of bipolar transistors used for BiCMOS LSIs is uniform in the same chip because the depth of n<sup>+</sup> buried layers is solely decided by Si epitaxial layer thickness. Under uniform conditions, it is difficult to achieve high speed and multi-functionable BiCMOS LSIs.

This paper proposes the formation of varying depth  $n^+$  buried layers in the same chip using a high energy ion implantation (HEI<sup>2</sup>) technique<sup>2,3,4</sup>) in order to achieve lower cost-, high speed-, multi-function-BiCMOS LSIs. The varying depth  $n^+$  buried layers formed by high-energy ion implantation in SiO<sub>2</sub> film of varying thickness,

Fig. 1 Procedure of making various depth n<sup>+</sup> buried layers

and the varying performance bipolar transistors obtained, are reported.

#### 2. Experiments

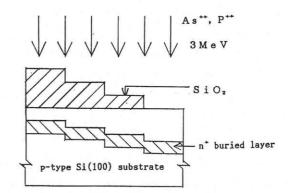

The formation method of various n<sup>+</sup> buried layers is shown in Fig. 1. Si dioxide film of various thickness (0, 0.2, 0.4,  $0.6\mu$ m) formed on the p-type Si substrate. As<sup>++</sup> or P<sup>++</sup> ions are implanted into the Si substrate through the varying thickness SiO<sub>2</sub> films. Using this process, various depth n<sup>+</sup> buried layers can be obtained at the same implantation condition and in the same wafer, because implanted ions lose energy while passing through varying thickness SiO<sub>2</sub> film. Acceleration energy is 3MeV. When the implanted ion is phosphorous, ion implanted depth are about 2.5, 2.3, 2.1, 1.9µm. The  $P^{++}$  ions' dose was  $7 \times 10^{14}$ /cm<sup>2</sup>. With this P<sup>++</sup> dose, the n<sup>+</sup> buried layer resistance is thought to be equal to that of conventional Si epitaxial substrates. When n<sup>+</sup> buried layers are formed by HEI<sup>2</sup> for bipolar transistors, leakage current problem exists in base-collector junctions. Therefore, annealing in N<sub>2</sub> atmosphere was performed before the oxidation process<sup>5)</sup>. Annealing temperature was 1000℃ and annealing time was 30min. Next, the poly-Si emitter bipolar transistor was fabricated by the conventional bipolar transistor's process. 3. Results and Discussion

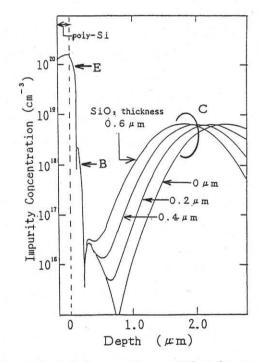

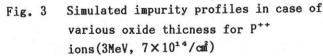

Simulated arsenic and phosphorous profiles before and after annealing (1000°C, 180min.) are depicted in Fig. 2. As shown in this figure, the phosphorous profile is deeper than that of arsenic. This result means that phosphorous ions are superior to arsenic ions in achieving large BV CEO value. Arsenic ions have a small diffusion constant, small  $R_P$  value and a large  $\Delta R_P$  value. 0n the other hand, phosphorous ions have a large diffusion constant value, large R<sub>P</sub> value, a small  $\Delta R_P$  value. In HEI<sup>2</sup>, since ion dispersion is very large, the impurity diffusion drive-force is very small. Therefore the Rp factor is most important in obtaining large BVCEO values. Simulated bipolar transistor impurity profiles are indicated in Fig. 3. The  $P^{++}$  ions dose is  $7 \times 10^{14}$ /cm<sup>2</sup>.  $R_P$  and  $\Delta R_P$ values of HEI<sup>2</sup> were used as the experimental values<sup>6)</sup>, and R<sub>P</sub> values were supposed to decrease by the same value as the oxide thickness. Fig. 4(a) indicates the relationship between collector current(Ic) and the applied voltage between collector and emitter( $V_{CE}$ ) for P<sup>++</sup> ions, Fig. 4(b) is for As<sup>++</sup> ions. In the case of As<sup>++</sup> ions, the dose is 1.7×10<sup>15</sup>/cm<sup>2</sup>. Both ions are directly implanted in the Si substrate not

Fig. 2 Simulated phosphorous and arsenic profiles before and after annealing (1000°C, 30min.)

passing through the SiO<sub>2</sub> film.

Figs. 4(a) and (b) reveal that the breakdown voltage between the emitter and collector in the case of  $P^{++}$  ions, is larger than the value in the case of  $As^{++}$  ions. This result is coincident with the result in

Fig. 4 Collector current versus collector-emitter voltage for (a) As<sup>++</sup> ions and (b) P<sup>++</sup> ions (emitter size : 1×3µm<sup>2</sup>)

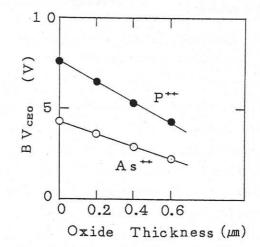

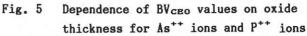

Fig. 2. The collector resistance(Rcs) values examined from Vce-Ic saturation region characteristics are 140  $\Omega$  in the case of P<sup>++</sup> ions and  $110\,\Omega$  in case of As<sup>++</sup> ions. These values are smaller than the  $R_{cs}$  value (180  $\Omega$ ) for bipolar transistors formed in conventional Si epitaxial substrates, the same process used with HEI<sup>2</sup>. The relationship between BVCEO values and oxide thickness is shown in Fig. 5. This result reveals that the BVCEO values are easily controlled by Si dioxide film thickness. This result also shows that BVCEO values decrease linearly as oxide thickness increases. The BVCEO maximum value was 7.8V for P<sup>++</sup> ions and 4.4V for As<sup>++</sup> ions. The base-collector leakage currents histogram for HEI<sup>2</sup> and the leakage currents histogram for conventional Si epitaxial substrate used as a reference, are shown in Fig. 6.

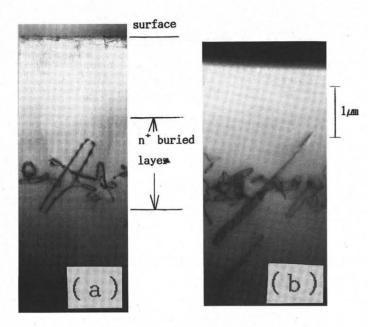

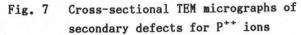

Measurement conditions of leakage currents are as follows. The base-collector junction area size is  $60\mu m \times 150\mu m$ , and the reverse bias value is 5V. This figure reveals that leakage current values for HEI<sup>2</sup> are less than 100pA in over 90% of measured devices. This rate is nearly the same as the conventional Si epitaxial substrate case. However, large leakage currents  $(30 \mu A)$  exists in the HEI<sup>2</sup> case. This large leakage

current value exceeds that of the epitaxial substrate (4.3nÅ), and the frequency is also a little larger. Cross-sectional TEM(XTEM) micrographs of the same sample as for the

HEI<sup>2</sup> leakage current measurement are shown in In Fig. 7, the n<sup>+</sup> buried layer de-Fig. 7. fined by the region in which phosphorous concentration is more than  $1 \times 10^{18}$ /cm<sup>2</sup> is also indicated. Secondary defects exist inside the n<sup>+</sup> buried layer for the most part (region(a)), as shown in Fig. 7. This result is thought to be the reason for the low leakage currents (below 100pA). That is, the base-collector depletion region does not reach the secondary defects buried in the n<sup>+</sup> On the other hand, a large buried layer. rod-like defect was also observed (region(b)). This defect almost reaches the front of the n<sup>+</sup> buried layer. This type of defect is considered to result in large leakage currents, as mentiond above. Therefore, it is necessary to eliminate these large rod-like defects to completely eliminate large leakage currents. Finally, remaining secondary defects are proved to be harmless, if they are deeply imbedded in the n<sup>+</sup> buried layer.

## 4. Conclusion

In conclusion, high-grade n<sup>+</sup> buried layers were confirmed to be made by 7×10<sup>14</sup>/cm<sup>2</sup> of P<sup>++</sup> ions implanted by 3MeV acceleration energy. The maximum BVCEO value obtained was 7.8V. This value is a practical value never before achieved. The collector resistance value can be less than Moreover, BVCEO values decreased 140Ω. linearly with oxide film thickness, when ions were implanted by high acceleration energy through various thickness Si dioxide film. Leakage currents of the base-collector junction were significantly decreased when thermal annealing (1000°C, 30min.) was performed in N<sub>2</sub> atmosphere. The method of HEI<sup>2</sup> described in this paper should be a very effective process for designing both BiCMOSand multi-function LSIs.

#### Acknowledgments

The authors would like to express their sincere thanks to Dr. M. Tamura and Mr. K. Ohyu for their useful discussions and also thanks to Dr. Y. Wada, Dr. N. Momma and Mr. K. Miyata for their guidance and encouragement.

### References

- 1) A. Watanabe et al. ; Tech. Dig. of IEDM pp.423-426 (1985)

- 2) J. F. Ziegler et al. ; IBM Tech. Disclosure Bull. 14, p1635 (1971)

- 3) M. Doken et al. ; Tech. Dig. of IEDM, p586 (1981)

- M. Takahashi et al. ; JJAP, Vol.20, No.11 November, pp.2205-2209 (1981)

- 5) M. Tamura et al. ; JJAP, Vol.25, No.6, June, pp.L474-L477 (1986)

- H. Wong et al. ; Nuclear Instruments and Methods in Physics Research (1987)

- 7) Y. Kobayashi et al.; Tech. Dig. of IEDM pp.802-804 (1986)