Extended Abstracts of the 20th (1988 International) Conference on Solid State Devices and Materials, Tokyo, 1988, pp. 613-614

LA-6-4

# A Novel Device Structure for Latch-up Free VLSI CMOS Circuits

# W. Pribyl, W. Reczek Siemens AG., Components Group Otto-Hahn-Ring 6, D-8000 Munich 83, FRG

Abstract: A new concept, where well- and substrate- contacts are replaced by diodes, provides latch-up free CMOS circuit operation without degrading the MOS device parameters. For the 4 Megabit 0.9  $\mu$ m n-well bulk CMOS technology with VBB-generator, the well contact is substituted by a buried poly-Si diode. Compared to conventional CMOS, no additional area is needed.

#### 1. Theory of Operation

Many concepts have been presented in the past that claimed to provide latch-up free CMOS circuits. But a high price had to be paid; i.e. expensive (epilayer [1]) and complicated (Schottky PMOS [2]) technologies or increased die size (additional guardrings [3], other design measures [4]). A new idea [5], combining the good static latch-up hardness of floating well concepts [4] and the low transient latch-up suszeptibility of conventional CMOS leads to a simple unique solution without degrading MOS device performance. The principle of operation is discussed in detail in [5].

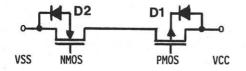

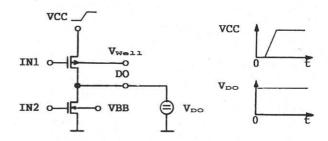

Fig.1a shows the cross section of this new CMOS structure. If compared to conventional CMOS, no additional area is needed for this structure. Fig.1b shows the equivalent circuit of a CMOS stage, where the substrate and well contacts are replaced by diodes. The n-well (or n-substrate) of the PMOS device is connected with the cathode of diode D1 to VCC. The p-substrate (or p-well) of the NMOS device is connected with the anode of diode D2 to VSS. There is no significant increase of substrate and well shunt resistances. The MOS device performance is not degraded.

In the case of power-on, majority carriers only can flow out of the well and out of the substrate. Proper biasing of well and substrate is achieved by threshold voltages of the additional diodes lower than the threshold voltages of the parasitic  $p^n$  and  $n^p$  diodes.

Under static conditions only the small leakage current of the p-n junctions will act as a base current for the parasitic bipolar transistors.

## Technology and Diode Device Features

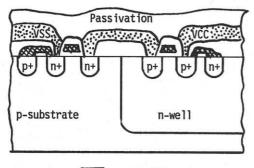

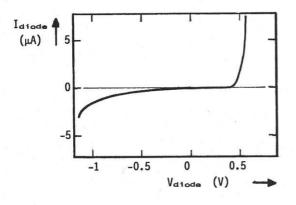

Basis for the new device structure is the 4M DRAM  $0.9\mu m$ n-well CMOS technology [6]. In p<sup>+</sup> regions (p<sup>+</sup> source/drain of the p-channel MOS) the outdiffusion of As out of the As doped poly-Si forms a n<sup>+</sup>p<sup>+</sup> junction. Fig.2 shows a microphotograph of a cross section of the new poly-Si diode. The n<sup>+</sup> outdiffusion is 0.1 $\mu m$  into the 0.6 $\mu m$  deep p<sup>+</sup> diffusion region. Fig.3 shows the I/V characteristics of the device.

#### Latch-up Measurements

The latch-up hardness of the new concept using poly-Si diodes is compared to conventional CMOS and floating well CMOS.

#### 3.1 Static Latch-up Behaviour

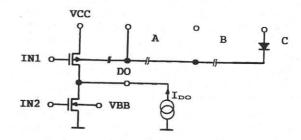

To characterize the static latch-up behaviour of the CMOS stage (VCC=5V; Fig.4; results in Tab.1) a current is forced into the output pin. The PMOS and NMOS are in the OFF state. For positive currents at the output pin, the conventional CMOS structure latches at VCC+0.7V ( $V_{DO}$ =5.7V) at a trigger

current of only  $I_{\rm DO}{=}8mA$ . The floating well concept and the new concept with the poly-Si diode are latch-up free for voltages  $V_{\rm DO}{=}8V$ . For negative currents at the output pin, all 3 concepts are latch-up free because of the use of a VBB-generator. The trigger currents  $I_{\rm DO}$  are greater than 100mA at a trigger voltage  $V_{\rm DO}{=}-3.4V$ .

#### 3.2 Transient Latch-up Behaviour

The power-on latch-up hardness is investigated with a VCC=7V/2ns ramp rate and a DC voltage source at the DO pin (Fig.5; results Tab.2). The power-on latch-up hardness of the conventional CMOS stage is taken as a reference. The floating well concept offers some advantages for positive DC voltages at the DO pin while for negative voltages  $V_{DO}$  the latch-up hardness is worse. A real improvement is obtained for the stage with the poly-Si diode, where the structure is latch-up free for voltages  $V_{DO} \approx -1V$  and  $V_{DO} \approx 5.2 V$ .

#### 4. Conclusion

The new concept with poly diodes instead of conventional substrate and well contacts provides latch-up free CMOS circuits with additional benefits as easy layout and reduced die size if compared to guardring technologies. The fabrication of the poly-Si diodes can easily be implemented in the 4M DRAM 0.9µm n-well bulk CMOS process.

## Acknowledgements

The authors wish to thank G. Enders for his support in technology, Dr. E. Demm and B. Leibhard for their support in SEM analysis and H. Mulatz for packaging of the samples. This report is based on a project which has been supported by the Minister of Research and Technology of the Federal Republic of Germany under the support-no. NT 2696. For the contents the authors alone are responsible.

# References

- D.Estreich, PhD Dissertation, Stanford Univ., Techn. Rep. No. G-201-9 (1980).

- [2] E.Sangiorgy, S.Swirhun, IEEE Trans. Elect. Dev. Let., vol.EDL-5, no. 8 (1984), 293.

- [3] R.R.Troutman, IEEE Trans. Elect. Dev. Let., vol. EDL-4, no. 12 (1983), 438.

- [4] H.P.Zappe, R.K.Gupta, K.W.Terrill, C.Hu, Dig.Tech.Pap. IEDM 1985, Washington, DC, 517.

- [5] W.Pribyl, J.Harter, W.Reczek, D.Sommer, H. Häusele, to be published in JSSC June 1986.

- [6] K.H.Küsters, G.Enders, W.Meyberg, H.Benzinger, B.Hasler, G.Higelin, S.Röhl, H.M.Mühlhoff, W.Müller, Proc. of the 1987 Symp.on VLSI Technology, Nagano, Japan, 93.

- 856006 25KV X20.0K 1.5Aum

- Fig.2: SEM Microphotograph of the poly-Si diode (Cross section).

Fig.1: CMOS output stage with additional diodes.Cross section a.) and equivalent circuit b.) of the proposed structure with poly-Si diodes instead of substrate and well contacts.

Fig.3: I/V characteristics of the poly-Si diode.

| buffer design                        | trigger current/voltage                                  |

|--------------------------------------|----------------------------------------------------------|

| A well on VCC=con-<br>ventional CMOS | +8mA / 5.7V<br>no LU at -100mA / -3.4V                   |

| B floating well                      | no LU at V > 8V<br>no LU at -100mA / -3.4V               |

| C poly-Si diode                      | no LU at V <sub>DO</sub> > 8V<br>no LU at -100mA / -3.4V |

Tab.1: DC latch-up trigger currents/voltages for different CMOS buffers. W/L=400μm/1.1μm and W/L=600μm/1.1μm for NMOST and PMOST, respectively. VCC = 5 V, LU = latch-up. Fig.4: Measurement setup for static (DC) latch-up characterization.

Fig.5: Measurement setup for power-on latch-up characterization (worst case condition).

| buffer design                        | voltage on DO pin |

|--------------------------------------|-------------------|

| A well on VCC=con-<br>ventional CMOS | ≤ -0.34V ≥ +1.7V  |

| B floating well                      | ≤ -0.29V > 8V     |

| C poly-Si diode                      | ≤ -1V ≥ +5.2V     |

Tab.2: Power-on latch-up trigger currents/voltages for different CMOS buffers.W/L=400µm/1.1µm and W/L=600µm/1.1µm for NMOST and PMOST, respectively. Ramp rate VCC=7V/2ns, LU=latch-up.