Extended Abstracts of the 20th (1988 International) Conference on Solid State Devices and Materials, Tokyo, 1988, pp. 605-606

## LB-2-3

## A High Speed 1-kbit Variable Threshold Josephson RAM Chip

## Itaru KUROSAWA, Hiroshi NAKAGAWA, Shin KOSAKA, Masahiro AOYAGI, and Susumu TAKADA Electrotechnical Laboratory 1-1-4 Umezono, Tsukuba-shi, Ibaraki 305

This paper reports a high speed 1-kbit Josephson RAM(Random Access Memory) chip integrating variable threshold memory cells[1].

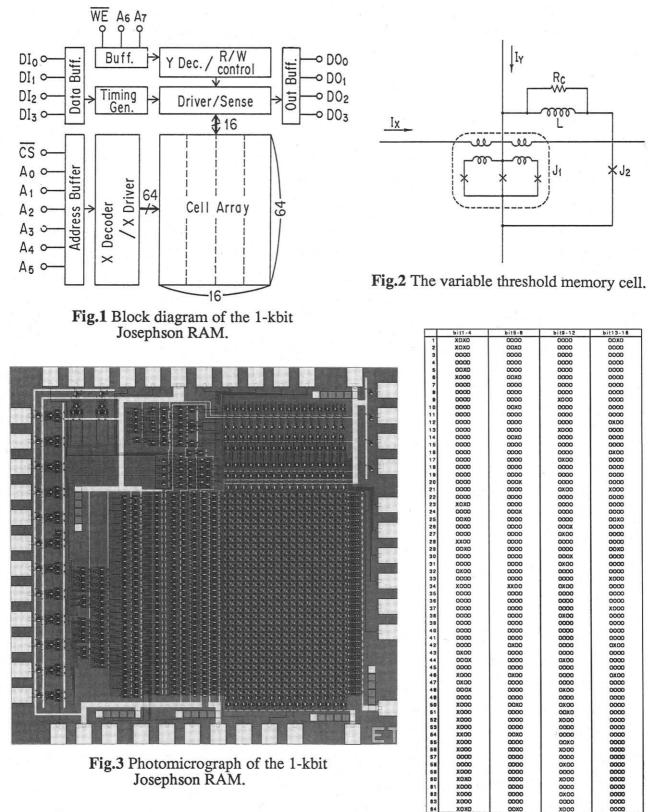

A block diagram of a 256 x 4-bit(1-kbit) RAM is shown in Fig.1. The memory plane is organized into four blocks, each with 64 rows and 4 columns. The variable threshold memory cell which has been proposed and investigated[2] has an equivalent circuit of asymmetric dc SQUID(Superconducting Quantum Interference Device) as shown in Fig.2. The cell has a simple structure in comparison with other Josephson memory cells. The present cell is two times smaller than the conventional ones[3,4,5]. This is very important to achieve a high performance Josephson memory, not only for the storage capacity but also for the access time.

The address decoder circuit consists of OR-gates and INVERT-gates, instead of AND-gate used in the conventional one. Therefore this circuitry gives a small area and a fast operating speed. One column is driven by a pair of set-reset gates with a feedback signal from the sense gate to achieve an NDRO(Non-Destructive Read Out) operation. By introducing a two phase unipolar power supply it is realized to operate the RAM chip in a pipe-line way which makes the cycle time shorter than that in a single phase or a dc power supply systems. All of the inputs are set in the active cycles of the power of phase 1 before the power of phase 2 rises up. The positive and the negative signals are made at the input buffer gates. These all peripheral circuits consist of a 4JL-gate family[6].

A photomicrograph of the 1-kbit RAM is shown in Fig.3. The chip has been fabricated based on the Nb/Al-oxide/Nb junction technology with 3-µm design rule[7]. The cell size is 30µm x 72µm. Whole circuits are integrated in an area of 3.3mm square on the chip.

All operating function tests were carried out in liquid He. Figure 4 shows a result of repeatable operations of write"1", read, write"0" and read sequence for all bits. Marks"o" in the figure show correct-responding bits to the sequential operation. "x" indicates the location of the cell which responds incorrectly. More than 90% of the cells showed their right response. From high speed measurements, the critical delay time of the decoder and the memory plane were obtained to be 150ps and 350ps, respectively.

[3]M.Yamamoto et al., IEEE Electron Device Lett., EDL-4, p150(1983).

[6]S.Takada et al., Jpn.J.Appl.Phys., 19, Suppl.1, p607(1980).

<sup>[1]</sup>I.Kurosawa et al., Appl. Phys. Lett. 43, p1067(1983); 44, p567(1984).

<sup>[2]</sup>I.Kurosawa et al., Ext. Abst. 16th SSDM, p619(1984).

<sup>[4]</sup>W.H.Henkels et al., J.Appl.Phys., 58, p2371(1985). [5]Y.Wada et al., 1988 ISSCC Digest Technical Papers, p84(1988).

## [7]H.Nakagawa et al., Jpn.J. Appl. Phys., 25, pL70(1985).

Fig.3 Photomicrograph of the 1-kbit Josephson RAM.

Fig.4 Error bit map measured on the 1-kbit RAM chip.