Extended Abstracts of the 21st Conference on Solid State Devices and Materials, Tokyo, 1989, pp. 97-100

# A-6-2

# An 8 nm-thick Polysilicon MOS Transistor and Its Thin Film Effects

T.Hashimoto , T.Kobayashi , T.Mine , T.Yamanaka , N.Hashimoto A.Shimizu\* , T.Nishida and Y.Kawamoto

Central Research Laboratory, Hitachi Ltd., Kokubunji, Tokyo 185, JAPAN \*Hitachi VLSI Engineering Corp., Tokyo JAPAN

Submicron p-channel polysilicon MOS transistors have been fabricated in a ultra-thin polysilicon film. These devices show excellent characteristics due to thin film effects in off-current, subthreshold slope and punchthrough resistance. A key fabrication technology is the formation of continuous polysilicon film less than 10nm-thick.

In LPCVD silicon deposition the nucleus density on CVD  $SiO_2$  is found to be higher than that on thermal  $SiO_2$ . An 8nm-thick continuous silicon film is formed on CVD  $SiO_2$  for polysilicon MOS transistor.

# INTRODUCTION

In recent years, there have been many reports on polysilicon MOS transistors (poly-Si MOS) for application to VLSI[1,2]. We have already reported a new type of memory cell with a poly-Si p-channel MOS load and a cross -coupled capacitor for high packing density SRAM[3]. This cell has many advantages, reduction in stand -by power, as such improvement of retention characteristics and soft error immunity. In order to achieve them, a high on/off current ratio is demanded for poly-Si pMOS load[4].

There have been several reports on increase of grain size more than  $1 \mu$  m by recrystallization of Si films, which are amorphized by Si<sup>+</sup> ion implantation [5]. They have reported high on-current (IoN) because of the film's high field mobility. Furthermore, the benefits of a thin poly-Si film have been proposed to accomplish low off-current(IOFF). However, there is a limit to deposit a thin using a conventional LPCVD poly-Si film technique, because a Si film has an island the initial stage of the structure in deposition.

То overcome this problem, new а technology has been developed to obtain continuous Si film less than 10nm-thick. The device fabricated in this film showed not only low IOFF but also excellent performances in other areas. In this report we describe the poly-Si deposition technology and the electrical characteristics of the poly-Si MOS transistor.

#### EXPERIMENTAL

### 1. Formation and observation of Si film

Si films were deposited on insulators on Si wafers in a conventional LPCVD reactor. The flow rate of SiH<sub>4</sub> as a source gas was fixed at 60sccm. Total pressure in the reactor was 106Pa and temperature was 515~630°C.

The surface morphology of the Si films was inspected by scanning electron microscopy (SEM). The uniformity and the thickness of the ultra-thin Si films were verified using transmission electron microscopy(TEM).

#### 2. Device structure and fabrication

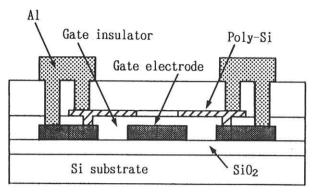

A schematic cross-section of the poly-Si pMOS is shown in Fig.1. It has so-called under-gate structure. A 100nm-thick poly-Si film was deposited at 620°C by LPCVD on a

Fig.1 Schematic cross-section of the poly-Si p-channel MOSFET

100nm-thick thermally grown SiO<sub>2</sub>. BF<sub>2</sub><sup>+</sup> ion implantation and RIE were carried out to form a gate electrode. Then a 22~36nm-thick gate oxide was deposited using a reaction of SiH4 and N<sub>2</sub>O at 800°C. An 8~38nm-thick Si film was deposited at 530°C. When device isolation was accomplished, BF2<sup>+</sup> at a dose of 2E14cm<sup>-2</sup> was implanted in the source/drain regions. After a 100nm-thick CVD SiO<sub>2</sub> and a 350nm-thick boro-phospho-silicate glass (BPSG) film were deposited as an inter-layer, annealing was carried out at 900°C in N2 for 30min. After contact hole delineation, an Al-Si film was deposited. patterned and sintered at 450°C in H2. A 500nm-thick PSG film or plasmadeposited Si<sub>3</sub>N<sub>4</sub> film was then formed as encapsulation layer, hydrogen passivation was achieved by subsequent annealing at 450°C in N2.

### RESULTS AND DISCUSSIONS

### 1. Formation of ultra-thin poly-Si film

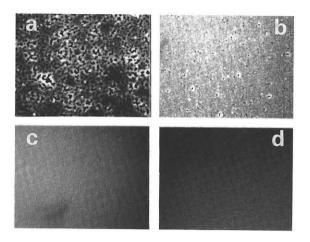

Figure 2 shows SEM micrographs of Si films on thermal SiO<sub>2</sub> at different deposition times. In the initial stage we can find that the film has an island structure. The film thickness must be more than 30nm to form a continuous film in this condition. This phenomenon is explicable by the following deposition mechanism. the initial stage In nucleations occurred in small clusters on the insulator at a certain probability. As time progresses these nuclei grow and coalesce. Finally a continuous film is formed which then thickens.

According to this deposition mechanism, a

Fig.2 SEM micrographs of Si film surface at different deposition times Films were deposited at 520°C on thermal SiO<sub>2</sub>. a)20min b)30min c)40min d)60min

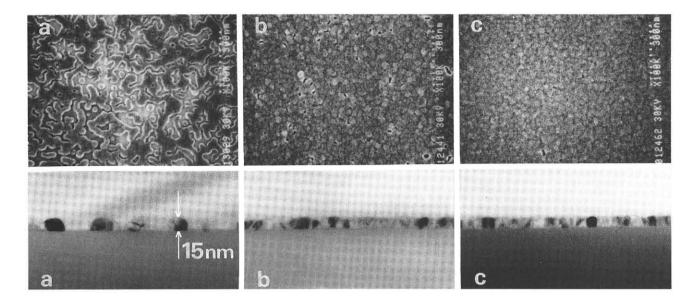

thinner continuous film can be obtained by increasing the nucleus density. We think that nucleus density strongly depends on the substrate insulator. Thus we investigated the surface morphology in the initial stage of deposition on different insulators: thermal SiO<sub>2</sub>, CVD SiO<sub>2</sub> and CVD Si<sub>3</sub>N<sub>4</sub>. Deposition temperature was 630°C. These results are shown in Fig.3. Obviously nucleus density on the CVD insulators is higher than that on thermal SiO<sub>2</sub>. On thermal SiO<sub>2</sub>, the film has an island structure and the height of each island being about 15nm. However, on the CVD SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub>, films of the same thickness are almost continuous. Furthermore, deposition temperature also influences nucleus density. We can obtain an 8nm-thick continuous film by decreasing the deposition temperature from 630° to 530°. For poly-Si pMOS with an undergate structure, the CVD insulator can be used as a gate insulator. The CVD SiO<sub>2</sub> film is chosen because of its good properties as a gate insulator.

### 2. Device characteristics

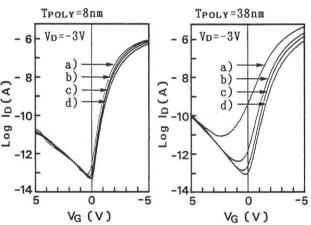

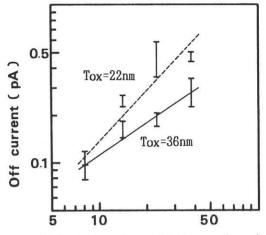

Figure 4 shows subthreshold characteristics of poly-Si pMOS with several channel lengths for two different poly-Si thickness. Figure 5 shows IOFF as a function of poly-Si thickness. IOFF decreases with poly-Si thickness. IOFF is considered as generation current at the

Fig.3 SEM(upper) and TEM(lower) micrographs of Si films deposited on a)thermal SiO<sub>2</sub>, b)CVD SiO<sub>2</sub>, c)CVD Si<sub>3</sub>N<sub>4</sub> Films were deposited at 630°C for 2min.

drain p -n junction [6]. Junction area increases with poly-Si thickness. An 8nm thick poly-Si pMOS has sufficiently small IoFF. A typical IOFF (at VD=-3.5V,VG=0V) is as low as 0.04pA shown in Fig.4, which corresponds to 0.16  $\mu$ A stand-by current for 4-Mbit SRAM.

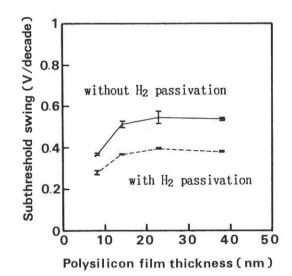

Figure 6 shows subthreshold swing (S) as a function of poly-Si thickness. The decrease in S factor is very important, because Ion is determined mainly by S factor. By thinning the poly-Si film from 38nm to 8nm, S factor decreased from 0.54V / decade is to 0.37V / decade without hydrogen passivation. which results in the increase of Ion (at  $V_{D} = V_{G} = -4V$ ) approximately five times. A similar improvement is observed in a single crystalline Si SOI MOSFET [7]. It is observed 100nm critical thickness. about while at about 10nm-thick is critical for a poly-Si MOS.

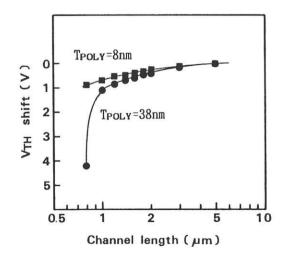

$\Delta V_{TH}$  as a function of Figure 7 shows Short channel effect is channel length. suppressed by reducing the poly-Si thickness. This result seems the same as the thin film effect in single Si SOI pointed out in ref. [8]. 8nm -thick poly -Si pMOS do not show An punchthrough even if channel length is  $0.8 \,\mu$  m,

Fig. 4 Subthreshold characteristics of p-channel MOSFETs for different channel lengths a)0.8 μm, b)1.0 μm, c)1.2 μm, d)1.6 μm

while a 38nm-thick device shows increase of IOFF due to punchthrough at the same condition. Therefore this ultra-thin Si film is quite attractive for future three-dimensional SRAM cells.

#### CONCLUSION

We have achieved a high performance poly-Si pMOS which has low Ioff, sharp subthreshold slope and high punchthrough

Polysilicon film thickness (nm)

Fig.5 Off current vs. poly-Si film thickness L/W=1.6/0.6(μm), VD=-3.5V

Fig.6 Subthreshold swing vs. poly-Si film thickness L/W=1.6/0.6(μm), VD=-0.1V

Fig.7 VTH shift(ΔVTH) dependence on channel length ΔVTH=VTH(L=5μm)-VTH(L=L)

resistance by using an ultra-thin poly-Si film less than 10nm. This film is obtained by using CVD SiO<sub>2</sub> as a substrate insulator on which nucleus density is higher than that on thermal SiO<sub>2</sub>.

Thus, the proposed poly-Si pMOS shows excellent performances and high potential for future high packing density SRAM cells using deep submicron technology.

### ACKNOWLEDGEMENTS

The authors would like to thank Drs. E. Takeda and K. Shimohigashi for their encouragement and support throughout this work.

In addition, credit is due to T. Shimotsu and H. Kakibayashi for TEM observation, to S. Nakagawa for SEM observation and K.Sasaki and to K.Ishibashi for useful discussions.

Special thanks are also due to Dr. K. Yagi for his continuous encouragement.

REFERENCES

- [1]S. D. S. Malhi, H. Shichijo, S. K. Banerjee, R. Sundaresan, M. Elahy, G. P. Pollack, W. F. Richardson, A. H. Shah, L. R. Hite, R. H. Womack, P. K. Chatterjee and H. W. Lam; IEEE J. Solid-state Circuits, vol. sc-20(1985) 178.

- [2]M. Ando, T. Okazawa, H. Furuta, M. Ohkawa, J. Monden, N. Kodama, K. Abe, H. Ishihara and I. Sasaki; Symposium on VLSI Circuits (1988)49.

- [3]T.Ymanaka, T.Hashimoto, N.Hashimoto, T.Nishida, A.Shimizu, K.Ishibashi, Y.Sakai, K.Shimohigashi and E.Takeda; IEDM Tech. Dig. (1988)48.

- [4]K. Ishibashi, T. Yamanaka and K. Shimohigashi; Symposium on VLSI Circuits(1989)29.

- [5]T.Ohshima, M.Negishi, H.Hayashi, T.Noguchi and A.Mizumura; IEDM Tech. Dig. (1986)196.

- [6]J.G.Fossum, A.Ortiz-Conde, H.Shichijo and S.K.Banerjee; IEEE Trans. Electron Devices, vol. ED-32(1985)1878.

- [7]J.P.Colinge ; IEEE Electron Device Letters, vol.EDL-7(1986)244.

- [8]T. Sekigawa and Y. Hayashi ; Solid-state Electron vol. 27(1984)827.