## MOS Characteristics and Reliability of Thin Gate Dielectrics Grown by Rapid Thermal Processing in O<sub>2</sub> Diluted with NF<sub>3</sub>

G. Q. Lo, W. Ting, D. L. Kwong, J. Kuehne\* and C. W. Magee\*\*

Microelectronics Research Center, The University of Texas at Austin, \*Texas Instrument Inc., \*\*Evans East Inc.

High quality ultrathin fluorinated gate oxides by rapid thermal processing in diluted NF<sub>3</sub> and O<sub>2</sub> have been fabricated and characterized. Fluorinated oxides with small amounts of F show less interface state generation under F-N injection, whereas excessive F incorporation deteriorates the interfacial resistance. Increased hole trap density in fluorinated oxides was also observed. In addition to passivating Si dangling bonds, F is speculated to create nonbridging oxygen centers and/or oxygen deficiencies and enhances positive charge trapping during hot-electron injection.

Recently it was found that by incorporating small amounts of F into SiO2, the MOS device properties could be greatly affected.<sup>1-7</sup>) Various techniques have been proposed and studied, including rinsing Si substrates in HF solution prior to oxidation,<sup>1,2</sup>) F ion-implantation into poly-Si gate followed by drive-in, 3-6) and furnace oxidation in an  $O_2 + NF_3$  mixture.<sup>7</sup>) Proper amounts of fluorine in the oxide was found to suppress hot-electron induced interfacial degradation and enhance radiation hardness, while excessive F incorporation exhibited detrimental effects.<sup>3,4)</sup> In order to precisely control oxide thickness (< 10 nm) and F incorporation, rapid thermal processing (RTP) is the most promising candidate since both the NF3 purging time and oxidation time can be accurately controlled and a low thermal budget is also maintained. As a consequence, RTP is applied in this study to prepare high-quality ultrathin (~10 nm) fluorinated  $SiO_2$  suitable for MOS device applications. The Si substrate temperature and the NF3 flux were used as switches to turn the surface reaction on or off. Precise and selective F incorporation can be achieved thereby.

The substrates used were (100) oriented Ptype Si wafers with a resistivity of 1-2  $\Omega \cdot cm$ . The control oxide was grown by RTO at 1050 °C in pure  $O_2$  for 60 s. Two groups of samples were prepared. In the first group, wafers received rapid thermal annealing (RTA) in diluted NF3 (100 ppm in N<sub>2</sub>) prior to gate oxidation with durations from 10 to 40 s at 900 °C followed by an in-situ RTO in pure oxygen at 1050 °C for 60 s. In the second group, diluted NF3 was added to pure O2 during the 1050 °C, 60 s RTO with NF3 flowing durations from 10 to 60 s. MOS capacitors were fabricated using standard poly-Si gate technology after gate oxide preparation.

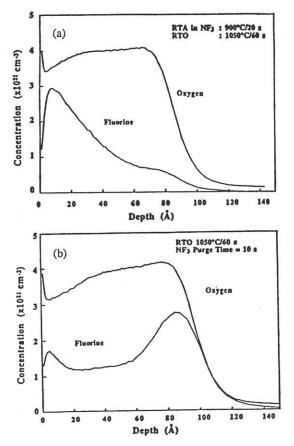

Secondary ion-mass spectrometry (SIMS) was applied to investigate F distribution in the oxide. Fluorine pile-up at the oxide surface was observed with the concentration decreasing toward the  $Si/SiO_2$  interface in the sample received RTA in NF<sub>3</sub> at 900 °C for 20 s before RTO, , as shown in Fig. 1 (a). We believe a significant amount of fluorine is adsorbed on the surface during RTA in NF<sub>3</sub> due to the high temperature and is subsequently incorporated into the oxide during gate oxidation. This process is similar to rinsing wafers in HF before

gate oxidation. On the other hand, fluorine pileup at both the oxide surface and the Si/SiO2 interface was observed in the sample grown in O2/NF3 with NF3 purging for 10 s during a 60 s RTO, as shown in Fig. 1 (b). From these profiles, demonstrated we have that significantly different F distributions can be obtained by using different techniques to introduce fluorine. It is also interesting to note that no detectable amount of nitrogen was found in any of the fluorinated samples and, contrary to the work of Nishioka et al.,2) only small amount of <sup>47</sup>SiF was detected in all samples.

Fig. 1 SIMS depth profiles of O and F obtained from (a) sample rapid thermal annealed in NF<sub>3</sub> at 900°C for 20 s before RTO and (b) sample having NF<sub>3</sub> purging during the first 10 s of RTO. RTO was performed at 1050 °C for 60 s.

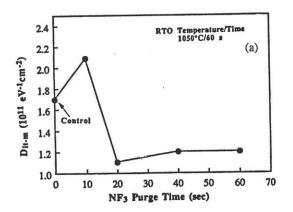

The interface state densities  $(D_{it})$  measured by the high-low frequency C-V technique on fresh capacitors are summarized in Fig. 2 (a) and (b) as a function of NF<sub>3</sub> purging time during RTO, and RTA duration in NF<sub>3</sub> prior to RTO, respectively. In Fig. 2 (a),  $D_{it}$  decreases as the purge time increases except for the sample which had the shortest, i. e. 10 s of purging.  $D_{it}$ in Fig. 2 (b) decreases monotonically with increasing RTA time in NF<sub>3</sub>. Nishioka *et al.* suggested that the reduction of  $D_{it}$  by NF<sub>3</sub> treatment is due to F tying to the Si-dangling bonds which cannot be terminated by H.<sup>3</sup>)

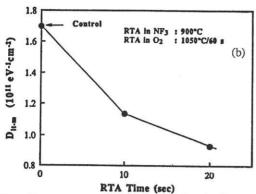

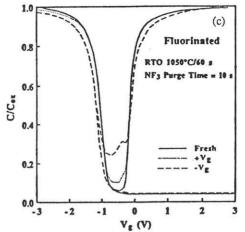

Fig. 3 shows the high- and low-frequency C-V characteristics of MOS capacitors with (a) control oxide, (b) fluorinated oxide prepared with NF<sub>3</sub> purging during RTO, and (c) fluorinated oxide prepared with RTA in NF3 prior to RTO. Curves obtained from devices before and after F-N electron injection are both presented. In Fig. 3 (b), the quasi-static C-V after electron injection from both curves polarities are less distorted than either Fig. 3 (a) or (c), indicating an enhanced resistance to Dit generation. In addition, the shift of highfrequency C-V curve after stressing in Fig. 3 (b) is the least, especially when electrons are injected from the substrate where no shift is observed. The sample which received RTA in NF3 prior to RTO, on the other hand, exhibited deteriorated resistance to D<sub>it</sub> generation and increased  $\Delta V_{fb}$  as compared with the control Referring to Fig. 1 (a) and (b), the oxide. devices shown in Fig. 3 (b) and (c) have very different F distributions, and it is clear that the hot-electron hardness is improved by proper amounts of F at the Si/SiO2 interface instead of at the SiO<sub>2</sub>/gate interface.

Fig. 2  $D_{it}$  measured from fresh devices as a function of (a) NF<sub>3</sub> purge time during RTO and (b) RTA duration in NF<sub>3</sub> before RTO.

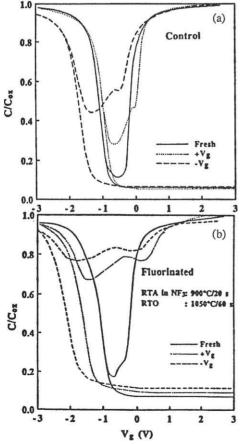

The dependence of hot-electron resistance on NF<sub>3</sub> purge time was also studied and shown in Fig. 4 (a) and (b). All devices were subjected to electron injection to a total fluence of 5 x  $10^{-3}$ C/cm<sup>2</sup>. As compared with the control oxide, the sample which received 10 s of NF<sub>3</sub> purge during RTO showed less D<sub>it</sub> generation while longer purges degraded the hardness. On the other hand, the pre-oxidation RTA in NF<sub>3</sub> for 20 s obviously degraded the hot-electron resistance, similar to the observation from Fig. 3.

Fig. 3 High- and low-frequency C-V curves measured from MOS capacitors before and after a 300 s constant current stressing. The stress current density was 17  $\mu$ A/cm<sup>2</sup>. (a) control oxide, (b) fluorinated oxide with NF<sub>3</sub> purging during the first 10 s of RTO, and (c) fluorinated oxide formed by RTA in NF<sub>3</sub> at 900 °C for 20 s followed by RTO.

Fig. 4  $D_{it}$  as a function of surface potential after F-N electron injection with NF<sub>3</sub> purge time as a parameter: (a) positive gate bias (b) negative gate bias. Control and fluorinated oxide with RTA in NF<sub>3</sub> at 900°C for 20 s before RTO (labeled

5) are also included. Labels from 1 to 4 represent  $NF_3$  purge time of 10, 20, 40, and 60 s, respectively.

The charge trapping properties of fluorinated oxides under F-N electron injection were also investigated and shown in Fig. 5 in which  $\Delta V_{fb}$  is plotted against NF<sub>3</sub> purge time during RTO. Negative  $\Delta V_{fb}$  was observed in all samples under negative gate bias which indicates positive charge trapping. For pure oxide the negative  $\Delta V_{fb}$  is attributed to donortype slow interface state generation and/or trapped holes.8,9) The sample which received 10 s NF3 purge during RTO showed reduced positive charge trapping compared with control oxide, as indicated by a less negative  $\Delta V_{fb}$ . Prolonged NF<sub>3</sub> purge, on the other hand, enhances hole trapping. Similar behavior was observed under positive gate bias. The increased hole trap density is speculated to arise from defects such as oxygen deficiency resulted from F incorporation. Similar explanation was proposed for lightly nitrided SiO<sub>2</sub> films.<sup>10)</sup> The positive charge enhanced generation in fluorinated oxides due to irradiation has also been reported in which the creation of nonbridging oxygen or E' centers was suggested.11)

Fig. 5  $\Delta V_{fb}$  after F-N electron injection in fluorinated oxide as a function of NF<sub>3</sub> purge time: (a) positive gate bias and (b) negative gate bias. Control oxide and oxide with RTA in NF<sub>3</sub> at 900°C for 20 s before RTO are also included.

In conclusion, MOS characteristics of ultrathin oxides received different rapid thermal treatment in  $O_2$  and  $NF_3$  have been studied. The presence of  $NF_3$  during RTO was found to reduce initial interface density. Process dependence of  $\Delta V_{fb}$  and  $\Delta D_{it}$  has been studied and the physical mechanisms have been discussed.

This work was supported by SRC/SEMATECH and Texas Advanced Technology Program.

## References

- Y. Nishioka, E. F. Da Silva, Jr., Y. Wang and T.-P.Ma: IEEE Electron Device Lett. 9 (1988) 38.

- Y. Nishioka, Y. Ohji, K. Mukai, T. Sugano, Y. Wang and T. P. Ma: Appl. Phys. Lett. 54 (1989) 1127.

- Y. Nishioka, K. Ohyu, Y. Ohji, N. Natuaki, K. Mukai and T. P. Ma: IEEE Electron Device Lett. 10 (1989) 141.

- Y. Nishioka, K. Ohyu, Y. Ohji and T. P. Ma: IEEE Electron Device Lett. 10 (1989) 540.

- P. J. Wright and K. C. Saraswat: IEEE Trans. Electron Devices 36 (1989) 879.

- P. J. Wright, N. Kasai, S. Inoue and K. C. Saraswat: IEEE Electron Device Lett. 10 (1989) 347.

- E. F. da Silva, Jr., Y. Wang and T. P. Ma: IEDM Tech. Dig. (1987) 848.

- S. K. Lai and D. R. Young: J. Appl. Phys. 52 (1981) 6231.

- M. S. Liang, Y. T. Yeow, C. Chang, C. Hu and R. W. Brodersen: IEDM Tech. Dig. (1982) 50.

- M. Severi, L. Dori, M. Impronta and S. Guerri: IEEE Trans. Electron Devices 36 (1989) 2447

- 11)Y. Nishioka, K. Ohyu, Y. Ohji, M. Kato, E. F. da Silva and T. P. Ma: IEEE Trans. Nucl. Sci. 36 (1989) 2116.