Extended Abstracts of the 22nd (1990 International) Conference on Solid State Devices and Materials, Sendai, 1990, pp. 1023-1026

## Top-Gate Amorphous-Silicon Thin-Film Transistors Produced by CVD Method

Hiroshi Kanoh, Masahiro Yasukawa, Osamu Sugiura, Paul A. Breddels<sup>\*</sup> and Masakiyo Matsumura

Department of Physical Electronics, Tokyo Institute of Technology (\*On leave of absence from Philips Research Lab., The Netherlands)

O-okayama, Meguro-ku, Tokyo 152, Japan

Chemical-vapor-deposited (CVD) amorphous-silicon films have been applied as the active layers in thin-film transistors with top-gate structure, for the first time. The maximum field-effect mobility and the typical on/off current-ratio were more than  $0.5 \text{cm}^2/\text{Vs}$  and  $10^7$ , respectively. The characteristics were better than the ones based on plasma-CVD.

### 1. Introduction

Amorphous-silicon thin-film transistors  $(a-Si \ TFTs)$  have been extensively investigated for applying them into largearea flat-panel displays<sup>1)</sup>. Displays with more than  $10^6$  pixels have been formed on a 14''-diagonal glass substrate. Although the present a-Si TFTs are formed by using plasma-CVD method<sup>2)</sup> and have a bottom-gate structure<sup>3)</sup>, it becomes clear that the device structure and the processing technology should be improved for denser and larger displays with reasonable production cost.

We have investigated a new a-Si deposition method<sup>4</sup>) by using a higher silane and demonstrated that good a-Si TFTs can be formed on glass substrate<sup>5</sup>) by using a totally plasma-free (CVD) method.

This paper shows that the CVD method can also be applied to a top-gate structure which has the following advantages : Firstly, the top-gate TFTs can be produced by only 2 photomasks<sup>6</sup>). Secondly, the gate bus-line can be sufficiently thick, resulting in a small bus-line resistance. Thirdly, high mobility poly-silicon TFTs can be easily formed for peripheral circuits<sup>7</sup>) together with a-Si TFTs in a matrix.

# 2. Formation of Thermally Stable Source and Drain Electrodes

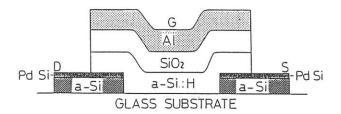

A schematic cross sectional view is shown in Fig. 1 for the top-gate TFT under study. In order to form a good MIS interface, the source and drain electrodes should be formed before depositing the active a-Si layer. Since the CVD temperature of a-Si is more than  $400^{\circ}$ C, Al can not be used as source and drain electrodes due to degradation of TFT characteristics by alloying of a-Si with Al. It has been reported<sup>8</sup>) that many metals make alloy with

Fig.1 Schematic cross sectional view of the top-gate TFT under study.

single-crystal silicon at less than several hundred <sup>O</sup>C and that a-Si is chemically more active than single-crystal silicon<sup>9)</sup>. Thus, pure metals will not be sufficiently stable for the source and drain.

We have used silicon-rich silicide for the source and drain because there remain no active metal molecules in this silicide. Palladium silicide was selected among many kinds of silicides since it can be formed at low temperatures and it is thermally stable.

Table I Process Flow of Palladium Silicide Eledtrode

| (1) CVD of a-Si              | Si <sub>3</sub> H <sub>8</sub> : 54sccm<br>(diluted to 4% in Ar)<br>H <sub>2</sub> : 62.5sccm<br>P : 100Torr, T : 450 <sup>o</sup> C |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| (2) Pd Evaporation           | T : 150°C                                                                                                                            |

| (3) N <sub>2</sub> Annealing | N <sub>2</sub> : 200sccm<br>P <sup>2</sup> : 760Torr, T : 450°C                                                                      |

| (4) Pd Removing              |                                                                                                                                      |

| (5) N <sub>2</sub> Annealing | N <sub>2</sub> : 200sccm<br>P : 760Torr, T : 410 <sup>o</sup> C                                                                      |

Palladium silicide was formed by the process flow tabulated in Table I. A 50 nm thick a-Si layer was deposited by thermal CVD method using a Si<sub>3</sub>H<sub>8</sub>-H<sub>2</sub> gas mixture at 450°C. Next, a 20 nm thick Pd layer was evaporated by using an electron beam. After the silicide was formed by heating the samples up to 450°C in nitrogen ambient, the remaining Pd metal was removed by iodine. The Si-rich palladium silicide was, then, annealed again at 410°C in order to finish the chemical reaction completely. The sheet resistivity of the electrode was  $0.1\Omega/square.$

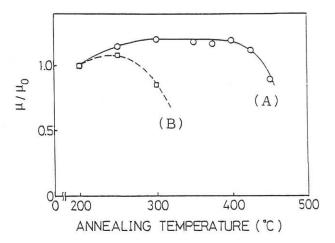

Thermally stable properties of the palladium silicide electrodes have been checked by a simple bottom-gate CVD a-Si TFT with thermal SiO<sub>2</sub> as a gate insulator and highly doped single-crystal Si substrate as the gate. The device has been heated in hydrogen ambient to various temperatures for 30 min. Hydrogen will remove from the film at temperatures more than 250°C and this will degradate device characteristics. In order to eliminate the change in characteristics caused by this dehydrogenation, the devices were annealed again in hydrogen ambient at lower temperatures. The temperature and time of this annealing were changed to the optimum conditions for the highest mobility. The field-effect mobility was evaluated under low drain voltage conditions.

The results are shown by the solid curve in Fig. 2. The mobility was normalized by the mobility value  $\mu_0$  before annealing.

Fig.2 Field-effect mobility of the bottomgate TFT as a function of the annealing temperature in hydrogen. The solid curve (A) is the palladium silicide TFT and the dashed curve (B) is the Aluminum TFT.

Characteristics of the bottom-gate TFT on the same chip but with Al electrodes on the CVD a-Si layer were also shown by the dashed curve for reference purpose. As can be seen the silicide TFT was not deteriorated in its performance at least until  $425^{\circ}$ C, while the mobility of the Al TFT started to be decreased at temperatures as low as  $250^{\circ}$ C. Thus, it was concluded that silicide electrodes were thermally stable until the deposition temperature of thermal-CVD a-Si ( $400^{\circ}$ C). It was observed that the surface of the silicide electrode was specular until  $400^{\circ}$ C, and began to be rough at more than  $450^{\circ}$ C.

3. Characteristics of The Top-Gate a-Si TFT

The top-gate TFT has been formed on a Corning 7059 glass substrate. After forming the silicide as the source and drain electrodes by the process flow listed in Table I, the a-Si and SiO<sub>2</sub> layers were deposited by the thermal CVD method using the process flow tabulated in Table II. The

Table II Process Flow of TFT

| (1) | Palladium Silicio        | le Forming & Patterning                                                                                                 |

|-----|--------------------------|-------------------------------------------------------------------------------------------------------------------------|

| (2) | CVD of a-Si              | Si <sub>3</sub> H <sub>8</sub> : 54sccm<br>(diluted to 4% in Ar)<br>H <sub>2</sub> : 62.5sccm<br>P : 100Torr, T : 400°C |

| (3) | H <sub>2</sub> Annealing | H <sub>2</sub> : 30sccm<br>P : 76Torr, T : 250°C                                                                        |

| (4) | CVD of SiO <sub>2</sub>  | SiH <sub>4</sub> : 6sccm<br>O <sub>2</sub> : 2sccm<br>P : 0.8Torr, T : 250 <sup>o</sup> C                               |

| (5) | Al Evaporation &         | Patterning                                                                                                              |

| (6) | H <sub>2</sub> Annealing | H <sub>2</sub> : 200sccm<br>P : 760Torr, T : 250 <sup>o</sup> C                                                         |

|     |                          |                                                                                                                         |

a-Si layer was deposited at 400°C and was 50nm thick. In order to improve the CVD a-Si film, the samples were annealed at 250°C in hydrogen just before the deposition of SiO<sub>2</sub>. For SiO<sub>2</sub> deposition, a gas mixture of silane  $(SiH_4)$  and oxygen was used. The deposition temperature was kept as low as the hydrogen annealing temperature (i.e.,  $250^{\circ}C$ ). The SiO<sub>2</sub> thickness was 140nm. An Al layer was evaporated on the SiO<sub>2</sub> layer as the gate electrode. After patterning the Al and SiO<sub>2</sub> layers, the samples were annealed again in hydrogen at  $250^{\circ}C$ . Channel length and width were  $65\mu$ m and  $220\mu$ m, respectively.

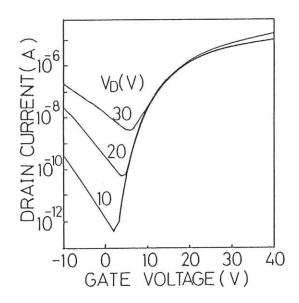

Fig.3 The semi-logarithmic drain current as a function of the gate voltage for various drain voltages.

The semi-logarithmic drain current,  $log(I_D)$ , is shown in Fig. 3, as a function of the gate voltage V<sub>G</sub> for drain voltages, V<sub>D</sub>, of 10, 20 and 30V, respectively. The on/off ratio of the drain current was more than  $10^7$  at V<sub>D</sub>=10V. The threshold voltage was 12.6V.

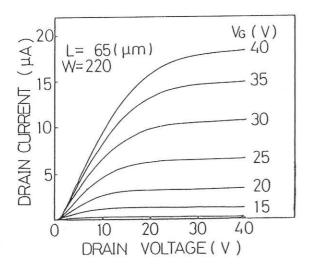

Linear  $I_D - V_D$  characteristics are shown in Fig. 4 for various positive  $V_G$  values. The maximum field-effect mobility estimated from the linear  $I_D - V_D$  region was 0.5 cm<sup>2</sup>/Vs. These values are higher than typical values for the top-gate plasma-CVD TFT.<sup>7</sup>)

Fig.4 The drain current as a function of the drain voltage for various values of the gate voltage.

#### 4. Conclusion

We have investigated an a-Si TFT with a top-gate structure. The high performance and simple fabrication steps of the CVD-produced top-gate TFT together with various advantages of CVD method<sup>5)</sup> make this device very attractive for high quality displays.

#### Acknowledgment

The authors would like to express their thanks to Showa-Denko for preparing the trisilane.

#### References

- L.E.Tannas ; IEEE Spectrum <u>26(1989)</u> 34.

P.G.LeComber, W.E.Spear and A.Ghaith ;

- Electron. Lett. 15(1979) 179.

- 3) P.K.Weimer; Proc. IRE 50(1962) 1462.

- 4) P.A.Breddels, H.Kanoh, O.Sugiura and M.Matsumura ; Electron. Lett. 24(1989) 1637.

- 5) H.Kanoh, O.Sugiura, P.A.Breddels and M.Matsumura ; Electro. Dev. Lett. 11(1990) 258.

- 6) Y.Lebosq, M.LeContellec, F.Morin, S.Salaun and P. Weisse ; IEEE Conference Record of The 1985 International Display Research Conference (1985) 34.

- 7) K.Sera, F.Okumura, H.Uchida, S.Itoh, S.Kaneko and K.Hotta; IEEE Trans. Electron Devices <u>36</u>(1989) 2868.

8) S.P.Murarka; Silicides for VLSI Applications, Academic Press; New York,

- 1983.

- 9) W.Losch and H.Niehus ; Proceeding of 11th International Conference on Amorphous and Liquid Semiconductors 2(1985) 1019.