Extended Abstracts of the 22nd (1990 International) Conference on Solid State Devices and Materials, Sendai, 1990, pp. 1035-1038

# Mechanism of Mobility Improvement of a-Si TFT with Channel Passivated Layer

Yasuo TANAKA, Ken TSUTSUI, Toshiko KOIZUMI†, Hideaki YAMAMOTO and Toshihisa TSUKADA

Central Research Laboratory, Hitachi, Ltd., † Musashino Works, Hitachi Device, Ltd., Kokubunji, Tokyo 185, Japan

The a-Si TFT with the channel-passivated layer shows high mobility and low threshold-voltage compared with the conventional TFT. The  $\beta \max^{-1}$  vs. channel-length relations indicate the existence of the induced n-channel under the drain/ channel-passivation overlap region for Vg <Vd. The induced-channel shortens the effective channel-length to increase the observed mobility, and that suppresses the hole-injection from drain-electrode in Vg <OV. Optimizing the conditions of depositing a-Si(i) layer, the off-current at Vg=-20V decreases lower than  $10^{-13}$  Å.

#### 1. Introduction

The a-Si TFT's have been widely used in active-matrix liquid crystal displays (LCD's) [1]. The requirements of a-Si TFT's for TFT/ LCD's are high on-current for signal-charging. low off-current(Ioff) for signal- holding [2], low threshold-voltage(Vt) for reducing driving voltage and small Vt-shift for reliability [3]. Several types of structures have been proposed on the a-Si TFT's, so far. The inverted-gatestaggered a-Si TFT with the channel-passivated (CHP) layer has advantages of high mobility [4] and low off-current. However, it is not always why the CHP-TFT has these merits. clear Recently, the overlap-effects of CHP-TFT's were calculated using two-dimensional computer simulations [5]. We studied experimentally some ambiguous points to estimate the mobility  $(\mu)$ , the Vt and the Ioff in the CHP-TFT's. Such conditions as the applied-voltages on the gate (Vg) and drain electrodes (Vd), the sizes of channel-width(W) and length(L) after fabrication, and the edge-effects should be taken into account carefully. In this paper, we will discuss the mechanism of the mobility increase and the Vt reduction, and the

conditions to lower off-currents in the CHP-TFT's.

#### 2. Experiment

# 2.1 TFT Fabrication

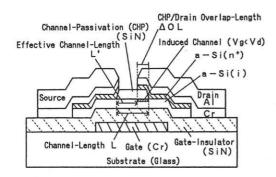

Fig. 1 shows the cross-sectional view of an asymmetrical CHP-TFT in which the overlaplengths of source/CHP and drain/CHP are made asymmetrically. On a glass substrate, a gateelectrode of Cr was formed, on which a gateinsulator of SiN(300 nm thickness), an undoped a-Si(i) layer(20 ~ 50 nm) and a CHP layer of SiN (200 nm) is continuously deposited by the rf (13.56 MHz) glow-discharge CVD method. The SiH<sub>4</sub>-NH<sub>3</sub>-N<sub>2</sub> mixtures were used for the depositions of the gate-insulator and the CHP layer. the pure SiH4 was used for the a-Si(i) layer. The a-Si(i) layer degradation were prevented by controling deposition temperature of the a-Si(i) and CHP layer. After the CHP patterns were formed, a light etch was necessary over the a-Si(i) surface by a diluted HF-NH<sub>4</sub>F buffer-solution to improve the source and drain contacts. Then, an a-Si(n<sup>+</sup>) layer(30 nm) was deposited by the same CVD method using the  $SiH_4-H_2-PH_3$  mixtures. The a-Si(n<sup>+</sup>) layer

on the CHP layer was removed after the formation of source-drain electrodes of evaporated Cr and Al. Finally, a passivation layer was formed (not shown in Fig. 1).

### 2.2 Measurement

First, the overlap-effects of drainelectrode over the CHP layer on the CHP-TFT is investigated by comparison with the conventional inverted-gate-staggered TFT in which an a-Si(n<sup>+</sup>) layer is deposited continuously on an a-Si(i) layer. We define the channellength under the CHP layer as L, and the drain /CHP overlap-length as  $\_$  OL. The  $\mu$  and  $\beta$ values are derived from the differential curves of the  $\sqrt{Id}$  vs. Vg curves using the relation of  $\sqrt{Id} = \sqrt{(\beta/2)} \cdot (Vg - Vt)$ , where  $\beta =$ µ •CsiN•W/L, Id is the drain-current, and CsiN is the capacitance of the SiN gate-insulator per unit area. In those curves, we define the maximum values of  $\beta$  and  $\mu$  as  $\beta$  max and  $\mu$  max, respectively. The Vt, max and Vg, max correspond to those maximum values using the relations of  $\sqrt{Id} = \sqrt{(\beta \max/2) \cdot (\forall g, \max - \forall t, \max)}$  and  $\beta \max =$ µ max · CsiN · W/L.

# 3. Results and Discussion

3.1 Dependences of  $\mu$  and Vt on gate-voltage

Fig. 2 shows the  $\mu$  vs. Vg and Vt vs. Vg characteristics for the CHP-TFT (L = 10.1  $\mu$  m, O plots) and for the conventional TFT (L = 11.5  $\mu$ m,  $\Delta$  plots). Fig. 2 indicates that the mobility of the CHP-TFT has the large dependence on the gate-voltage, and has the maximum values ( $\mu$  max = 0.92 cm<sup>2</sup>/V·s, Vt,max =1.2 V) at around Vg = 5V (Vg,max). The  $\mu$ -values at a gate-voltage higher than 10V are similar to those of the conventional TFT. On the contrary, the conventional TFT has a moderate peak in mobility at around 10V ( $\mu$  max = 0.54 cm<sup>2</sup>/V·s, Vt,max = 2.6 V). The CHP-TFT's have higher  $\mu$  max-values and lower Vt, max-values than those of the conventional TFT's in the range of Vg < Vd.

## 3.2 Effects of the drain/CHP overlap region

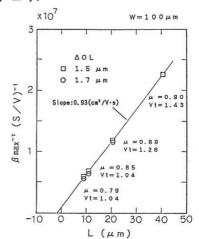

Fig. 3 shows the  $\beta \max^{-1}$  vs. L characteristics of the asymmetrical CHP-TFT in which AOL is large (AOL = 4.8  $\mu$  m, O plots), compared with those of the same TFT with the source and drain electrodes exchanged, i.e., AOL is small (AOL = 0.0  $\mu$  m,  $\Box$  plots). It is clear that the plots corresponding to the large ∆OL (O plots) and the small ∆OL (□ plots) are on the separate lines. On the other hand, as for the symmetrical CHP-TFT shown in Fig. 4, these phenomena have not been observed, and the both lines are exactly matched each other. In Fig. 4, AOL is almost the same, i.e., one side is  $\Delta OL = 1.7 \ \mu m$ , O plots, another side is  $AOL = 1.5 \ \mu m$ ,  $\Box$  plots. If we use the channel-length L' which is equal to L-AOL instead of the channel-length L shown in Fig. 1, then the line of the  $\Delta OL = 4.8 \ \mu m$  (O plots) shifts to the left, and the line after the correction ( plots) is the same as the line corresponding to the  $\Delta OL = 0.0 \ \mu m \ (\Box \ plots)$ . This fact suggests that the existence of the induced n-channel under the AOL region shown in Fig. 1, and this dominates the draincurrent characteristics in the low gate voltage of Vg < Vd. Then the channel length L becomes shorter by LOL, and as a result, the observed mobility increases.

After the correction of the &0L-effect (• plots) in Fig. 2, the  $\mu$  max-value of the CHP-TFT takes a lower value ( $\mu$  max = 0.73 cm<sup>2</sup>/ V·s) than the original value (0.92 cm<sup>2</sup>/V·s), but this value is still higher than that of the conventional TFT (0.54 cm<sup>2</sup>/V·s). That was mainly caused by the differences of the edgeeffects of the drain-electrode in the CHP-TFT and the plasma-damages on a-Si(i) back-surface in the conventional TFT.

Fig. 5 (a) and (b) show the comparison of the  $\mu$  vs. Vg characteristics of different AOL, i.e., (a) AOL = 1.4  $\mu$ m and (b) AOL = 0.3  $\mu$ m for different Vd. Fig. 5 (a) shows the typical  $\mu$  vs. Vg curves of the CHP-TFT, while Fig. 5 (b) shows similar to those of the conventional TFT. The induced n-channel under the  $\Delta OL$  region has the effect of accelerating the rise of on-current as well as shortening channel-length, and going with this, the Vt,max-values become lower as shown in Fig. 2 and Fig. 5.

# 3.3 Off-current of the CHP-TFT's

Discussing the off-current of a-Si TFT, we should distinguish the two types of offcurrents. One has the dependence on Vg due to the rising of the hole-current, another has not the dependence on Vg due to simple leakage currents such as the surface or boundary leakage current. In the conventional TFT's, it is difficult to achieve the off-currents lower than  $10^{-13}$  A at Vg = -20 V and Vd = 10 V, although it is easier to achieve at Vg = -5 V. Because, the conventional TFT's have a strong electric field around the edge of drain electrode and the hole-injection easily occur. However, the CHP-TFT's have a weak electric field under the drain-electrode due to the electrical shield-effect of the AOL region. Moreover, the induced n-channel of the AOL region blocks the hole-injection from drainelectrode under negative gate bias. Consequently, the hole-injection in the CHP-TFT's will be suppressed lower level than the conventional TFT. Fig. 6 shows the dependence of the Ioff-values at Vg = -20 V on deposition temperature of a-Si(i) layer. As was expected, the Ioff-value is kept lower than 10<sup>-13</sup> A in the range lower than 230℃. However, in the range higher than 240 ℃, the Ioff-value increases exponentially with the deposition temperature of a-Si(i) layer. This fact is explained as follows: the increase of acceptor levels in a-Si(i) layer due to the hydrogen release from this layer makes easy the holeinjection from the a-Si(n<sup>+</sup>) layer under drainelectrode. In Fig. 6, the influence of channellength on off-current is relatively small. Thus, the off-currents of CHP-TFT's are lowered with the optimized a-Si(i) layer.

This condition is also useful to prevent the abnormal positive Vt-shift accompanied with moderating of the rise of on-current under the negative-stress.

### 4. Summary

The a-Si TFT with the channel-passivated layer show high mobility and low thresholdvoltage compared with the conventional TFT's. The on-current for the CHP-TFT's has the dependence on the drain/CHP overlap-length &OL, and indicate the existence of the induced nchannel under the AOL region in the low gatevoltage of Vg < Vd. The induced n-channel shortens the effective channel length to increase the observed mobility, and accelerates the rise of mobility in the low gatevoltage region. Another effect of the induced n-channel is suppressing hole-injection from the drain electrode under negative gate voltage. The off-currents of the CHP-TFT's are reduced to a level lower than 10<sup>-13</sup> Å at  $V_g = -20$  V with the optimized a-Si(i) layer.

#### ACKNOWLEDGEMENTS

The authors would like to thank Mr. H. Matsumaru and Mr. M. Yamaguchi for their technical discussions and support. We greatfully acknowledge the encouragement and support from Dr. H. Matsumura of Central Research Laboratory, Hitachi, Ltd. and Dr. A. Sasano of Mobara Works, Hitachi, Ltd.

### REFERENCES

- [1] F. Inoue et al.: SID'88 DIGEST(1988), 318.

- [2] Y. Kaneko et al.: IEEE Trans. Electron Devices, <u>36</u>(1989), 2953.

- [3] Y. Kaneko et al.: Extended Abstracts of the 18th Intn'l Conf. on Solid State Devices and Materials(1986), 699.

- [4] S. Hotta et al.: SID'86 DIGEST(1986), 296.

- [5] J. G. Shaw and M. Hack: J. Appl. Phys., <u>65</u> (1989), 2124.

Fig. 1 Cross-sectional view of the asymmetrical CHP-TFT, with an overlap region of the drain -electrode on the channel -passivated layer.

Fig. 2  $\mu$  and Vt vs. Vg characteristics of the symmetrical CHP-TFT ( O ) with the correction of  $\triangle$ OL effect (  $\bigcirc$  ), compared with those of the conventional TFT (  $\triangle$  ).

Fig. 5 Comparison of  $\mu$  vs. Vg characteristics of different AOL, (a) AOL = 1.4  $\mu$  m and (b) AOL = 0.3  $\mu$ m for different Vd.

Fig. 3  $\beta \max^{-1}$  vs. L characteristics of the asymmetrical CHP-TFT (  $\&0L = 4.8 \ \mu \text{ m}$ , O ) with the correction of the &0L effect ( ), compared with those of the same TFT with the source and drain electrodes exchanged (  $\&0L = 0.0 \ \mu \text{ m}$ ,  $\Box$  ).

Fig. 4  $\beta \max^{-1}$  vs. L characteristics of the symmetrical CHP-TFT (  $\triangle OL = 1.7 \ \mu m$ , O ) compared with those of the same TFT with the source and drain electrodes exchanged (  $\triangle OL = 1.5 \ \mu m$ ,  $\Box$  ).

Fig. 6 Dependence of Ioff at Vg = -20 V on the deposition temperature of a-Si(i) layer.