Extended Abstracts of the 1991 International Conference on Solid State Devices and Materials, Yokohama, 1991, pp. 475-477

## Tunnel Structured Stacked Capacitor Cell (TSSC) for 64 MBit dRAMs

N. Matsuo, Y. Nakata, H. Ogawa, T. Yabu, S. Matsumoto, M. Sasago and S. Okada

Semiconductor Research Center, Matsushita Electric Industrial Co., Ltd. Yagumo-nakamachi, Moriguchi, Osaka 570, Japan.

A new 3-dimensionally (3-d) stacked capacitor, TSSC, was developed. The TSSC realized the improved reliability and a capacitance of 29 fF with 0.25  $\mu m$  capacitor height because of the side-wall electrodes. The equivalent thickness of SiO<sub>2</sub> for the Oxide Nitride Oxide film (ONO) is 7.8 nm, and the cell area is 1.8  $\mu m^2$ . The side-wall electrodes formation leads no generation of the local field concentration inside of the tunnel that are clarified by the Transmission Electron Microscopy (TEM) observation for the uniformity of the ONO inside of the tunnel. These results indicate that the TSSC is one of the potential candidates for 64Mbit dRAMs.

1. Introduction: 3-d stacked capacitors become essential to realize the highdensity dRAMs 1,2,3,4). There are several requirements. : (1) The reliability of the storage electrode which is closely related with the localized concentration of the electric field at the capacitor electrode and the uniform deposition of the capacitor-dielectric-film within the narrow gap of the storage electrode. (2) The optimum capacitor structure with large capacitance of which height is limited by the depth of focus of photo lithography  $(\pm 1.0 \ \mu\text{m};$  in case of KrF).5) This paper proposes a new cell (TSSC) possessed of the above requirements and describes the reason of the improved reliability of this cell.

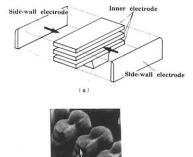

Figure 1.(a), (b) show a schematic view and the SEM photograph of the storage electrode of the TSSC with 2 tunnels, The storage electrode of the respectively. TSSC is composed of both the inner electrodes and the side-wall electrodes which are attached to the both sides of the inner electrodes to make the tunnels in the The reduction of the storage electrode. electric field concentration at the storage and plate electrode and a high capacitance with the small capacitor height can be realized. From a simple calculation, the capacitance of the TSSC is about 1.5 times as large as the stacked cell which is composed of only the inner electrode shown in Fig. 1(a).

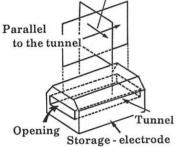

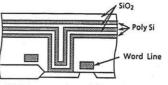

2. Experimental procedure: The TSSCs with 1 tunnel or 2 tunnels and the STC were fabricated. The process sequence of the TSSC is shown in Figure 2. The cell area is

Figure 1. (a) a schematic view and (b) a SEM photograph of the storage electrode of the TSSC with 2 tunnels. The side - wall electrodes are attached to the both sides of the inner electrodes to make the tunnel in the storage electrode.

1.8  $\mu\text{m}^2$  and the tunnel height equal to the thickness of the SiO2 (shown in Fig. 2(c)) is 50 nm for both TSSCs. The thickness of both the inner electrodés and the side-wall electrodes are 50 nm. The ONO consists of three-stacked layers: the natural oxide at the bottom, the intermediate nitride film which was grown by the LPCVD method, and the top oxide film by the wet method. The equivalent thickness of SiO2 for ONO is 6-The leakage current - plate 7.8 nm. (I-V) characteristics, the voltage distributions of the breakdown voltage, the constant voltage Time Dependent Dielectric Breakdown (TDDB) characteristics and the capacitances were examined for the TSSCs and the STC by measuring the 512K cell arrays. A positive bias was applied to the plate The breakdown voltage was electrode. defined as the bias at a leakage current of 1mA. The uniformity of the ONO inside of the tunnel was evaluated by observing some areas at regular interval from the opening

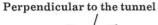

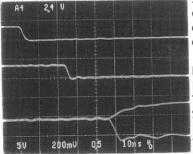

of the tunnel for the specimen of which tunnel length is 15.6 µm with Transmission Electron Microscopy (TEM). Figure 3 illustrates the relationship between the cross section, which is for the TEM observations both perpendicular to the tunnel and parallel to the tunnel, and the storage electrode. 3. Results and discussion: Figure 4 shows

the results of the I-V characteristics at the positive bias, for the TSSCs and the STC. The leakage currents of the TSSCs with 1 tunnel or 2 tunnels and the STC are proportional to the capacitance area of these capacitors. At the negative bias, the leakage currents are smaller than that at the positive bias. Figure 5 shows the

Figure 3. The relationship between the cross section. which is for the TEM observations both perpendicular to the tunnel and parallel to the tunnel, and the storage electrode.

the results of distributions of the breakdown voltage for the TSSCs and the STC. There was no degradation of the distributions of the breakdown voltage for the TSSCs, compared with the STC. Figure 6 shows the results of the TDDB characteristics for the TSSC with 2 tunnels and the STC. These datas are normalized by the capacitance areas. The characteristics of the TSSC is as same as that of the STC. These results indicate that the electric field concentration at the capacitor electrode is not generated for the TSSC. To clarify this phenomenon, the ONO inside of the tunnel was examined. Figures 7.(a), (b) and (c) show the cross sectional TEM photographs at the area of approximately 5 µm from the opening of the tunnel. Fig. 7(a) is perpendicular to the tunnel, and Fig. 7(b) is parallel to the tunnel. The ONO inside of the tunnel except for the corner of the tunnel is uniform over the entire length, and the thickness of which is as same as that outside of the tunnel. Fig. 7(c) is at the corner of the tunnel shown by the circle in Fig. 7(a). At the corner of the tunnel, the top oxide film (shown by "B") of the ONO is a little thicker than that at the other area, and the shape of the plate electrode at the corner of the tunnel is round. These shape effects are caused by the side-wall electrode formation. Because there is no generation of the local field concentration inside of the tunnel as shown in the schematic view of Fig. 7(c), the reliability of the TSSC is as good as that

d).SiO2 removal by HF solution and ONO dielectric films formation

Plate electrode

ONO dielectric films

e).Plate electrode formation

(P doped CVD poly Si)

a).Multi storage electrode layers formation

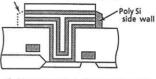

Figure 2. The process sequence of the TSSC.

c). Common storage electrode formation (Poly Si side wall formation and partial etching)

Figure 8 shows the relationship of the STC. between the capacitance and the cell area. The TSSC realizes a capacitance of 29 fF (7.8 nm SiO<sub>2</sub> equivalent) and 0.25 um capacitor height with 2 tunnels because of the side-wall electrode formation. The TSSC with 2 tunnels was applied to 64Mbit Figure 9 shows the cross sectional dRAMs. SEM photograph of 64Mbit dRAMs. Figure 10 shows the operation wave form. These

Figure 4. The I - V characteristics at the positive bias, for the TSSCs with 1 tunnel or 2 tunnels and the STC. The equivalent thickness of SiO<sub>2</sub> for ONO film is 6 nm.

Figure 5. Distributions of the breakdown voltage for the TSSC with 2 tunnels and the STC. The equivallent thickness of SiO<sub>2</sub> for ONO film is 7.8 nm.

curren

CELL AREA(µm<sup>2</sup>) 4. Summary: The TSSC with 2 tunnels realizes (1) the same reliability as that of the STC, and (2)a capacitance of 29 fF with 0.25 µm capacitor height which are both because of The ONO the side-wall electrode formation. inside of the tunnel was uniform except for The thickness of the ONO is a the corner. at the corner and this little larger

phenomenon leads the improved reliability. The authors wish 5. Acknowledgements: to

Figure 9. The cross sectional SEM photograph of 64Mbit dRAMs.

Figure 10. The operation wave form.

Τ. acknowledge Mr. Kouzaki of Matsushita Technoresearch Inc. Co., Ltd. for TEM observation. Thanks are also to Mr. M due Υ. Inoue, Mr. Terui, Drs. Τ. Takemoto and S. Horiuchi of the Semiconductor Research Center for their encouragements during the course

6.

TDDB

of this study. References: 1) Т Ema, S. Kawanago, Τ. Nishi, S.Yoshida, н. Nishibe, Τ. Yabu, Y Kodama, Τ.

Μ. Nakano and Taguchi: IEDM

Figure 7. The cross sectional TEM photographs of the TSSC with 1 tunnel and the schematic views of it. Fig. 7(a) is perpendicular to the tunnel and fig. 7(b) is parallel to that. Fig. 7(c) is at the corner of the tunnel shown by the circle in fig. 7(a). The area shown by "A" is the 2-layer film composed of the nitride and the bottom natural oxide, and the area by "B" is the top oxide. The schematic view both of the ONO and the plate - electrode inside of the tunnel is added to Fig. 7(c).

Tech. Dig. 1988 p.592. 2) W. Wakamiya, Y. Tanaka, H. Kimura, H.Miyatake and S. Satoh: VLSI Sympo. Tech. Dig. 1989 p.69. 3) S. Inoue, A. Κ. and Nitayama, Hieda F. Horiguchi: IEDM Tech. Dig. 1989 p.31. 4) Τ. Watanabe, N. Aoto, S. Η. Adachi, Ishitani, E. Ikawa and K. Terada: Extended Abst. of the 22th SSDM 1990 p.873. 5) Y. Tani, M. Sasago, H. Fujimoto, N. Furuya, T. Ono, N. Horiuchi and T. Miyata: VLSI Sympo. Tech. Dig. 1990 p.7.