Extended Abstracts of the 1991 International Conference on Solid State Devices and Materials, Yokohama, 1991, pp. 368-370

# The Room Temperature Characteristics of GaAs $\delta$ -Doped Superlattice Switching Transistor

### W.C. Liu, C.Y. Sun, W.S. Lour, D.F. Guo, and Y.S. Lee

Department of Electrical Engineering, National Cheng–Kung University, Tainan, TAIWAN, Republic of China

In this paper, a new functional GaAs switching transistor is demonstrated. A sawtooth  $\delta$ -Doped superlattice is introduced between anode and cathode. Holes, created by the avalanche multiplications near the metal-semiconductor (M-S) junction, play an important role in the transport properties. An attractive S-shaped negative differential resistance (NDR) phenomenon in the experimental current-voltage characteristics is observed. Furthermore, with proper operation of the third electrode, gate, the studied structure performs a controllable switching characteristics.

## 1. INTRODUCTION

Recently, for being used on the high frequency oscillators and microwave circuits, the N-shaped or S-shaped negative-differential-resistance (NDR) devices have attracted great attentions in circuit applications. However, quite a few three-terminal switching devices with S-shaped NDR have ever been reported. In spite of that, with the increasing improvement of semiconductor growth technologies, e.g., molecular beam epitaxy (MBE) and metal organic chemical vapor deposition (MOCVD) etc, it becomes possible to locate impurity doping profile at an atomic layer. Therefore, a new artificial doping technology, the monolayer doping or  $\delta$ doping, has been successfully developed.1) In addition, Schubert et al. have achieved the sawtooth-doping-superlattice (SDS) structure<sup>2-6</sup>) based on the doping superlattice concept of Esaki et al.<sup>7)</sup> and the  $\hat{\delta}$ -doping method of Wood et al.<sup>1)</sup> The SDS is fabricated by altering periodic n- and p-type dopants onto semiconductor within a considerably short length scale period and causes a great potential modulation in the band structure. With a long period such as 600A, the SDS structure exhibits an S-shaped NDR phenomenon.<sup>5)</sup> In this paper, we propose a new three-terminal-controlled GaAs switching device in which a double SDS structure with two different  $\delta$ -doping sheets and a metal-semiconductor (M-S)structure are employed. In the proposed structure, holes are generated from the avalanche breakdown near the M-S junction and accumulated at the valence band maxima of the zigzag quantum wells. It causes a potential redistribution in the band structure. As a result, the studied device exhibits a controlled S-shaped NDR performance at room temperature.

# 2. EXPERIMENTS

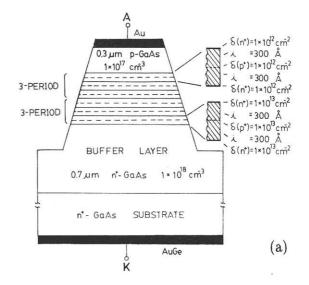

The structure studied was grown on a (100)-oriented n<sup>+</sup>-GaAs substrate by MBE. The details of substrate preparation and layers growth were described elsewhere.<sup>8-9)</sup> The growth sequence included a 0.7  $\mu$ m Si-doped GaAs (n=1×10<sup>18</sup> cm<sup>-3</sup>) buffer layer, SDS1, SDS2, and a 0.3 µm Be-doped GaAs (p=1×10<sup>17</sup> cm<sup>-3</sup>) cap layer. The SDS1 was composed of 3-period  $\delta(n^+)-i-\delta(p^+)-i$  superlattice with  $\delta(n^+) = \delta(p^+) = 1 \times 10^{13} \text{ cm}^{-2}$  and i=300A while the SDS2 was 3-period  $\delta(n^+)$ -i- $\delta(p^+)$ -i superlattice with  $\delta(n^+)=\delta(p^+)=1\times 10^{12}$  cm<sup>-2</sup> and i=300A. The growth temperature of the GaAs host material was Ts=580 °C which was reduced to 500 °C when the delta-doping layers were growing. After the epitaxial growth finishing, the ohmic contact was then formed to the cathode (K) by the deposition of AuGe metal on the bottom n<sup>+</sup>-GaAs layer. Besides, the Schottky contacts were employed to anode (A) by the deposition of Au metal on the top p-GaAs layer. Then, the wafer was etched into the n<sup>+</sup>-GaAs buffer layer using a wet chemical etching solution  $(3NH_4OH:1H_2O_2:50H_2O, 300K)$ . The schematic illustration of studied device is depicted in Fig.1.

#### 3. RESULTS AND DISCUSSIONS

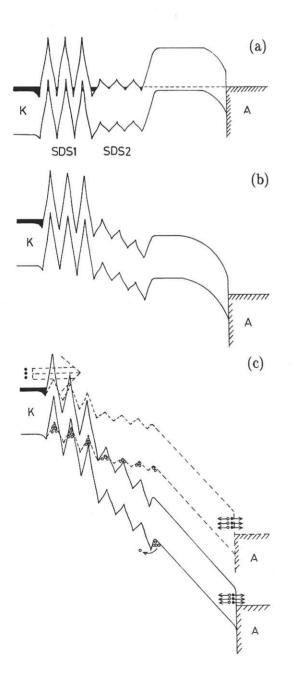

Fig.2 shows the energy band diagrams of studied devices. As shown in Figs.2 (a) and (b), due to the sufficient barrier height and width, the conducting current originating from the thermionic emission or tunneling is so small as to be neglected when the device is operated under zero bias or a small anode-cathode voltage VAK. As VAK is increased further, at some voltage VS, an avalanche multiplications near the metal-semiconductor (M-S) junction occurs. Then, holes, created by the avalanche multiplications, are accumulated at the valence band maxima, as shown in Fig.2 (c). In figure 2(c), the solid lines describe that the strong electrical field just causes the avalanche breakdown at M-S junction, but holes don't be transported into the sawtooth potential wells yet. Moreover, the dashed lines interpret that the holes trapped in zigzag quantum wells and yield the collapse of potential barriers due to the screening effect of acceptors. This causes the potential redistribution in SDS regions and performs an S-shaped NDR in current-voltage (I-V) characteristics at room temperature. The total conducting current will then rapidly increase because the potential barrier height for electrons injection are lowered substantially. The experimental I-V characteristics between anode and cathode at room temperature is shown in Fig.3 (a). As we expected, the S-shaped NDR is observed at 300K. When VAK is small, the conduction current can be neglected. At some VAK voltage, Vs, the sufficiently electrical field causes the avalanche multiplications and yields an onset of switching phenomenon. The switching parameters are Vs=8.0V, VH=5.7V, IH=1.0mA, and voltage control ratio Vs/VH=1.42, respectively.

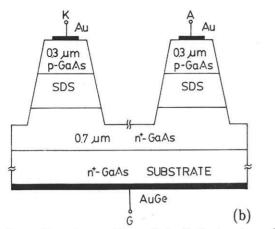

Fig.1(b) depicts the schematic cross section of the structure studied for three-terminal operation. Obviously, by using the gate electrode through the n<sup>+</sup>-GaAs buffer layer, it is a series composition of two-terminal structure as shown in Fig.1 (a). The application of a bias VGK at gate electrode can control the initial off-state switching voltage Vs across the anode and cathode regions. As illustrated by long-dotted line in Fig.2 (d), once a negative VGK voltage is applied, the SDS region is biased under an additional voltage drop with a magnitude of VGK over the gate floated condition. The employment of negative VGK voltage causes an effective enhancement on carrier transport in SDS A region and the conduction current, through anode-gate loop, is increased simultaneously. So, the initial off-state switching voltage Vs is expected to be lower than that at gate floated condition.

Figs.3 (b) and (c) shows the experimental I–V characteristics of the studied device under three– terminal operation. Fig.3 (b) shows the I–V characteristics between anode and cathode with the negative control voltages VGK. In accordance to our prediction, the initial off-state switching voltage VS is decreased with increasing the magnitude of the applied negative gate voltage VGK. In addition, Fig.3 (c) shows the I–V characteristics between anode and cathode with the negative control current IG. When the applied negative current IG is increased, the magnitude of the negative voltage VGK is also increased. As mentioned above, it causes an increment of anode current IA under the same anode-to-cathode bias VAK.

## 4. CONCLUSIONS

We have demonstrated a new three-terminal-

controlled GaAs switching device with double SDS device exhibits structures. The studied an interesting S-shaped NDR performance. The NDR phenomenon is attributed to the avalanche multiplications at M-S interface and the potential redistribution in SDS. Furthermore, the band structure and carrier transport properties can be adjusted effectively when the third electrode, i.e., gate, is employed. The facility of three-terminal operation provides the wide and flexible application capability. Consequently, with an appropriate design of the structural parameters, e.g., the delta doping density and the SDS number etc, the proposed structure exhibits good potential for switching circuit and multiple-valued logic circuit applications.

This study was supported by the National Science Council of the Republic of China under contract No. NSC-80-0404-E006-54.

## 5. REFERENCES

- C.E.C. Wood, G. Metze, J. Berry and L.F. Eastman : J. Appl. Phys. 51 (1980) 383

- 2) E.F. Schubert, A. Fischer and K. Ploog : Electron Lett. 21 (1985) 411

- 3) E.F. Schubert, A. Fischer, Y. Horikoshi and K. Ploog : Appl. Phys. Lett. 47 (1985) 219.

- 4) È.F. Schubert, Y. Horikoshi and K. Ploog : Phys. Rev. B32 (1985) 1085

- 5) E.F. Schubert, J.E. Cunningham and W.T. Tsang : Appl. Phys. 51 (1987) 817.

- E.F. Schubert, B. Ullrich, T.D. Harris and J.E. Cunningham : Phys. Rev. B38 (1988) 835.

- L. Esaki and R. Tsu : IBM J. Rev. Dev. 14 (1970) 61.

- W.C. Liu, R.L. Wang, W.S. Lour, C.Y. Sun and C.C. Hong : Jpn. J. Appl. Phys. 29 (1990) L7.

- 9) W.C. Liu, and C.Y. Sun : Jpn. J. Appl. Phys. 30 (1991) 635.

The schematic cross section of studied structure for (a) two terminal(b) three terminal operation

The corresponding energy band diagrams of the studied devices at (a) zero bias (b) a small positive bias (c) increased positive bias, the zigzag potential barriers redistribute after the avalanche breakdown process occurring at the M-S junction (d) three-terminal operation with negative VGK voltage.

The room temperature I-V characteristics of the studied devices under (a) two-terminal operation (b) three-terminal operation with applied negative VGK bias (c) three-terminal operation with applied negative IG current.