# Threshold Voltage Shift of a-Si TFTs during Pulse Operation

Ryoji Oritsuki, Toshikazu Horii, Akira Sasano, Ken Tsutsui†, Toshiko Koizumi\*, Yoshiyuki Kaneko†, and Toshihisa Tsukada†

Mobara Works, Hitachi, Ltd.

† Central Research Laboratory, Hitachi, Ltd.

\* Musashino Works, Hitachi Device, Ltd.

Mobara, Chiba 297, Japan †\* Kokubunji, Tokyo 185, Japan

The threshold voltage shift of amorphous -Si TFT's under pulse operation is discussed. The duty ratio and frequency dependence of the shift have been measured. A positive pulse stress causes a shift equivalent to that of DC voltage stress. On the other hand, a negative pulse stress decreases the amount of the shift depending on its pulse width and can be accurately described by an equivalent circuit model. Based on these data, a more dependable estimate of the long-term reliability of an amorphous-Si TFT panel has been realized.

# 1. Introduction

Amorphous-Si (a-Si) TFTs have been widely used in active-matrix LCDs because of their good switching characteristics. However, the threshold voltage (Vt) shift during operation still shows an obstinate instability of a-Si TFTs. Much effort has been done to reduce the amount of the Vt shift, (1) to study the shift mechanisms, (2) and to estimate the long-term reliability by their dependence on the stress period and voltage. (1) It is important to confirm the estimation methods and to verify panel life -time, because the direction is subject to stress polarity, and the resultant shift will be negligible by offsetting shifts of mutually oposite directions. Nevertheless, the investigation has mainly concentrated on applying DC voltage on the gate electrode, and the shift under pulse operation has not been studied in detail. In this paper, the Vt shift under pulse operation is described, and the estimate of the threshold voltage shift of such TFTs under long-term operation is presented.

### 2. Experiments

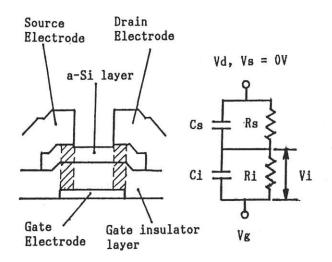

As shown in Fig. 1, TFTs used to study the shift have an inverted stagger structure with a gate insulator layer and an a-Si layer between the gate and the source and drain electrodes. The gate insulator layer is composed of silicon-nitride and aluminum -oxide, described in detail elsewhere. (3)

The threshold voltage is defined as the gate voltage at the intersection of extrapolation of the √Id vs. Vg curve in the saturation region. The Vt shift is derived by measuring the Vt before and after applying the

stress voltage. In the pulse stress measurements, a rectangular pulse is applied to the gate electrode with the source-drain electrodes set at 0 V. The total stress time is constant in every experiment.

# 3. Results and Discussion

# 3.1 Vt shift by pulse stress

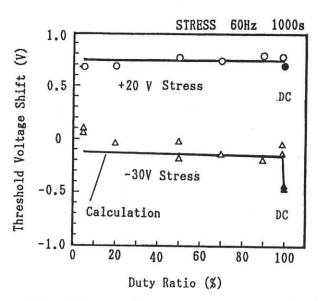

Figure 2 shows the duty ratio dependence of the  $\Delta$ Vt with 60 Hz pulses at 25°C. With a positive stress, the positive shift is almost constant with respect to the duty ratio. There is no difference between the shift by pulse stress ( $\bigcirc$  plots) and that by DC voltage stress ( $\bigcirc$  plots). A negative stress also shows no clear variation with the duty ratio, but there is a sharp jump between the pulse and DC stresses. The DC stress causes a shift to the negative direction ( $\triangle$  plots) about three times greater than the pulse stress ( $\triangle$  plots).

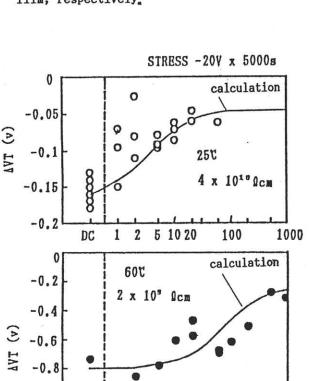

Figure 3 shows the frequency dependence of the shift with a negative pulse stress having a 50% duty ratio, at  $25 \, \mathrm{C}$  ( $\bigcirc$  plots) and  $60 \, \mathrm{C}$  ( $\bigcirc$  plots). The shift towards the negative direction is greater at  $60 \, \mathrm{C}$  than at  $25 \, \mathrm{C}$ . A high-frequency pulse decreases the shift. The shift starts to decrease at around 1 Hz at  $25 \, \mathrm{C}$  and  $10 \, \mathrm{Hz}$  at  $60 \, \mathrm{C}$ . In LCD panel operation, a negative pulse is applied at  $60 \, \mathrm{Hz}$ , which causes about a  $70 \, \mathrm{M}$  drop in the shift at  $25 \, \mathrm{C}$  and about a  $20 \, \mathrm{M}$  drop at  $60 \, \mathrm{C}$ .

# 3.2 Effects of pulse stress

Since the threshold voltage shows a negative shift with a negative stress, the shift should mainly be caused by carrier trapping at a -Si / SiN interface. Therefore, when TFTs are stressed by pulse voltage, the

voltage across the gate insulator (Vi) should be taken into account. Vi is calculated through the ordinary charging model of CR circuits, as shown in Fig. 1.

$$Vi = Vg(1 - \frac{Ci}{Cs + Ci} exp(-\frac{t}{\tau})) \qquad , \qquad (1)$$

$$\tau = (Cs+Ci) \cdot (\frac{1}{Rs} + \frac{1}{Ri})^{-1}$$

, (2)

where Vg is the applied voltage to the gate electrode, Ci and Cs are the capacitances, Ri and Rs are the resistances, of the insulator film and the a-Si film, respectively, t is the stress time, t is the time constant of the circuit.

When the negative pulse at 60Hz is applied to the gate at 25°C, the ratio of Vi to Vg is calculated as a function of pulse width using expression (1), where the specific resistivity of a-Si is assumed to be  $4x10^{10}$  Qcm at 25% and the a-Si film thickness is 0.24 µm. The ratio varies with the duty ratio, in other words, the pulse width. When the duty ratio is 99.9%, the gate insulator is stressed by 74% of the applied voltage.

Since the shift is proportional to the stress voltage to the power of 3.8, according to our measurements, we can calculate the amount of the Vt shift by pulse stress from the observed shift by DC stress. The result of this calculation is shown as solid line in Fig 2. In particular, there is a jump in the curve between 99.9% and 100% (DC stress), and the shift with the pulse stress is expected to be 34% of the shift with the DC stress.

On the other hand, when a positive pulse is applied to the gate, the gate insulator is stressed by almost a full-swing voltage, because the a-Si film resistence (Rs) becomes sufficiently low and the time constant ( $\tau$ ) of expression (2) is close to zero, and the voltage across the gate insulator (Vi) is nearly equal to the applied voltage (Vi). Thus, the positive pulse stress causes a shift equivalent to that with DC voltage stress, as shown in Fig. 2.

Furthermore, the frequency dependence of the shift can be calculated in the same way, where the specific resistivity of a-Si at 60°C is assumed to be  $2x10^9~\Omega cm$ . Since the specific resistivity increases at 60°C, the time constant t becomes small, according to expression (2). Therefore, the shift at 60% begins to decrease at higher frequency than that at 25°C. The result is shown in Fig 3 as a solid line and agrees with the data. Thus, the shift with the pulse stress can be explained by the charging model described above.

# 3.3 Estimate of Vt shift during LCD operation

The basic procedure for estimating the threshold voltage shift during LCD operation is same as reported elsewhere. (1) The shift is obtained as the sum of the  $\Delta Vt$  for a negative and positive bias.

$$\Delta Vt = \Delta Vt(+) + \Delta Vt(-), \qquad (3)$$

$$\Delta Vt(+) \propto (Vg-Vt)^{\alpha 1} \cdot t^{\beta 1},$$

(4)

$$\Delta Vt(-) \propto (Vg-Vt)^{\alpha 2} \cdot t^{\beta 2}, \qquad (5)$$

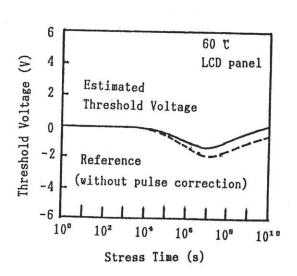

where  $\Delta Vt(+)$  is the shift by positive stress and  $\Delta Vt(-)$  by negative stress. As value  $\alpha 1$  and a 2 are used 2.7 and 3.8, respectively. The value of  $\beta1$  and  $\beta2$  have been measured at 60 Cby DC stress experiment to be 0.54 and 0.47, respectively. We calculated the ∆Vt of the LCD panel at 60  $\ensuremath{\text{C}}$ , assuming the effective voltage of the negative stress to be 95% of the original voltage. The result is shown as a solid line in Fig. 4, where a dashed line indicates the result estimated conventional method for reference. The estimation of the threshold voltage has been improved to less than 2 V in ten years even at 60°C.

#### 4. Summary

The threshold voltage shift of a-Si TFTs under pulse operation is quite different from that under DC bias. Although a positive stress causes an equivalent shift between pulse and DC stresses, a negative stress causes a sharp jump between 60 Hz pulse and DC stresses. Moreover, the frequency dependence of the shift by a negative pulse stress is remarkable and varies with temperature. These characteristics are explained well, by considering the effective voltage across the gate insulator. Consequently, when the a-Si TFTs are stressed by a negative bias during LCD operation, the expected negative shift is 34% at 25°C, and 82% at 60°C, with respect to the DC stress. Furthermore, the long-term reliability of a-Si TFTs can be estimated more precisely than before, using the data from DC stress measurements.

### ACKNOWLEDGEMENTS

The authors would like to thank Mr. H. Yamamoto for technical discussions. Also, the authors greatly appreciate the encouragement and support from Dr. H. Kawakami and Mr. Y. Tomita of Mobara Works, Hitachi, Ltd.

# REFERENCES

- (1) Y. Kaneko et al., Extended Abstracts of the 18th Conf. on Solid State Devices, '86, p699 (2) M.J.Powell, IEEE Trans ED vol 36, No 12,

- p2753

- (3) H. Yamamoto, IEDM '90, pp 34.3.1

Fig.1 Cross-sectional view of a-Si TFT(left); Equivalent circuit of shaded part(right); Cs and Ci are capacitances of a-Si and gate insulator film, and Rs and Ri are the resistances of a-Si and insulator film, respectively.

Fig.3 Frequency dependence of shift (AV<sub>T</sub>) at 25°C (O) and 60°C (●)

5 10 20

Freq (IIz)

100

-1.0

DC

1 2

Fig. 2 Duty ratio dependence of shift ( $\Delta V_T$ ) with positive stress (O) and negative stress ( $\Delta$ )

Fig. 4 Estimate curve of the threshold voltage of the LCD panel in panel life time.

Dashed line is a conventional result without correction of pulse stress.

1000