# A Proposal of a Highly Sensitive Interline CCD for HDTV

Toshifumi Ozaki, Hideaki Ono, Haruhiko Tanaka, and Kazuya Tokumasu Central Research Laboratory, Hitachi Ltd. Kokubunji, Tokyo 185, Japan

We propose new device structures for an interline CCD for HDTV, and analyze their performance in a 2-million-pixel image sensor with a 1-inch image format. The offset-shallow  $p^+$ -isolation and the completely-depleted well make it possible to shrink the channel width of the vertical CCD by 40% maintaining a charge handling capability of 22 fF. The combined use of a tetrode transistor and fluorine implantation reduces the noise charge of the amplifier by about half. These results indicate that the interline CCD has potential for HDTV applications.

## **1. INTRODUCTION**

A solid-state imaging device for high-definition TV systems needs to have 5 to 8 times as many pixels as conventional devices.<sup>1)2)</sup> This requirement, in conjunction with the need for miniaturization, makes it necessary to reduce the pixel size. However, in an interline CCD, <sup>1)6)</sup> which is widely available on the market, the area of the vertical CCD cannot be scaled down without sacrificing charge handling capability, and enlarging the signal band increases random noise of the output amplifier.

We propose new device structures to increase the charge handling capability of the vertical CCD and to lower the random noise of the amplifier. Their performance in a 2-million-pixel image sensor with a 1-inch image format is compared to a conventional structure.<sup>6</sup>

### 2. CHARGE HANDLING CAPABILITY

The maximum charge that can be transferred through the vertical CCD (charge handling capability)  $Q_S$  is given by:

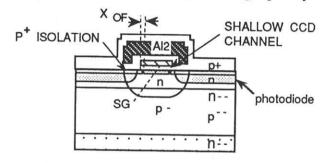

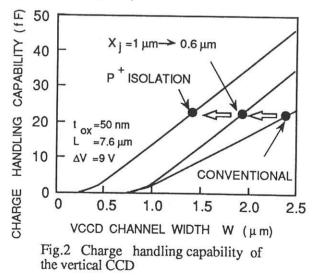

by:  $Q_S = C_U L(W - \Delta W)V$  (1) where  $C_U$  is the capacitance per unit area, L is the channel length, W is the channel width,  $\Delta W$  is the narrow channel factor, and V is the pulse swing. Pixel size reduction reduces the vertical CCD area.<sup>3</sup>) Therefore, there are only two ways to maintain the charge handling capability with a constant pulse swing; to decrease  $\Delta W$  or to increase  $C_U$ . A cross-sectional view of the proposed vertical CCD is

A cross-sectional view of the proposed vertical CCD is shown in Fig.1. In this structure, the shallow  $p^+$  and  $p^-$  double well isolates the n CCD channel from the n photodiode.<sup>4)</sup> There is no deep p-isolation in this structure. The shallow  $p^+$  is offset by only 0.3 µm from the n CCD channel. As a result, the narrow channel factor is lowered without degrading the isolation. Moreover, the n CCD channel is shallowed to the minimum possible with the process in order to increase the unit capacitance. The results of a two-dimensional computer simulation of the charge handling capability

Fig.1 Cross-section of the vertical CCD isolated by the shallow p+ layer

are shown in Fig.2. The proposed structure, with a channel 0.58 times as narrow as the conventional device, has the charge handling capability of 22 fF, which is satisfactory for operation.

Shallowing the CCD channel inevitably degrades the charge transfer efficiency of the horizontal CCD, which has the same doping profile as the vertical CCD. This problem has prevented the shallowing of the CCD channel in conventional devices. Moreover, a CCD for HDTV needs 3 to 4 times faster charge transfer.

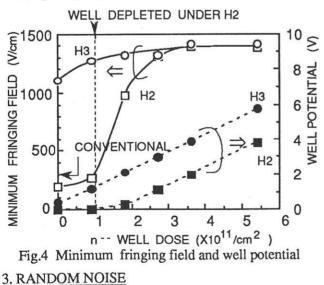

Charge transfer inefficiency is approximately proportional to the single-carrier transient time  $t_{tr}$ , which is given by:

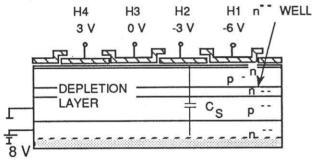

t<sub>tr</sub>=L/2 $\mu$ E<sub>fm</sub> (2) where  $\mu$  is the electron mobility and E<sub>fm</sub> is the minimum fringing field.<sup>3)</sup> Hence, a higher minimum fringing field is necessary to achieve faster charge transfer. The completely depleted well structure shown in Fig.3 enhances the minimum fringing field. In this structure, the n<sup>--</sup> well is formed under the p<sup>--</sup> double well of the horizontal CCD. The depletion layer is about 4 times as deep as in the conventional one. The results of two-dimensional computer simulation of the minimum fringing field are shown in Fig.4. When the well is not completely depleted, the minimum fringing field is 2/3 the conventional one because the channel is shallow. However, it reaches 7 times when the well is completely depleted (when well potential is over 0 V). This value is sufficient for the HDTV CCD.

Fig.3 Cross-section of the horizontal CCD with a completely depleted well

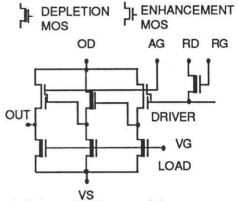

The schematic diagram of the output amplifier is shown

in Fig.5. In this configuration, the primary noise source, after CDS (Correlated Double Sampling),<sup>5)</sup> is the MOS driver transistor of the first source-follower. The random noise charge  $Q_{p}$  is given by

$$Q_{n} = \frac{C_{in}}{q} \sqrt{\frac{2f_{BO}}{f_{H}}} \int_{0}^{f_{B}} 4\sin^{2} (\pi f T_{S}) S(f) d^{-} (3)$$

In equation (3), q is the electronic charge, Cin is the input capacitance of the amplifier, fBO is the signal bandwidth, fH is the driving frequency of the horizontal CCD, fB is the cutoff frequency of the amplifier, Ts is the sampling period of the CDS circuits, and S(f) is the noise power spectrum. Increasing signal band-width increases of fB and Ts. Therefore, S(f) and Cin need to be lowered.

Fig.5 Schematic diagram of the output amplifier using tetrode transistors

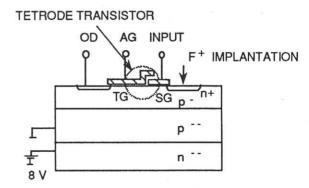

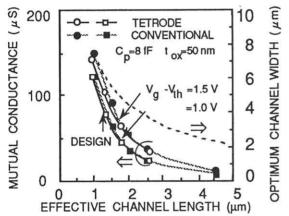

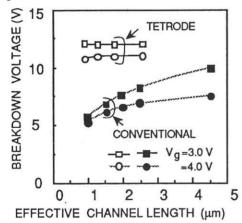

A MOS transistor has two noise sources; thermal noise and 1/f noise. The power spectrum of thermal noise is inversely proportional to the ratio of the channel width to channel length. The power spectrum of 1/f noise is inversely proportional to the channel area. Accordingly, S(f) can be reduced by using a wide channel. In the case of the driver, however, the input capacitance of the amplifier  $C_{in}$ , which includes the gate capacitance of the driver, increases as the channel width increases. So, a minimum random noise charge is reached at the point where the gate capacitance of the driver C<sub>G</sub> is equal to the parasitic capacitance at the input of the amplifier  $C_{p}$ . The thermal noise power spectrum can be reduced as the channel length decreases in order to increase mutual conductance. However, the breakdown voltage limits the use of a short channel. The tetrode transistor, shown in Fig.6, solves this problem. The constantly biased gate

Fig.6 Cross-section of the tetrode transistor

AG shields the electric field from the drain (OD) in order to increase the breakdown voltage. The mutual conductance of the tetrode transistor increases as the effective channel length decreases, in the same way as the conventional one, as shown in Fig.7. The effective channel length at which the breakdown voltage reaches 7 V is less than 1  $\mu$ m in the tetrode transistor and about 2.5  $\mu$ m in the conventional one, as shown in Fig.8. Hence, the mutual conductance is increased three to four times for the same gate capacitance.

Fig.7 Mutual conductance of the driver with the optimum channel width

Fig.8 Breakdown voltage

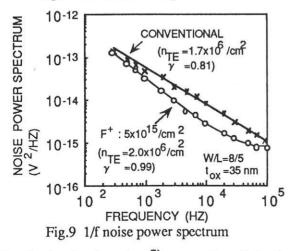

shown in Fig.9, because it inactivates the surface traps which generate 1/f noise.

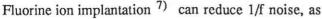

The calculated total noise charge is shown in Fig.10. The new structure roughly halves the noise charge.

## 4. CONCLUSION

The proposed device structure with the shallow p<sup>+</sup> isolation and the completely depleted well makes it possible to shrink the channel width of the vertical CCD by 40% while maintaining the high charge-handling capability. The combined use of tetrode transistor and fluorine implantation roughly halves the noise charge. These results indicate that the interline CCD has potential for HDTV applications.

#### 5. ACKNOWLEDGEMENTS

The authors wish to thank T.Nishida and the engineers in the Process Integration Center of the Central Research Laboratory for the process design and fabrication, and Dr. T. Masuhara for his continuous encouragement and useful suggestions.

#### 6. REFERENCES

1) I. Akiyama et al., "A 1280x980 Pixel CCD Image Sensor", in ISSCC Dig. Tech. papers, pp.96-97, Feb.1986.

2) K. Yonemoto et al., "A 2 Million Pixel FIT-CCD Image Sensor for HDTV Camera System", in ISSCC Dig. Tech. papers, pp.214-215, Feb. 1990

3) C. H. Sequin and M. F. Tompsett, Charge Transfer Devices : Academic Press, 1975, pp.140-144.

4) K. Ikeda et al.,"A 1/3-inch 360k-pixel IT-CCD Sensor", ITEJ Tech.Report vol.15, no.16, pp.31-36, IPU'91-13, CE'91-14 (Feb.1991)

5) M. H. White et al., "Characterization of Surface Channel CCD Image Arrays at Low Light Levels", IEEE Solid-State Circuits, vol. SC-9. no.1, pp.1-12, Feb.1974.

6) H. Ando et al., "A 1/2-inch CCD Imager with Low-Voltage Variable Shutter", in 1988 Symposium on VLSI Circuits Dig. Tech. papers, pp.123-124.

7) K. Ohyu et al., "Improvement of SiO2/Si Interface Properties Utilizing Fluorine Ion Implantation and Drivein Diffusion", Jap. J. of Appl. Phys. vol.28, No.6, June 1989, pp.1041-1045