# Electrical Properties of MOSFETs with N<sub>2</sub>O-Nitrided LPCVD SiO<sub>2</sub> Gate Dielectrics

J. Ahn, G. Q. Lo, and D. L. Kwong

Microelectronics Research Center Department of Electrical and Computer Engineering The University of Texas at Austin, Austin, TX 78712

In this paper, the electrical properties of MOSFETs with LPCVD SiO<sub>2</sub> nitrided in N<sub>2</sub>O ambient have been studied and compared to those with control thermal gate oxide. N<sub>2</sub>O-nitridation of CVD oxides combines the advantages of interfacial oxynitride growth and defect-less nature of CVD oxides. As a result, devices with N<sub>2</sub>O-nitrided CVD oxide show enhanced performance, improved reliability, and better TDDB property (t<sub>BD</sub>).

### I. INTRODUCTION

The as-deposited CVD oxide generally has inferior electrical properties for MOS gate dielectric applications due to large number of Si- and O-dangling bonds at the Si/SiO<sub>2</sub> interface <sup>1</sup>). Post-deposition annealing in O<sub>2</sub> and N<sub>2</sub> can improve CVD oxide characteristics which are close to or better than those of thermal oxide <sup>1-3</sup>) due to a thin thermal SiO<sub>2</sub> formation at the Si/SiO<sub>2</sub> interface. Meanwhile, it has been reported that the oxidation of Si in pure N<sub>2</sub>O ambient produces better quality oxide than thermal oxide due to [N]-incorporation at the Si/SiO<sub>2</sub> interface <sup>4-5</sup>). It can be expected that annealing of CVD SiO<sub>2</sub> in N<sub>2</sub>O not only densifies CVD SiO<sub>2</sub> but also grows interfacial Si<sub>x</sub>O<sub>y</sub>N<sub>z</sub> layer.

This paper reports performance and reliability of MOSFETs with thin (~87 Å) LPCVD gate oxides nitrided in N<sub>2</sub>O in comparison with those with controland N<sub>2</sub>O-nitrided thermal gate oxide. The devices with N<sub>2</sub>O-nitrided CVD oxide shows the best performance and TDDB characteristics, while their reliability is slightly inferior to those with N<sub>2</sub>O-nitrided thermal oxide but still better than those with control thermal oxide.

# II. EXPERIMENTAL

$N^+$  poly-Si gate n-MOSFETs were fabricated using CMOS twin-well technology and LOCOS isolation. N<sub>2</sub>O-nitrided CVD oxide (~87 Å) was prepared by LPCVD SiO<sub>2</sub> film at 450°C using SiH<sub>4</sub> and O<sub>2</sub> in a hotwall type multi-wafer reactor followed by furnace nitridation in pure N<sub>2</sub>O at 950°C for 10 min. Preparation of N<sub>2</sub>O-nitrided thermal oxide (~85 Å) was described in 6). For comparison, control oxide (~85 Å) was grown in furnace with dry  $O_2$  at 950°C followed by annealing in  $N_2$  at the same temperature. The thickness was measured by C-V technique on adjacent MOS capacitors and by ellipsometry. Thickness uniformities across the 4"-wafers were within  $\pm 2\%$  deviation for all oxides.

### **III. RESULTS AND DISCUSSION**

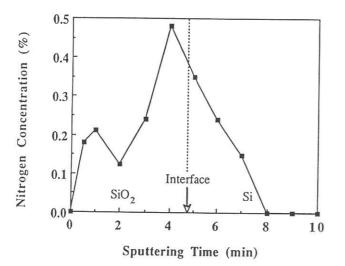

Fig. 1 shows an Auger Electron Spectroscopy (AES) depth profile of nitrogen in CVD oxide annealed in N<sub>2</sub>O at 950°C for 10 min. This profile shows a nitrogen peak at the Si/SiO<sub>2</sub> interface with a small amount of nitrogen in the bulk. This overall profile is similar to that of oxynitride film grown by thermal oxidation of Si in N<sub>2</sub>O ambient, although the nitrogen concentration in N<sub>2</sub>Oannealed CVD oxide is lower than that in oxynitride <sup>4</sup>). The thickness increase by annealing in N<sub>2</sub>O at 950°C for 10 min was ~25 Å by ellipsometric measurement and the thickness uniformity of the as-deposited CVD oxide was significantly improved by the annealing in N<sub>2</sub>O (within  $\pm 1.5\%$ ). A fixed refractive index (1.46) was used for ellipsometry because the [N] in the bulk oxide is small.

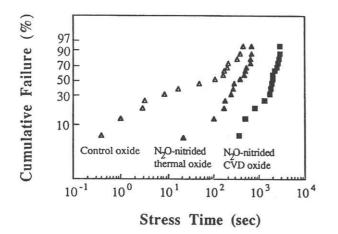

Fig. 2 shows time-to-breakdown ( $t_{BD}$ ) distributions of MOS capacitors with different gate dielectrics characterized by applying constant field stress (11.5 MV/cm). Capacitors with N<sub>2</sub>O-nitrided thermal and CVD oxides show much tighter distributions and higher  $t_{BD}$ values compared to those with control thermal oxide, implying much reduced weak oxide spots or defects through nitrogen incorporation at the interface <sup>5</sup>). Strained Si-O bonds, which are susceptible to the bond-

Fig. 1 AES depth profile of nitrogen for CVD oxide annealed in  $N_2O$  at 950°C for 10 min.

Fig. 2 Time-to-breakdown ( $t_{BD}$ ) distributions of MOS capacitors (area=  $5 \times 10^{-5} \text{ cm}^2$ ) with different gate dielectrics characterized by applying constant field stress (11.5 MV/cm)

breaking by hot-carriers, are reduced by interfacial  $Si_xO_yN_z$ -formation during N<sub>2</sub>O-nitridation. Because CVD oxide is deposited on rather than grown from the substrate without lattice match requirement <sup>7</sup>), N<sub>2</sub>O-nitrided CVD oxide has even less strained bonds and smaller number of defects which result in even higher t<sub>BD</sub> value than in N<sub>2</sub>O-nitrided thermal oxide.

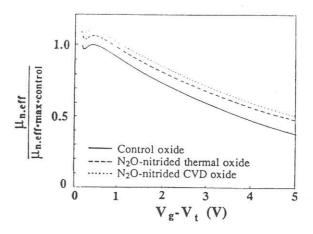

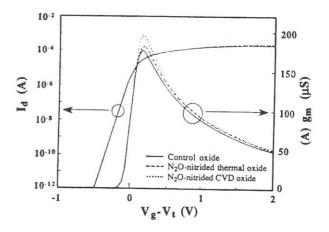

Effective electron mobilities, defined as  $\mu_{n,eff}$ = I<sub>d</sub>/[V<sub>d</sub>•W/L•C<sub>ox</sub>(V<sub>g</sub>-V<sub>t</sub>)], in MOSFETs (W<sub>eff</sub>/L<sub>eff</sub>=15 µm /15 µm) with different gate dielectrics are normalized to the peak  $\mu_{n,eff}$  of control oxide device and plotted in Fig. 3 as a function of gate drive (V<sub>g</sub>-V<sub>t</sub>). Both D<sub>it</sub> and subthreshold slopes (S) are similar in all devices (D<sub>it</sub>~  $5x10^{10}$  cm<sup>-2</sup>eV<sup>-1</sup> and S~70 mV/dec), as shown in Fig. 4. Fixed charge densities (N<sub>f</sub>) are  $5x10^{10}$  for control and N<sub>2</sub>O-nitrided thermal oxide devices and  $7x10^{10}$  cm<sup>-2</sup> for N<sub>2</sub>O-nitrided CVD oxide device. The slightly higher N<sub>f</sub> for CVD oxide may be a result of insufficient

Fig. 3 Normalized effective electron mobility  $(\mu_{n,eff}/\mu_{n,eff.max.control})$  as a function of  $(V_g-V_t)$  obtained from MOSFETs  $(W_{eff}/L_{eff}=15 \ \mu m / 15 \ \mu m)$  with different gate dielectrics

Fig. 4 I<sub>g</sub> vs. V<sub>g</sub> and g<sub>m</sub> vs. V<sub>g</sub> characteristics of submicron MOSFETs (W<sub>eff</sub>/L<sub>eff</sub>=15 μm/0.8 μm) with different gate dielectrics.

densification. The improvement factors of  $\mu_{n,eff}$  over control oxide are ~10% for N2O-nitrided CVD oxide and ~7% for N<sub>2</sub>O-nitrided thermal oxide. The dependence of  $\mu_{n,eff}$  on  $V_g$ - $V_t$  is similar for all devices. It has been reported that  $\mu_{n,eff}$  and  $g_m$  can be improved for all  $V_g$  by applying mechanical tensile stress to the thermal oxide which has residual compressive stress 8). An interfacial Si<sub>x</sub>O<sub>y</sub>N<sub>z</sub> formation with low nitrogen concentration ([N]<sub>int</sub>~0.5-1.5%) during N<sub>2</sub>O-nitridation, which is believed to result in less strained interface structure than control thermal oxide interface, without any noticeable increase of Nf or Dit. Excessive nitrogen at SiO2/Si interface, however, has been reported to degrade device performance (reduced  $\mu_{n,eff}$  and  $g_m$  at low  $V_g$ ) in NH<sub>3</sub>nitrided thermal oxide devices 8-10). Recent study showed that very light NH3-nitridation ([N]int ~0.5%) can solve this problem 11). We believe that the improved  $\mu_{n,eff}$  in N<sub>2</sub>O-nitrided CVD oxide is a combined effect of

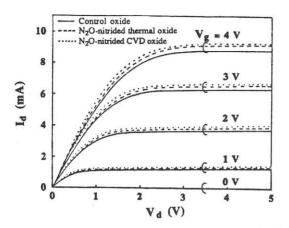

Fig. 5 Current drivability  $(I_d vs. V_d)$  of submicron MOSFETs with different gate dielectrics.

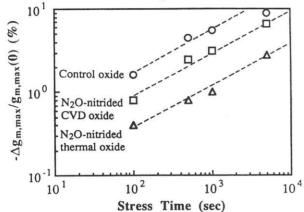

Fig. 6 Stress-time dependence of  $g_m$  degradation of submicron MOSFETs induced by channel hot carrier stress with  $I_{sub,max}$  ( $V_g$ = 2.5 V,  $V_d$ = 7.5 V)

interfacial oxynitride layer growth ( $[N]_{int} \sim 0.5\%$ ) and strainless nature of CVD SiO<sub>2</sub>/Si interface <sup>12</sup>). As a result, current drivability is also improved in both high and low V<sub>g</sub> ranges, as shown in Fig. 5.

Fig. 6 shows peak- $g_m$  degradation vs. stress time in MOSFETs ( $W_{eff}/L_{eff}=15\mu m/0.8 \mu m$ ) during channel hot carrier stress (CHCS) with I<sub>sub,max</sub>. MOSFETs with N<sub>2</sub>O-nitrided thermal and CVD oxides show suppressed  $\Delta g_m$  than MOSFETs with control thermal oxide. The  $\Delta D_{it}$  during CHCS may be due to a direct bond breaking process at the interface. Substitution of strained Si-O bonds with stronger Si-N bonds during N<sub>2</sub>O-nitridation <sup>6)</sup> is believed to improve interface hardness, resulting in less  $\Delta g_m$ . The suppression is less significant in N<sub>2</sub>Onitrided CVD oxide than in N<sub>2</sub>O-nitrided thermal oxide due to smaller amount of Si-N bonds at the interface ([N]<sub>int</sub>~0.5% for N<sub>2</sub>O-nitrided CVD oxide vs. [N]<sub>int</sub>~1.5% for N<sub>2</sub>O-nitrided thermal oxide) <sup>11</sup>).

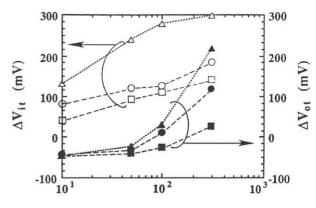

Fowler-Nordheim (F-N) current stress was also performed on MOSFETs, and result shows the same trend in  $\Delta g_m$  and threshold voltage shift ( $\Delta V_t$ ) as in CHCS. In Fig. 7 contributions of  $\Delta D_{it}$  ( $\Delta V_{it}$ ) and charge trapping ( $\Delta V_{ot}$ ) to  $\Delta V_t$  were separated by using

Stress Time (sec)

Fig. 7 Fraction of threshold voltage shift  $(\Delta V_t)$  due to  $\Delta D_{it}$  ( $\Delta V_{it}$ ) and charge trapping ( $\Delta V_{ot}$ ) under F-N constant current injection on submicron MOSFETs with control (triangle), N<sub>2</sub>O-nitrided CVD (circle), and N<sub>2</sub>O-nitrided thermal oxide (square).

subthreshold slope change ( $\Delta S$ ), *i.e.*,  $\Delta V_{it} = \Delta S \cdot \Phi_B / [kT/q \cdot ln10]$  and  $\Delta V_{ot} = \Delta V_t \cdot \Delta V_{it}$ , where  $\Phi_B = 2\Phi_F = 2kT/q \cdot ln (N_a/n_i)^{13}$ . As can be seen, both  $\Delta D_{it}$  and electron trapping are suppressed in N<sub>2</sub>O-nitrided oxides compared to control thermal oxide.

### **IV. CONCLUSION**

$N_2O$ -nitridation of CVD oxide combines the advantages of defect-less nature of CVD oxide, and the strainless interfacial oxynitride growth and densification effects of  $N_2O$ -nitridation. As a result, MOS devices with this gate dielectric exhibit improved performance, enhanced reliability, and improved TDDB characteristics compared to those with control thermal gate oxide.

This work was supported by SRC/SEMATECH and Texas Advanced Technology Program

### REFERENCES

- S. Ang and S. Wilson, J. Electrochem. Soc., 134, 1987, 1254

- 2) J. Lee et al., IEEE Electron Device Lett., 1986, 506

- 3) J. Lee et al., IEEE Electron Device Lett., 1988, 324

- 4) H. Hwang et al., in IEDM Tech. Dig., 1990, 421

- 5) W. Ting et al., *IEEE Electron Device Lett.*, 1991, 416

- 6) J. Ahn et al., IEEE Electron Device Lett., 1992, 117

- 7) J. Ahn et al., *IEEE DRC*, 1991, IVB-1

- 8) H. Momose et al., in IEDM Tech. Dig., 1990, 65

- 9) M. Schmidt et al., IEEE Electron Dev., 1988, 1627

- 10) T. Hori and H. Iwasaki, in *IEDM Tech. Dig.*, 1989, 459

- 11) H. Momose et al., in IEDM Tech. Dig., 1991, 359

- 12) J. Ahn et al., IEEE Electron Device Lett., 1992, 186

- 13) R. Sundaresan et al., *IEEE Trans. Nucl. Sci.*, 1986, 1223