## A Novel Fabrication Method for Poly-Si TFTs with a Self-Aligned LDD Structure

K.Kobayashi, H.Murai, T.Sakamoto, H.Tokioka, T.Sugawara, Y.Masutani, H.Namizaki, and M.Nunoshita

Materials and Electronic Devices Lab., Mitsubishi Electric Corporation. 8-1-1, Tsukaguchi-Honmachi, Amagasaki, Hyogo 661, Japan.

In active matrix liquid crystal displays using poly-Si TFTs, one of the main subjects is to decrease their OFF currents<sup>(1)</sup>. Poly-Si TFTs with a lightly doped drain(LDD) structure have been widely investigated<sup>(2)</sup>. However, it has a drawback of requirements of an additional photo-mask and precise mask alignment.

In order to solve these problems, we have developed a novel fabrication method for poly-Si TFTs with a self-aligned LDD structure. Our method is applied a lateral etching of n<sup>+</sup> Si film to make a LDD region. The lateral etching is caused by dry etching in patterning process of gate electrode. The method makes it possible to realize the self-aligned LDD structure by a simple process and it results in poly-Si TFTs with a high ON/OFF ratio.

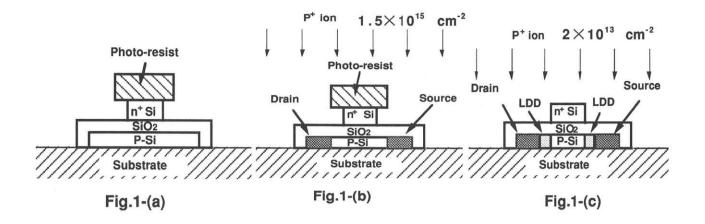

The poly-Si TFTs were fabricated on a quartz substrate. A 100nm thick amorphous Si film, deposited by LPCVD at 480 °C using Si<sub>2</sub>H<sub>6</sub> gas, was crystallized at 625 °C for 6 h. A poly-Si film with a relatively large grain size of 1-2  $\mu$ m was obtained. A 72nm thick gate oxide was formed by thermal oxidation at 950 °C. In order to realize the self-aligned LDD structure, the following novel process was employed. First, after a photo-resist for the gate electrode was formed on a 300nm thick n<sup>+</sup> Si film, the n<sup>+</sup> Si film was etched using SF<sub>6</sub> gas by a reactive ion etching (RIE) method. The conditions of the RIE were an RF power of 200W and a gas pressure of 40 mTorr. Since SF<sub>6</sub> gas results in isotropic etching, a lateral etching of the n<sup>+</sup> Si film occurs under the photo-resist by an over etching (undercut) (Fig.1-(a)). Second, P<sup>+</sup> ions were implanted at a dose of 1.5 $\times$ 10<sup>15</sup> cm<sup>-2</sup> to form the source and drain using the photo-resist as a mask(Fig.1-(b)). Next, the photo-resist was removed and the second ion implantation at a dose of 2 $\times$ 10<sup>13</sup> cm<sup>-2</sup> was followed to make the LDD region (Fig.1-(c)). The above-mentioned novel process results in the self-aligned LDD structure. The source/drain electrodes were fabricated with Cr/Al metals and hydrogenation was performed efficiently using an ECR plasma process.

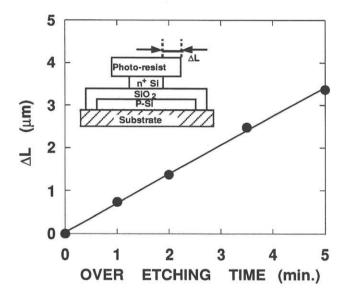

Fig.2 shows dependence of the undercut length ( $\Delta L$ ) on the over etching time. Here, the over etching time was counted from an end point of the dry etching of n<sup>+</sup> Si films. The end point was detected by plasma emission of F\* (704nm). The undercut by the lateral etching of n<sup>+</sup> Si film was confirmed by SEM. As shown in the figure, the  $\Delta L$  is proportional to the over etching time. It is concluded that the  $\Delta L$ , which is equal to LDD length, can be precisely controlled by the over etching time.

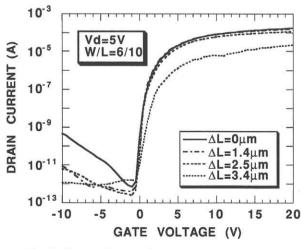

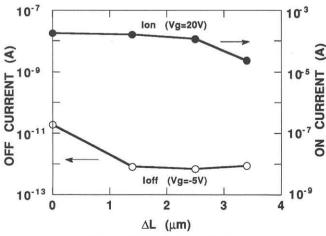

Fig.3 indicates the dependence of drain current on the gate voltage (Vg) as a function of the  $\Delta L$ . At the  $\Delta L=0\mu m$ , the field effect mobility of the poly-Si TFT is as high as  $80\text{cm}^2/\text{V} \cdot \text{s}$  and the OFF current at Vg=-5V is about  $10^{-11}\text{A}$ . Adoption of our LDD structure with  $\Delta L>1.4\mu m$  decreases the OFF current at a reverse bias by more than one order of magnitude, as shown in the figure. At this time, a drastic decrease of the ON current and a significant decrease of the sub-threshold slope are not observed until the  $\Delta L$  reaches 3.4 $\mu m$ . Fig.4 shows the OFF current (Ioff) at Vg=-5V and the ON current (Ion) at Vg=20V as a function of the  $\Delta L$ . The Ion is an almost constant for  $\Delta L<2.5\mu m$ . On the other hand, the Ioff has an almost constant value as low as  $10^{-12}$  A in the range of 1.4 $\mu m<\Delta L<3.3\mu m$ . Therefore, it is concluded that the range of 1.4 $\mu m<\Delta L<2.5\mu m$  is at least effective to realize poly-Si TFTs with a high ON current and a low OFF current. As shown in Fig.2, our novel fabrication method has a time tolerance (about 90 s) enough to control the  $\Delta L$  from 1.4 $\mu m$  to 2.5 $\mu m$ . Then, this method gives us high reproducibility for fabricating such a self-aligned LDD structure.

In conclusion, we have succeeded to develop a novel process for the self-aligned LDD structure, which leads to the decrease of the OFF current by more than one order of magnitude without an additional photo-mask process.

## REFERENCES

- (1) Y.Matsueda, M.Ashizawa, S.Aruga, H.Ohshima, and S.Morozumi, Proc. Ninth IDRC, Kyoto, 1989, P418.

- (2) K.Nakazawa, K.Tanaka, S.Suyama, K.Kato, and S.Kohda, Proc. SID, 1990 P.311.

Fig.1 A novel fabrication process for poly-Si TFTs with a self-aligned LDD structure.

Fig.2 Dependence of undercut length(ΔL) on over etching time.

Fig.3 Dependence of drain current on gate voltage as a function of  $\Delta L$  at a drain voltage (Vd) of 5V.

Fig.4 ON and OFF currents as a function of △L.