# A Poly-Si TFT Process for High Speed and Low Voltage CMOS Circuits

#### Y.Fukushima, T.Ueda, and H.Komiya SHARP CORPORATION 2613-1, Ichinomoto, Tenri, Nara 632, Japan Tel(07436)5-1321; Fax(07436)5-4081

A poly-Si TFT process for high speed and low voltage CMOS circuits which is applicable to HDTV LCDs with integrated drivers has been developed. The defects in the poly-Si film are extremely reduced by the annealing in  $O_2$ ambient ( $O_2$  annealing) after the solid phase crystallization of LPCVD  $\alpha$ -Si. The field effect mobilities of NMOS and PMOS TFTs are 140cm<sup>2</sup>/Vs and 110cm<sup>2</sup>/Vs, respectively. The CMOS shift registers operate at frequencies as high as 35MHz under a supply voltage of 14V. By reducing the gate length, the maximum frequency of 9.5MHz is achieved under a supply voltage as low as 5V.

#### 1.Introduction

In recent years, there has been a strong demand for practical HDTV LCD systems<sup>(1) (2)</sup>. The high temperature poly-Si TFT process is one of the promising candidates for very small and high resolution **LCDs** fully with integrated HDTV drivers, especially for projector because of the availability of VLSI technology and the simplicity of the poly-Si film formation compared with that of the low temperature process. However, more superior characteristics of poly-Si TFTs for HDTV for those of conventional systems than electronic viewfinders are yet required. Namely the grain size of poly-Si film should not only be enlarged, which is usually done by solid phase crystallization (SPC) of a-Si film, but also the defect density in poly-Si film should be reduced.

In this work, we have successfully developed a poly-Si TFT CMOS process to HDTV-class LCDs with fully applicable integrated drivers. The effects of  $O_2$ annealing on the reduction of defects in the poly-Si film after SPC are examined by the characterization of poly-Si crystallinities and the evaluation of device performance. the CMOS shift registers Further are  $O_2$ fabricated by this process including annealing to evaluate the applicability to high speed and low voltage CMOS circuits.

### 2.Experiments

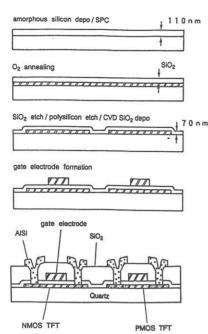

High quality poly-Si film formation consists of two steps, i.e., SPC in order to enlarge the grain size and following  $O_2$ annealing to decrease the defects, which is schematically illustrated in Fig.1. The

starting material is an 110nm thick a-Si film deposited on a quartz substrate by LPCVD (low-pressure chemical vapor deposition) using Si<sub>2</sub>H<sub>6</sub> as a source gas at 450°C. In the first step, an  $\alpha$ -Si film is crystallized at 600°C for 24 hours in N<sub>2</sub> ambient (SPC). Subsequently, the poly-Si film is annealed at 1050°C in O2 ambient (O2 annealing). After O2 annealing, oxide on the surface of poly-Si is removed and then the device regions are patterned. A 85nm thick CVD (HTO) high temperature oxide is deposited at 850℃ dielectric as a gate film. After gate electrodes are patterned, phosphorus and boron ions are implanted into the source and drain regions of NMOS and PMOS TFTs, respectively, which are self-aligned to the gate electrodes. Final gate electrodes. the Final passivation of all devices is performed by hydrogen diffusion from PECVD SiN to bonds terminate the dangling during а subsequent annealing at 420°C after AI metallization. By using this process, which is optimized by the following analyses, the CMOS shift registers are fabricated to prove the circuit performance.

Poly-Si films are characterized as follows.  $O_2$  annealing time is varied from characterized as 12min. to 120min., when oxide thickness is from 35nm to 130nm., to investigate the effects on the reduction of defects in the A poly-Si polv-Si film. film is also annealed in N2 ambient (N2 annealing) at 1050°C for 30min. after SPC to compare with the effects of O<sub>2</sub> annealing. The structures poly-Si films observed of are by transmission electron microscope (TEM) to evaluate the grain size and the defects. Electron spin resonance (ESR) is used to determine the defect density originated

from dangling bonds in poly-Si films. The surface roughness of poly-Si films is measured by atomic force microscope (AFM) after  $O_2$  annealing.

### 3.Results and Discussion

Fig.2 shows TEM photographs of poly-Si films after SPC,  $O_2$  and  $N_2$  annealing, respectively. The grain size of poly-Si film after SPC is well enlarged and its maximum size is a few microns shown in Fig.2(a). There is no change of the grain size, but the fine structures in the grains and at the grain boundaries disappear specially after  $O_2$  annealing for 37min. compared with  $N_2$ annealing for 30min. at 1050°C shown in Fig.(b) and (c), respectively. It means that the defects after  $O_2$  annealing are less than that after  $N_2$  annealing.

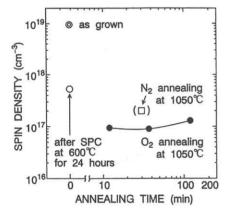

Fig.3 shows the spin density of poly-Si film obtained from ESR as a function of annealing time. The spin density decreases from  $1 \times 10^{19}$  cm<sup>3</sup> to  $5 \times 10^{17}$  cm<sup>3</sup> after SPC and dramatically decreases to less than  $1 \times 10^{17}$  cm<sup>3</sup> after O<sub>2</sub> annealing. It reaches to  $8 \times 10^{16}$  cm<sup>3</sup> of minimum density at 37min. and over that it slightly increases with the increase of O<sub>2</sub> annealing time. The spin density after N<sub>2</sub> annealing at 1050°C for 30min. is  $2 \times 10^{17}$  cm<sup>-3</sup>. O<sub>2</sub> annealing is more effective in the reduction of defects than N<sub>2</sub> annealing.

The mechanism of  $O_2$  annealing is assumed as follows. During  $O_2$  annealing, unoxidized Si interstitials formed by a small fraction of excess silicon atoms near Si-SiO<sub>2</sub> interface<sup>(3)</sup> quickly diffuse into the poly-Si film and reduce the defects existed at the grain boundaries and in the grains.

However, it is afraid that the increase of surface roughness of poly-Si films during  $O_2$  annealing is caused by the difference of oxidation rate between the grain boundaries and each grain. The surface roughness obtained from AFM after  $O_2$  annealing is shown as a function of annealing time in Fig.4. The surface of poly-Si film after SPC is very smooth and its roughness is a few angstroms. The surface roughness is a few angstroms. The surface roughness is a shout 10Å for shorter than about 40min. For over that it gradually increases.

In summary of the analyses above mentioned,  $O_2$  annealing is extremely effective in the reduction of defects in poly-Si films. But excessive  $O_2$  annealing increases the surface roughness and reduces the controllability of the fabrication process with the decrease of poly-Si thickness. The optimum  $O_2$  annealing time is around 40min. at 1050°C.

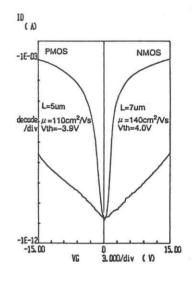

The characteristics of NMOS and PMOS TFTs fabricated by using  $O_2$  annealing for 37min. at 1050°C, when oxide thickness is about 60nm, are measured. Fig.5 shows the drain current (ID) versus gate voltage (VG) characteristics of NMOS and PMOS TFTs with gate width of 20 $\mu$ m and gate lengths(Ln,Lp) of 7 $\mu$ m and 5 $\mu$ m, respectively. The field effect mobilities and threshold voltages of NMOS and PMOS TFTs are 140 cm<sup>2</sup>/Vs, 4.0V and 110cm<sup>2</sup>/Vs, -3.9V, respectively. High performance for both type of TFTs accomplishes high speed operation of CMOS circuits.

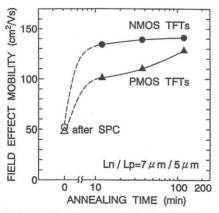

Fig.6 shows the field effect mobilities of NMOS and PMOS TFTs as a function of  $O_2$  annealing time. The field effect mobilities of both type of TFTs fabricated by  $O_2$  annealing are very large and over  $100 \text{cm}^2/\text{Vs}$ . They slightly improve with increasing  $O_2$  annealing time. These results are explained by the reduction of the defects in poly-Si characterized by TEM and ESR analyses.

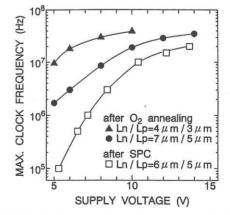

The characteristics of the CMOS shift registers fabricated by the process including  $O_2$  annealing are measured. Fig.7 shows the maximum clock frequencies of CMOS shift registers as a function of supply voltage. The devices with  $O_2$  annealing are much faster than those without annealing after SPC. When the supply voltage is 14V, the maximum clock frequencies in excess of 35MHz are achieved at gate lengths of Ln=7µm and Lp=5µm. Decreasing gate lengths to Ln=4µm and Lp=3µm, the maximum clock frequency of shift registers increases to 9.5MHz under a supply voltage as low as 5V.

## 4.Conclusion

$O_2$  annealing of the poly-Si film with large grain size obtained by SPC of LPCVD  $\mathfrak{a}$ -Si using Si<sub>2</sub>H<sub>6</sub> as a source gas is greatly effective in the reduction of the defects. The field effect mobilities of NMOS and PMOS TFTs fabricated by using this technique are as high as 140cm<sup>2</sup>/Vs and 110cm<sup>2</sup>/Vs, respectively. The characteristics of the CMOS shift registers prove the capability for the high speed and low voltage CMOS circuits composed of these TFTs. This CMOS process certainly promises very small and high resolution LCDs with integrated drivers such as HDTV LCDs.

## Acknowledgement

The authors wish to thank T.Degawa, S.Hideshima, and A.Nakano for their help in processing and testing support, and analyses of crystalinities of poly-Si films. The authors also wish to thank Dr.Y.Takafuji for his extensive discussion.

## REFERRENCES

- (1) Y.Takafuji et al.,SID 93 DIGEST, p.383 (1993)

- (2) Y.Matsueda et al., Proc. 12th. IDRC(JAPAN DISPLAY '92), p561(1992)

- (3) S.M.Hu, J.Appl. Phys. Vol. 45, p. 1567(1974)

Fig.1 The fabrication process flow.

(c) (b) 0.5µm (a)

Fig.2 TEM micrographs of poly-Si film after SPC,  $O_2$  and  $N_2$  annealing. (a)SPC at 600°C for 24h. (b)SPC at 600°C for 24h and  $O_2$  annealing at 1050°C for 37min. (c)SPC at 600°C for 24h and  $N_2$  annealing at 1050°C for 30min.

Fig.3 The spin density of poly-Si film as a function of annealing time.

Fig.4 The surface roughness after  $O_2$  annealig at 1050°C as a function

Fig.5  $I_p$ -V<sub>G</sub> characteristics of NMOS and PMOS TFTs at |Vds|=10V. (W=20 µ m)

Fig.6 The field effect mobilities of NMOS and PMOS TFTs as a function of O2 annealing time. O2 annealing at 1050°C.

of annealing time.