Extended Abstracts of the 1993 International Conference on Solid State Devices and Materials, Makuhari, 1993, pp. 996-998

# High Performance Polysilicon Thin-Film Transistors Using Very Thin Sputtered Gate Oxide Films

Noriyoshi Yamauchi, Nobuhiko Kakuda and Tomoko Hisaki

NTT Interdisciplinary Research Laboratories, 3-9-11 Midori-cho, Musashino-shi, Tokyo, 180 Japan.

Polysilicon thin-film transistors with with various gate oxide thicknesses from 94 to 12 nm using sputter-deposited SiO<sub>2</sub> films were fabricated and their electrical characteristics were studied. The gate SiO<sub>2</sub> film was deposited by magnetron sputtering at 200°C using a mixture of Ar and O<sub>2</sub> as a sputtering gas. The polysilicon TFT with a 12-nm gate SiO<sub>2</sub> film showed excellent characteristics: threshold voltage of 0.4 V, subthreshold slope of 140 mV/dec, field effect mobility of 77 cm<sup>2</sup>/Vs and the gate oxide breakdown voltage of 22 V. These results indicate a possibility of improving polysilicon TFT circuit performance by scaling down the device structure.

## 1. INTRODUCTION

Although some studies on polysilicon thin-film transistors (TFTs) with reduced channel dimensions have been done  $^{1-5)}$ , the full potential of achieving higher performance by reducing the gate oxide thickness has not been extensively investigated in polysilicon TFTs because of the difficulties in obtaining very thin gate oxide films keeping high quality for the gate insulator.

A sputter-deposited SiO<sub>2</sub> films using Ar and O<sub>2</sub> mixture as a sputtering gas have been developed by Suyama et al previously to achieve lower process temperature. <sup>6-14)</sup> Superior TFT characteristics comparable or even better than those of thermally grown SiO<sub>2</sub> have been achieved in polysilicon TFTs using the SiO<sub>2</sub> films with 100 nm thickness. It has also been shown that the sputtered SiO<sub>2</sub> shows high dielectric breakdown strength even when the thickness is reduced to 3.5 nm. <sup>15</sup>)

In this work, we have fabricated and characterized polysilicon TFTs with the sputter-deposited gate oxide films of various thicknesses, including 12 nm which is the thinnest, to explore the possibility of scaling down the gate oxide thickness.

## 2. DEVICE FABRICATION

The polysilicon TFTs were fabricated on fused quartz substrate using the following process. Original polysilicon thin films were deposited from  $Si_2H_6$  at 470

°C using the LPCVD method. The polysilicon film was then thermally annealed for 15 hours at 600°C for solidphase crystallization <sup>16</sup>). It was then annealed at 800°C for 30 min. The resulting polysilicon films have grain sizes around 1 µm. After the polysilicon island formation, SiO2 films with thicknesses ranging from 94 to 12 nm were deposited by the magnetron sputtering method at 200°C using an oxygen-argon mixture (30 % oxygen concentration, 5 mTorr) as a sputtering gas 6-15). The deposition rate was 1.2 to 1.4 nm/min. The gate oxide thickness were measured on control Si wafers using elipsometry. A phosphorus-doped polysilicon film deposited by the LPCVD method was used as gate electrode. Source and drain regions were formed by phosphorus ion implantation followed by thermal activation at 800℃. The TFTs were completed after interlayer SiO<sub>2</sub> film deposition by magnetron sputtering, contact hole formation using reactive ion etching and metallization using consecutive DC magnetron sputtering of Mo and Al films.

# 3. RESULTS AND DISCUSSION

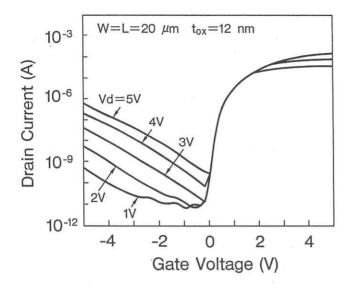

The TFT characteristics were measured and their gate oxide thickness dependency was investigated. Figure 1 shows the drain-to-source current vs. gate voltage curves of a polysilicon TFT with 12 nm gate oxide for different drain voltages. It is clearly seen that high on to off current rartio of about  $10^6$  is obtained at the drain-to-source voltage of 5 V.

Fig. 1. Drain current vs. gate voltage curves in the polysilicon with a 12-nm- thick gate oxide.

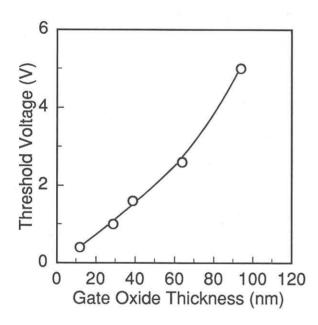

Fig. 2. Threshold voltage dependence on the gate oxide thickness.

Figure 2 shows the dependency of the threshold voltage on the gate oxide thickness. As expected, the threshold voltage shows linear decrease for smaller gate oxide thicknesses.

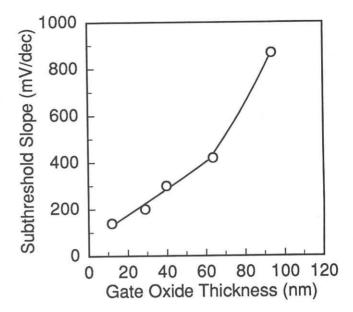

Figure 3 shows the relationship of subthreshold slope and gate oxide thickness. The subthreshold slope shows a remarkable steepening as the gate oxide thickness is reduced.

The subthreshold slope S can be expressed as a function of the depletion-layer capacitance  $C_D$ , the capacitance  $C_{it}$  which is associated with the trap-density, and the gate oxide capacitance  $C_i$  as follows, <sup>17</sup>

Fig. 3. Subthreshold slope dependence on gate oxide thickness.

$$S = (kT \cdot \ln 10/q) \cdot [1 + (C_D + C_{it})/C_i]$$

(1)

where k is the Boltzman constant, T is the temperature and q is the electron charge. The subthreshold slope decreases linearly as the gate oxide thickness is reduced from 64 nm to 12 nm. This indicates that the trap density is constant at least in the above gate oxide thickness range.

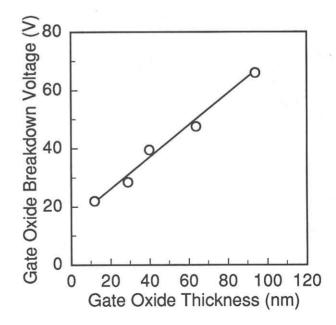

Breakdown voltage is a crucial factor that determines the applicable supply voltages. As shown in Fig. 4, it decreases with the gate oxide thickness.

Fig. 4. Gate oxide breakdown voltage dependence on gate oxide thickness.

997

However, the relation of the breakdown voltage with the thickness is sub-linear indicating higher tolerance to electric field values in small gate oxide thicknesses.

The electrical characteristics of the TFT with 12 nm gate oxide is summarized in Table 1. Excellent characteristics such as threshold voltage of 0.4 V, subthreshold slope of 140 mV/dec and field effect mobility of 77 cm<sup>2</sup>/Vs are achieved. These threshold and subthreshold characteristics are much favorable for scaled down TFTs which are supposed to be used with lower supply voltages. The breakdown voltage of 22 V allows implementation of TFT integrated circuits using a 5 V supply voltage with enough margin.

| TABLE I. | Characteristics of the polysilicon TFT with |  |

|----------|---------------------------------------------|--|

| a 12 i   | nm thick gate oxide.                        |  |

| Threshold Voltage     | 0.4 V                  |

|-----------------------|------------------------|

| Subthreshold Slope    | 140 mV/dec             |

| Field Effect Mobility | 77 cm <sup>2</sup> /Vs |

| On/Off Ratio (Vd=5 V) | 106                    |

| Gate-Oxide Breakdown  |                        |

| Voltage               | 22 V                   |

### 4. CONCLUSION

We have demonstrated that high performance polysilicon TFTs are possible with very thin sputterdeposited  $SiO_2$  films. We believe that this is the first report on a polysilicon TFT with deposited gate oxide film as thin as 12 nm. The results obtained in this work for thin oxide TFTs are very encouraging for circuit applications. With scaled down design, we can expect TFT integrated circuits with sophisticated processing functionality comparable with silicon VLSIs. Combining this functionality and polysilicon TFTs ' unique feature that they can be built on insulating and optically transparent substrates, we believe that new applications such as parallel optoelectronic switching and processing systems will become possible in which analog and/or digital processing is done in high performance polysilicon TFT circuits.<sup>18)</sup>

#### REFERENCES

- A. G. Lewis, I-W. Wu, T. Y. Huang, M. Koyanagi, A. Chiang and R. Bruce, IEDM Tech. Dig., (1988) 260.

- A. G. Lewis, T. Y. Huang, I-W. Wu, R. Bruce and A. Chiang, IEDM Tech. Dig. (1989) 349.

- N. Yamauchi, J.-J. J. Hajjar and Rafael Reif, IEEE Electron Devices Lett. <u>11</u> (1990) 15.

- N. Yamauchi, J.-J. J. Hajjar and Rafael Reif, IEEE Trans. Electron Devices <u>38</u> (1991) 55.

- 5) N. Yamauchi, J.-J. J. Hajjar and Rafael Reif, IEEE Trans. Electron Devices 38 (1991)1967.

- S. Suyama A. Okamoto and T. Serikawa, IEEE Trans. Electron Devices <u>ED-34</u> (1987) 2124.

- 7) S. Suyama, A. Okamoto and T. Serikawa, J. Electrochem. Soc. <u>134</u> (1987) 2260.

- S. Suyama, A. Okamoto, T. Serikawa and H. Tanigawa, J. Appl. Phys. <u>62</u> (1987) 2360.

- 9) S. Suyama, A. Okamoto and T. Serikawa, J. Electrochem. Soc. <u>135</u> (1988) 3104.

- S. Suyama, A. Okamoto and T. Serikawa, Appl. Surface Science, 33/34 (1988) 1236.

- S. Suyama, A. Okamoto S. Shirai and T. Serikawa, Mat. Res. Soc. Symp. Proc. <u>146</u> (1989) 301.

- 12) T. Serikawa, S. Shirai, A. Okamoto and S. Suyama, Jpn. J. Appl. Phys. <u>28</u> (1989) L1871.

- 13) T. Serikawa, S. Shirai, A. Okamoto and S. Suyama, IEEE Trans. Electron Devices 36 (1989) 1929.

- 14) S. Suyama, A. Okamoto and T. Serikawa, J. Appl. Phys. <u>65</u> (1989) 210.

- 15) S. Suyama, A. Okamoto, S. Shirai and T. Serikawa, Proc. 2nd Int. Symp. on Sputtering and Plasma Process, (1993) 263.

- 16) K. Nakazawa, J. Appl. Phys. 69 (1991) 1703.

- M. S. Sze, "Physics of semiconductor devices", 2nd edition, Chapt. 8, Wiley-Interscience, 1981

- N. Yamauchi, Y. Inaba and M. Okamura, IEEE Photonics Technol. Lett. <u>5</u> (1993) 319.