# New Scaling Scenario for Channel Hot Electron Type Flash EEPROM

S. Ueno, H. Oda, N. Ajika, M. Inuishi and N. Tsubouchi

ULSI Laboratory, Mitsubishi Electric Corporation 4-1 Mizuhara, Itami, Hyogo 664 JAPAN

The new scaling rule of flash EEPROM is presented to keep the programming current constant. In the new scaling rule, the concept of PBC (Programming Best Condition) is introduced to discuss the programming time by using the maximum gate current. Using PBC concept, it is clarified that there exists the scaling limitation for the drain, the gate and the swing voltage. Moreover it is derived that the supply voltage after scaling should be reduced by the scaled difference between the voltage before scaling and the limitation, to keep the programming current constant.

#### [Introduction]

Many scaling theories of MOSFETs have been evolved to improve performance and packing density. However scaling methodology of flash EEPROM has not been thoroughly discussed, yet<sup>1)</sup>. In this paper, the new scaling scenario is proposed, including the concept of PBC ( Programming Best Condition ). PBC means the applied voltage condition where the programming time becomes shortest. In this scenario, there exists the scaling limitation for the drain, the gate and the swing voltage. So the voltages can not be simply scaled by 1/kaccording to the scaling factor k (>1) . Instead, the voltage shift from the limitation should be scaled to keep the programming current constant.

#### [ Programming Best Condition (PBC) ]

The programming time is analytically calculated from equation 1 which expresses charging the capacitance.

Programming Time =

$$C_t \int_{V_{end}}^{V_{start}} \frac{dV_{fg}}{I_g(V_{fg})}$$

(1)

The charge balance equation 2 in the EPROM structure is given by

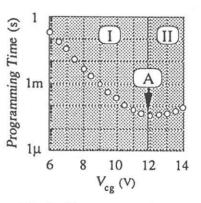

Fig. 1: Programming time dependence on V<sub>cg</sub>.

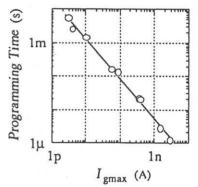

Fig. 2: The relationhsip between *Programming time* and Igmax under PBC.

$$Q_{fg} = C_{fc} (V_{fg} - V_{cg}) + C_{fd} (V_{fg} - V_{d}) + C_{fs} (V_{fg} - V_{s}) + C_{fb} (V_{fg} - V_{s} - V_{th})$$

(2)

Figure 1 shows the programming time versus the control gate voltage using these equations 1 and 2. In the region I of figure 1, the programming time reduces with increasing control gate voltage, since the gate current increases due to the oxide field favoring the hot carrier injection. On the other hand, in the region II, the programming time increases, because the gate current reduces due to decrease in the electric field near the drain junction. There exists minimum programming time for a certain gate bias as shown figure 1. This is due to the largest gate current for this bias condition. We call this PBC (Programming Best Condition). It should be noted that the programming time under PBC is exponentially proportional to the maximum gate current as shown in figure 2. Hence, the scaling scenario under PBC can be discussed in terms of the maximum gate current with respect to the drain voltage and the impurity concentration. Moreover, under PBC (*Igmax* condition), the gate voltage is linearly related to the drain voltage. Therefore, the gate voltage is scaled, when the drain voltage is reduced.

### [ Gate Current Characteristics ]

At first, we have to clarify the relationship between the maximum gate current and the drain voltage or the impurity concentrations for discussing the scaling scenario. Based on the lucky-electron model <sup>2)</sup>, the gate current can be expressed as

A 17

$$I_{g} = I_{d} P(E_{ox}) \left(\frac{\psi \ b \ L_{m}}{\lambda}\right)^{2} exp \left(\frac{\lambda}{\psi \ b \ L_{m}}\right) (3)$$

(a) 1

(b) 1k

(c) 1k

(c) 4

(

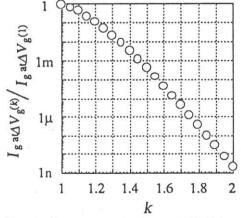

Fig. 3: The sensitivity of  $I_{gmax}$  to the (a) drain voltage  $V_d$ , (b) impurity concentrations  $N_a$  and (c) the shift of gate voltage  $\Delta V_g$ .

where  $\lambda$  is the optical phonon mean free pass and  $\phi_b$  is the effective barrier height. Em is the maximum lateral electric field, which is derived using quasi-two dimensional analysis as follows.

$$E_{\max} = \frac{V_{\rm d} - V_{\rm dsat}(N_{\rm a})}{\ell} \tag{4}$$

Where  $V_{dsat}$  is the saturation drain voltage, which is proportional to  $N_a$  by solving the Poisson's equation at velocity saturation region <sup>3</sup>). Figure 3(a) shows the normalized  $I_{gmax}$  ( $I_g(k)/I_g(1)$ ), when the drain voltage is scaled by k (Vd/k). The  $I_{gmax}$  is proportional to k, because the gate current is proportional to 1/Vd. And it is derived that the sensitivity of the  $I_{gmax}$  (SVd), when the Va is scaled, is expressed as follows by the least square fitting in figure 3(a).

$$log\left(\frac{I_{gmax}(k)}{I_{gmax}(1)}\right) = S_{V_{d}} = -13.8 \ (k-1)$$

(5)

Figure 3(b) shows that the  $I_{gmax}$  is proportional to 1/k, when the impurity concentration is scaled as  $kN_a$ . This means that the gate current is proportional to  $1/N_a$  and the sensitivity of the  $I_{gmax}$  against the scaled  $N_a$  ( $SN_a$ ) is predicted by equation 6.

$$\log\left(\frac{I_{\text{gmax}}(k)}{I_{\text{gmax}}(1)}\right) = S_{N_a} = -8.5 \left(\frac{1}{k} - 1\right)$$

(6)

Moreover, it is necessary to include the sensitivity of the  $I_g$  to the gate voltage shift ( $\Delta V_g$ ) from the  $I_{gmax}$  condition, to discuss the scaling of the gate swing between the high and the low states. Figure 3(c) shows the normalized  $I_g$ , when the swing of the gate voltage scaled by k ( $\Delta V_g/k$ ). The sensitivity of the  $I_g$  to the scaled  $\Delta V_g/k$  ( $S\Delta V_g$ ) is predicted from figure 3(c) as follows.

$$log\left(\frac{I_{g at}\Delta V_{g}(k)}{I_{g at}\Delta V_{g}(1)}\right) = S_{\Delta V_{g}} = -1.17\left(\frac{1}{k^{2}} - 1\right)$$

(7)

Fig. 4:  $I_{gmax}$  versus scaling of Vd,  $N_a$  and  $\Delta V_g$ .

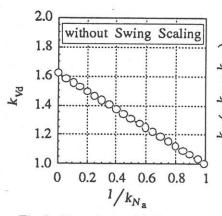

Fig 5: The relationship between  $kN_a$  and  $kV_d$  for keeping the programming current constant, when the gate swing is not scaled down.

# [ Scaling Scenario ]

In the view of the above considerations, the change of the maximum gate current can be predicted by the multiplied product of Vd,  $N_a$  and  $\Delta Vg$  sensitivities. Figure 4 shows the relation between scaling factor and the maximum gate current. Note that no scaling can keep the gate current and the programming ability constant. This is because, the sensitivity for the drain voltage is much higher than that for the others. Therefore, to keep gate current constant, the scaling for Vd should be optimized in combination with the other scaling factors.

From this point of view, the new scaling law to keep the gate current constant, is deduced by keeping the summation of sensitivity factors equal to zero as can be seen from equation 5 to 7. For example, when the drain voltage and the impurity concentrations are scaled except the swing voltage, the relation of equation 8 should be held.

$$S_{V_{d}} + S_{N_{a}} = -13.8 (k_{V_{d}} - 1) - 8.5 (\frac{1}{k_{N_{a}}} - 1) = 0$$

(8)

where kva and kNa are the scaling factors of the drain voltage (under PBC) and that of the impurity concentration. Figure 5 shows the relationship between the scaling factor for the impurity concentration (kNa) and that for the drain voltage (kva) from equation 8. kva is proportionally to 1/kNa and the least square fitted curve to the data intersect to the kva axis at 1.6 (1/kNa = 0, Na =infinity). This indicates that the drain voltage can not be reduced below 3.1V(=Valimit), even if the impurity concentration were infinity. Assuming the kva is approximated as the linear function of kNa, the drain voltage should be scaled as expressed by equation 9

$$V_{\rm d}(k) = V_{\rm d}(1) - \frac{V_{\rm d}(1) - V_{\rm d.limit}}{k}$$

(9)

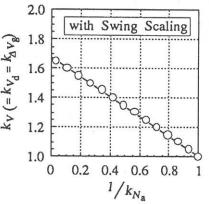

Fig 6: The relationship between  $kN_a$  and  $kV (=kV_d = kV_\Delta V_g)$  for keeping the programming current constant, when the gate swing is scaled down.

Table I: Summarize the new scaling law

| Gate Swing                              | kecping     | scaleing          |

|-----------------------------------------|-------------|-------------------|

| Impulity<br>Concentration               | k           | k                 |

| Supply Voltage at W                     | riting Mode |                   |

| V <sub>d</sub> - V <sub>d.limit</sub>   | 1/k         | 1/k               |

| V <sub>fg</sub> - V <sub>fg.limit</sub> | 1/k         | 1/k               |

| $\Delta V_{g} - \Delta V_{g,limit}$     | /           | 1/k               |

| Gate Current                            | 1           | 1                 |

| Programming Time                        | 1/k         | 1/k               |

| V <sub>d.limit</sub>                    | 3.1         | 3.0               |

| V <sub>fg.limit</sub>                   | 1.5 +1/2 Vf | $g.swing + V_{U}$ |

| $\Delta V_{g,limit}$                    | /           | 1.2               |

where k is the scaling factor, and the impurity concentration is  $k \cdot N_a$ . Moreover when the gate swing is scaled, the relationship between the scaling factor of the supply voltage (kv) and that of the impurity concentration is given by equation 10 and figure 6.

$$S_{V_{d}} + S_{N_{a}} + S_{\Delta V_{g}} = 0$$

(10)

In the same way as previously discussed, the limitation of the drain voltage and that of the gate swing are obtained to be 3.0V and 1.2V respectively. Hence the supply voltage can be reduced by  $(V - V_{\text{limit}}) / k$ , using the above limitation voltages.

The new scaling scenario is summarized in Table I. Comparing both of the scaling scenarios, it can be seen that scaling of the gate swing is less effective in reducing the limitation voltage. This is because the gate current hardly increases, when the  $V_g$  is varied near the maximum gate current region.

# [ Conclusion ]

The concept of Programming Best Condition (PBC) is used to discuss the effect of the scaling of  $V_d$ ,  $V_g$  and  $V_g$  swing on the programming time, in proportional to  $I_{gmax}$ . Under PBC, there exists the limitation voltage for scaling. Each supply voltage can be reduced by the scaled difference from each limitation voltage, to keep the programming current constant.

1) K.Yoshikawa, et al, VLSI Tech. Symposium, (1991), p.79 2) S.Tam, et al, IEEE Trans. Electron Devices, ED-31, (1984), p.1116

3) N.G.Einspruch, Advanced MOS Device Physics, Academic Press, San Diego, (1989), p.130