# Lateral Tunneling Devices on GaAs (111)A and (311)A Patterned Substrates Grown by MBE Using Only Silicon Dopant

#### H. Ohnishi, M. Hirai, K. Fujita and T. Watanabe

ATR Optical and Radio Communications Research Laboratories 2–2 Hikaridai, Seika–cho, Soraku–gun, Kyoto 619–02, Japan

A lateral interband tunneling transistor with gate-controlled negative differential resistance characteristics is demonstrated for the first time on a GaAs(111)A patterned substrate. Si-doped GaAs layers are grown on GaAs(111)A and GaAs(311)A patterned substrates by molecular beam epitaxy to fabricate lateral p-n junctions. Both samples show interband tunneling diode characteristics. Furthermore, a gate electrode is fabricated on the (111)A sample. The lateral tunneling transistor shows the modulated peak current density from 0.41 to 0.90 mA/cm<sup>2</sup> by varying the gate voltage from -5.0 to 5.0 V.

# **1. Introduction**

Tunneling devices with negative differential resistance (NDR) characteristics have attracted much interest because of their great potential for high-speed, low-power, and multifunctional device applications due to their unique current-voltage (I-V) characteristics. Tunneling diodes<sup>1,2)</sup> are already being used for high-frequency generation, frequency conversion and switching applications. Recently some reports have been made for three-terminal tunneling devices, that is tunneling transistors, with gate-controlled NDR characteristics<sup>3-6)</sup> because tunneling transistors have a number of potential applications. However, there are still some problems with the device fabrication processes; they require a complicated process to fabricate the gate electrode onto vertical tunneling junctions<sup>3-5)</sup> or require a regrowth process to obtain lateral tunneling junctions.<sup>6)</sup>

In this paper, we propose a new fabrication technology and device structure of a tunneling transistor based on lateral interband tunneling. To achieve lateral p-n tunneling junctions, plane-dependent Si doping in nonplanar epitaxy is used.<sup>7,8)</sup> This technique utilizes the amphoteric nature of Si dopant in molecular beam epitaxy (MBE). Since Si atoms incorporate as an acceptor in GaAs growth on (N11)A (N≤3) substrates,<sup>9)</sup> a lateral pn junction can be obtained by growing a Si-doped GaAs layer on a patterned (N11)A substrate. The fabrication process of the proposed tunneling transistor is as simple as that of conventional metal-insulator-semiconductor field effect transistors.

## 2. Experimental procedure

Patterned semi-insulating (111)A and (311)A oriented GaAs substrates were prepared using conventional photolithography and selective etching techniques. The sidewall orientations were controlled by varying the compositions of HF+H\_O\_+H\_O mixtures used as etching solution.<sup>10)</sup> A (511)A surface and (100) surface were used as the sidewall orientation for the (111)A substrate and (311)A substrate, respectively. After removing the photoresist, the substrates were degreased and etched with NH<sub>4</sub>OH:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O (2:1:96) for 1 min at 20°C.<sup>11)</sup> Then, they were introduced into the MBE chamber. After thermal cleaning at 630°C under an As, pressure, a undoped GaAs buffer layer and Si-doped (Si: 5x10<sup>19</sup> cm<sup>-3</sup>) GaAs layer were grown sequentially at 540°C. The As,/Ga flux ratio was 5 for the (111)A substrate and was changed to 2 for the (311)A substrate to obtain a p-type layer, because the conductivity type of Si-doped GaAs layers depends on the growth conditions such as the flux ratio.<sup>12)</sup> The growth rate was 0.6  $\mu$ m/hour and the substrates were rotated at 36 rpm to expose the entire flat surface and sidewall to the molecular beam during the growth of one monolayer.

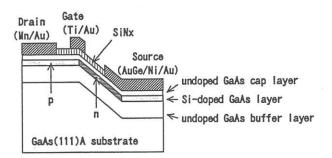

Photolithography and lift-off techniques were employed to fabricate a lateral transistor as proposed in Fig. 1. First, mesas were etched with  $H_3PO_4$ : $H_2O_2$ : $H_2O$  (3:1:50) solution to isolate the diodes. The p-type ohmic electrode (Mn/Au) and the n-type ohmic electrode (AuGe/Ni/Au) were evaporated on the flat surface and on the sidewall, respectively, and they were alloyed at 400°C for 2 min in

Fig. 1. Schematic cross sectional view of a lateral transistor.

$N_2$ . Secondly, a 50 nm thick SiNx film was deposited as the gate insulator. Then, a 5  $\mu$ m long and 200  $\mu$ m wide gate electrode (Ti/Au) was formed by deposition on the SiNx film at the p-n junction.

Cross sections of the lateral p-n junctions were observed by scanning electron microscopy (SEM). The carrier concentrations and conductivity types of the Sidoped GaAs layers were evaluated using samples grown on planar substrates by van der Pauw Hall measurements at room temperature (RT). The I-V characteristics of the devices were measured with the HP4142B and HP16276B at temperatures from 30 K to RT.

#### 3. Results and discussion

#### 3.1 Lateral tunneling diodes

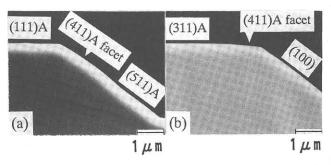

Figure 2 shows cross-sectional SEM micrographs of samples grown on (111)A and (311)A patterned substrates. An extra (411)A facet can be seen on the top of the sidewall for both samples. The conductivity type evaluated using Si-doped (Si:  $5x10^{19}$  cm<sup>-3</sup>) GaAs layers grown on planar (111)A and (311)A was p-type (p= $5x10^{19}$  cm<sup>-3</sup>) and that on (411)A was n-type (n= $9x10^{18}$  cm<sup>-3</sup>). These results indicate that the p-n junction is formed between the p-type top surface and the n-type (411)A facet.

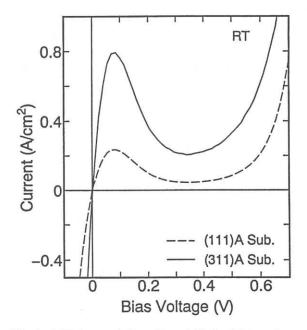

I-V characteristics at RT for lateral diodes on (111)A and (311)A patterned substrates are shown in Fig. 3. NDR characteristics can be seen for both samples in the forward bias region. For the (111)A diode, the peak-to-valley ratio (PVR) and the peak current density (I<sub>P</sub>) are 5.5 and 240 mA/cm<sup>2</sup>, respectively. These characteristics are comparable with the (311)A diode's with a PVR of 4.0 and an I<sub>P</sub> of 790 mA/cm<sup>2</sup>. In the reverse bias region, the I-V characteristics of these diodes were almost independent of the measurement temperature. This result indicates that the NDR characteristics are caused by the interband tunneling phenomenon. It should be noted that NDR characteristics were not observed in a patterned (111)A substrate with a

Fig. 2. Cross-sectional SEM micrographs of Si-doped GaAs layers grown on patterned substrates. (a) (111)A patterned substrate and (b) (311)A patterned substrate.

Fig. 3. I-V characteristics of lateral diodes fabricated on (111)A and (311)A patterned substrates.

(211)A or (311)A sidewall. In these samples, moreover, the (411)A facet was not observed on the top of the sidewall.<sup>13)</sup> These results indicate that the interband tunneling phenomenon results from an abrupt p-n junction between the top surface and the (411)A facet.

To increase the peak current density, a multiple quantum well (MQW) structure was grown on the patterned (111)A substrate. This AlGaAs/GaAs MQW structure consisted of five 8 nm thick Si-doped GaAs well layers sandwiched by 30 nm thick undoped  $Al_{0.2}Ga_{0.8}As$  barrier layers. In this case, the NDR characteristics were caused by the tunneling phenomenon between the p-type subband on the (111)A surface and the n-type subband on the sidewall. The peak current density was 350 mA/cm<sup>2</sup>; this value is 1.5 times larger than that of a 0.5  $\mu$ m thick GaAs lateral interband tunneling diode with the same Si doping concentration on a (111)A patterned substrate. This

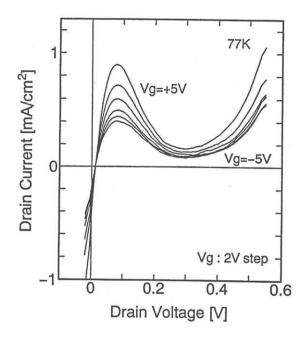

Fig. 4. I-V characteristics of a lateral transistor fabricated on a patterned GaAs(111)A substrate at 77 K.

improvement is attributed to an increase in the number of states per unit energy by vertical quantum confinement in QWs compared with a GaAs bulk structure. Furthermore, the peak current density will be increased by using MQW structures with a higher barrier height and a thinner well width.

## 3.2 Lateral tunneling transistors

To fabricate the lateral transistor as proposed in Fig. 1, the structure of the Si doped GaAs layer grown on the patterned (111)A substrate was as follows: a  $0.6 \,\mu\text{m}$  undoped GaAs buffer layer, a Si-doped (Si:  $1x10^{19} \text{ cm}^{-3}$ ) 50 nm thick GaAs layer and a 10 nm undoped GaAs cap layer. Figure 4 shows drain current (Id) – voltage (Vd) characteristics at 77 K. The Vd is swept from -0.02 to 0.55 V with the gate voltage (Vg) applied in steps of 2.0 V from -5.0 to 5.0 V. The NDR characteristics are controlled by Vg. The peak drain current density is modulated from 0.41 to 0.90 mA/cm<sup>2</sup>. On the other hand, the PVR of 5 is maintained in this gate bias region.

We have demonstrated that a lateral interband tunneling transistor can be achieved by using a Si-doped GaAs layer grown on a patterned (111)A substrate. This technique provides a simple process for fabricating three-terminal tunneling devices.

## 4. Conclusion

We have demonstrated lateral interband tunneling

diodes by using Si-doped GaAs layers grown on GaAs (111)A and (311)A patterned substrates. The interband tunneling phenomenon is observed between the p-type layer on the (111)A or (311)A surface and the n-type layer on the (411)A facet formed on the top of the sidewall. These diodes have NDR characteristics in the forward bias region at RT. Furthermore, we have demonstrated a lateral interband tunneling transistor on the patterned GaAs(111)A substrate. This transistor has gate-controlled NDR characteristics in the forward drain bias region. The peak drain current density is modulated from 0.41 to 0.90 mA/cm<sup>2</sup> by varying the gate voltage from -5.0 to 5.0 V. On the other hand, the PVR of 5 is maintained in this gate bias region.

## Acknowledgement

The authors would like to thank Dr. Hideyuki Inomata for his encouragement throughout this work.

## References

- 1) L. Esaki, Phys. Rev. 109 (1958) 603.

- 2) T. C. L. G. Sollner, W. D. Goodhue, P. E. Tannenwald, C. D. Parker and D. D. Peck, Appl. Phys. Lett. <u>43</u> (1983) 588.

- N. Yokoyama, K. Imamura, S. Muto, S. Hiyamizu and H. Nishi, Jpn. J. Appl. Phys. <u>24</u> (1985) L853.

- F. Capasso, S. Sen, A. C. Gossard, A. L. Hutchinson and J. H. English, IEEE Electron Device Lett. <u>EDL-7</u> (1986) 573.

- 5) K. Maezawa and T. Mizutani, Jpn. J. Appl. Phys. <u>32</u> (1993) L42.

- T. Uemura and T. Baba, Jpn. J. Appl. Phys. <u>33</u> (1994) L207.

- 7) D. L. Miller, Appl. Phys. Lett. 47 (1985) 1309.

M. Fujii, T. Yamamoto, M. Shigeta, T. Takebe, K. Kobayashi, S. Hiyamizu and I. Fujimoto, Surf. Sci. <u>267</u> (1992) 26.

- W. I. Wang, E. E. Mendez, T. S. Kuan and L. Esaki, Appl. Phys. Lett. <u>47</u> (1985) 826.

- T. Takebe, T. Yamamoto, M. Fujii and K. Kobayashi, J. Electrochem. Soc. <u>140</u> (1993) 1169.

- T. Yamamoto, M. Inai, T. Takebe and T. Watanabe, J. Vac. Sci. Technol. <u>A11</u> (1993) 631.

- M. Shigeta, Y. Okano, H. Seto, H. Katahama, S. Nishine and K. Kobayashi, J. Cryst. Growth <u>111</u> (1991) 284.

- T. Takebe, M. Fujii, T. Yamamoto, K. Fujita and K. Kobayashi, J. Cryst. Growth <u>127</u> (1993) 937.