# Characterization of One-Dimensional Conduction in an Ultra-Thin Poly-Si Wire

Tomoyuki Ishii, Kazuo Yano, Toshiaki Sano\*, Toshiyuki Mine, Fumio Murai, and Koichi Seki

Central Research Laboratory, Hitachi Ltd., Kokubunji 1-280, Tokyo 185, Japan \*Hitachi Device Engineering Ltd., Kokubunji, Tokyo 185, Japan

One-dimensional conduction in ultra-thin poly-Si single-electron devices is studied. A model, which includes a transition from one-dimensional conduction to two-dimensional conduction as gate voltage is increased, explains experimental results well. Unprecedented 60% modulation of current by random telegraph noise at room temperature has also been observed.

#### 1. Introduction

Single electron devices, in which an addition or subtraction of an electron can be controlled by using a charging effect, have recently attracted much attention [1]. We have succeeded in room temperature operation of single electron memories and transistors by introducing ultra-thin (~3-nm) poly-Si film in which natural onedimensional current path beyond lithography limit less than 10-nm is achieved [1, 2]. We believe that an ultrathin poly-Si film is one of the most promising platforms we have now to probe single-electron effects. In the previous works, however, study of the conduction in the films was limited to low electron density region because the gate oxide thickness was so large that the electrondensity cannot widely be changed. In this work, using new samples having thinner gate oxide we characterize the conduction in this ultra-thin poly-Si wire in wide electrondensity range. Especially, we study a transition from onedimensional conduction under near threshold voltage condition to two-dimensional conduction under higher gate voltage condition.

# 2. Device Structure

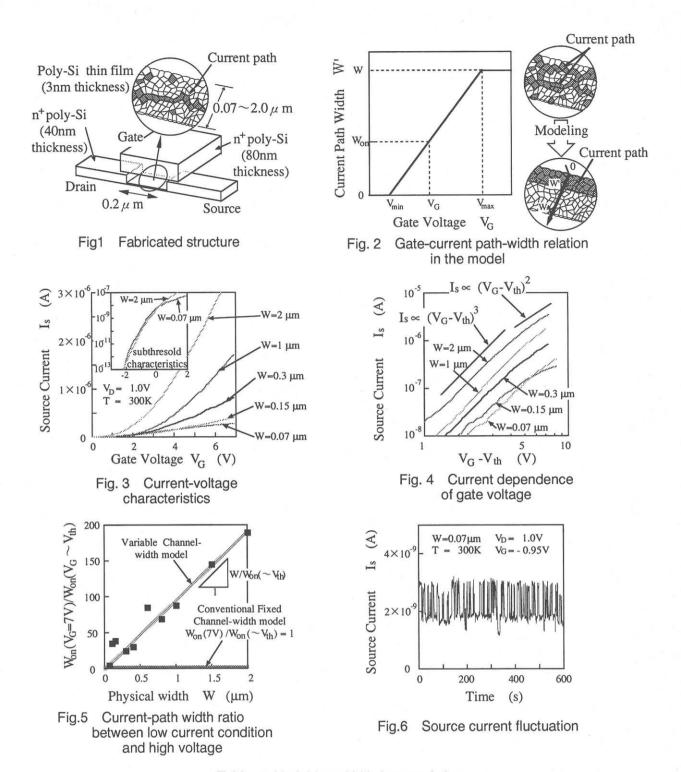

The fabricated device consists of an ultra-thin channel poly-silicon wire (3-nm thick) and a gate wire (80-nm thick) which covers the channel wire. Thickness of the gate oxide is 30-nm. The channel poly-silicon film is deposited as a-Si and crystallized at 750°C and consists of silicon grains, each about 10-nm across (Fig. 1).

In our picture, current path width under low current condition is comparable to the typical grain-size of the poly-Si film, and the width spreads as gate voltage is increased. Because there is thickness variation in the poly-Si film, the potential in the film, which originates mainly from vertical quantum confinement energy, varies randomly depending on the position. As we apply a positive gate bias, low-potential regions below the Fermi level are filled with electrons, and finally a percolation channel between source and drain is formed (Fig. 1). Then the current bottleneck of the channel is much narrower than physical wire width. The current-path width is expected to spread as gate voltage soars, because regions below the Fermi level increase.

# 3. Variable Channel-width Model

To take this width change effect into account, following simple model is formulated. We assume that a poly-Si wire consists of many fine wires that have different threshold voltages, which are scattered uniformly between  $V_{min}$  and  $V_{max}$  (Fig. 2). Here  $V_{min}$  is the lowest threshold voltage of fine wires in the film and  $V_{max}$  is the highest threshold voltage. Then, in this model effective current-path width  $W_{on}$  is given by following equation.

$$W_{on} = (V_G - V_{min}) W / \Delta$$

where V<sub>G</sub> is the gate voltage and  $\Delta$  is (V<sub>max</sub> -V<sub>min</sub>). Applying gradual channel approximation to each fine wire and integrating, we get equations shown in Table 1, which are compared with the conventional fixed channel width model. In saturation region, current-voltage characteristics are proportional to (V<sub>G</sub>-V<sub>th</sub>)<sup>3</sup> in this model, which is different from (V<sub>G</sub>-V<sub>th</sub>)<sup>2</sup> in conventional model. And in linear region, current depends on (V<sub>G</sub>-V<sub>th</sub>)<sup>2</sup>, which is higher power of (V<sub>G</sub>-V<sub>th</sub>) than linear dependence of conventional model. Under enough high gate voltage condition, which is higher than V<sub>max</sub>, current depends on (V<sub>G</sub>-V<sub>th</sub>) linearly because the current-path width corresponds to physical wire width and this model gives same results with conventional model in this region.

# 4. I-V Characteristics

Experimentally, the current-voltage characteristics of our devices show different behaviour from usual FET's characteristics. Channel width of sample changes from 0.07- $\mu$ m to 2- $\mu$ m. Each sample has same channel length, which is 0.2- $\mu$ m. I-V characteristics are shown in Fig. 3 and Fig. 4. Although the current increases exponentially as gate voltage is increased in subthreshold region just like usual FET (Fig. 3), in saturation region, the currentvoltage characteristics are not proportional to (V<sub>G</sub>-V<sub>th</sub>)<sup>2</sup> but are proportional to (V<sub>G</sub>-V<sub>th</sub>)<sup>3</sup>. And in linear region, the current depends on higher power of (V<sub>G</sub>-V<sub>th</sub>) than linear dependence. It is clear that our model describes much better the I-V curve of our devices than conventional model.

Using variable channel-width model, we can estimate current-path width from experimental I-V characteristics as following procedure. From equations shown in Fig. 1, second derivatives in saturation region and first derivatives in linear region are proportional to current width Won respectively. Then from the ratio between these two quantities, we can get the ratio between Won under highvoltage condition and Won under low-current condition if the mobilities under two conditions are not that different. Based on our model in which Won spreads proportionally to W as gate voltage increases, this ratio is proportional to W. On the other hand, this ratio is independent of W in fixed channel approximation. Evaluated ratios between Won at the high gate voltage and Won under the low gate voltage depend linearly on W, which agrees well with what our model predicts (Fig. 5). Assuming that the current-path width Won at VG=7V is close to W, we get current-path width near threshold about 10-nm, which is comparable to the typical lateral grain-size of the poly-Si film. Therefore, quasi-one-dimensional current path is formed in our ultra-thin poly-Si device under low current condition.

# 5. Random Telegraph Noise

One feature of one-dimensional conduction appears in large random telegraph noise. Time dependence of the drain current under fixed gate voltage and drain voltage at room temperature is shown in Fig. 6. Transitions between two states, which correspond to single electron capture and release, are clearly observed. This random telegraph noise with over 60 % current modulation is unprecedented large. In a one-dimensional path, repulsive Coulomb force works effectively and only one electron trap significantly affects the current. From this current modulation and I-V curve of this device, we can estimate capacitance between the gate and the bottleneck region in the current-path. And from this capacitance value, which is about 0.4-aF, the current-path width is estimated to less than 20-nm.

# 6. Conclusions

We have demonstrated that our model taking into account of gate-voltage dependence of current-path width explains experimental I-V characteristics of the single electron devices which use an ultra-thin poly-Si film well. Using this model, we show the current-path width of the device under the low current condition is about 10-nm, which is comparable to the typical lateral grain-size of the film. We also observed unprecedented large random telegraph noise at room temperature. This is a feature of one-dimensional conduction. These results support our picture for the device operational principles of our single electron memory and transistor.

# Acknowledgement

The authors would like to thank Dr. E. Takeda of the Hitachi Central Research Laboratory, Dr. H. Kawamoto of the Hitachi Semiconductor & Integrated Circuits Div., and Dr. K. Nakazato of the Hitachi Cambridge Laboratory for their support and valuable discussions. The authors are also indebted to Mr. T. Kure, Mr. T. Nishida, Dr. S. Ohkura, Mr. S. Iijima, Mr. T. Kobayashi of the Hitachi Central Research Laboratory, Mr. T. Morimoto, and Mr. T. Yamamoto of the Hitachi ULSI Engineering Ltd. for device fabrication.

# References

- For review, see for example, D. V. Averin and K. K. Likharev, in *Mesoscopic Phenomena in Solids*, Elsevier (1991); or H. Grabert and M. H. Devoret, eds., *Single-Charge Tunneling*, NATO ASI Series B (Plenum, New York, 1991).

- [2] K. Yano, T. Ishii, T. Hashimoto, T. Kobayashi, F. Murai, and K. Seki, IEEE Trans. Electron. Devices, Vol. 41, p1628-1638 (1994)

- [3] K. Yano, T. Ishii, T. Hashimoto, T. Kobayashi, F. Murai, and K. Seki, Int. Conf. on Solid State Devices and Materials, p325 (1994)

|                                              | saturation region<br>$(V_G < V_D + V_{th})$                     | linear region<br>$(V_G > V_D + V_{th})$                                                                                                        |

|----------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Variable<br>Channel-width<br>model           | $I_{\rm D} = \frac{\beta}{6\Delta} (V_{\rm G} - V_{\rm min})^3$ |                                                                                                                                                |

| Conventional Fixed<br>Channel-width<br>model |                                                                 | $I_{D} = \beta \{ (V_{G} - V_{th}) V_{D} - \frac{1}{2} V_{D}^{2} \}$ $\downarrow$ $\frac{1}{V_{D}} \frac{dI_{D}}{dV_{G}} = W \ \mu C_{OX} / L$ |

Table. 1 Variables of I-V characteristics