# Analysis of Si-Ge Source Structure in 0.15 μm SOI MOSFETs Using Two-Dimensional Device Simulation

Osamu ARISUMI, Kazuya MATSUZAWA, Naoyuki SHIGYO, Mamoru TERAUCHI, Akira NISHIYAMA, and Makoto YOSHIMI

ULSI Research Laboratories, R & D Center, Toshiba Corporation 1, Komukai Toshiba - cho, Saiwai - ku, Kawasaki, 210 Japan Phone: +81 - 44 - 549 - 2193 Fax: +81 - 44 - 549 - 2248

This paper describes the technological potential of the bandgap engineering technique using a Si-Ge source structure in SOI MOSFETs. The detailed mechanism as well as the structure dependence for suppression of the floating-body effect in 0.15  $\mu$ m gate-length SOI MOSFETs have been studied using a two-dimensional simulation. It has been found that the BVds improvement is strongly dependent on the lateral position of the Si-Ge layer to the source-to-channel p-n junction. It has also been predicted that the encroachment of the Si-Ge layer into the channel region is effective to achieve the maximum BVds improvement. The BVds improvement has been predicted to reach 1.5 V if it is possible to lower the energy barrier at the p-n junction in case where  $\Delta Eg = 0.2 \text{ eV}$ .

## **1. INTRODUCTION**

Silicon-on-insulator (SOI) devices are expected to offer great potential for realizing low-power and highspeed ULSIs, which are essential for portable, multimedia computer systems. In applying SOI devices to practical ULSIs, however, the critical drawback is the floating-body effect, which causes a lowering of the drain-to-source breakdown voltage (BVds) [1], the appearance of kinks in the Id-Vds characteristic [2], anomalous subthreshold swings, and Vth shifts [3]. To suppress these effects, we have proposed and experimentally demonstrated the bandgap engineering technique, in which a narrow bandgap material,  $Si_{l,r}Ge_r$ , is formed using Ge implantation in the source region [4][5]. The aim of this technique is to remove the excess holes in the channel region by forming a heterojunction near the source / channel interface.

In this work, we investigate the technological potential of the bandgap engineering technique of using the Si-Ge source structure. The detailed mechanism as well as the structure dependence of BVds improvement in 0.15  $\mu$ m gate-length SOI MOSFETs is studied using a two-dimensional simulation. It has been found that the BVds improvement is strongly dependent on the lateral position of the Si-Ge layer. It has also been clarified that bandgap engineering in the proximity of the source-to-channel p-n junction is important to realize the maximum performance.

### 2. SIMULATION

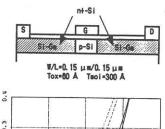

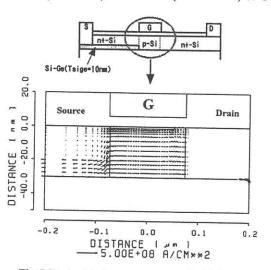

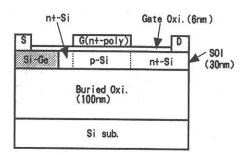

Figure 1 shows a cross section of the n-type thinfilm SOI MOSFET used in this analysis. Here, n<sup>+</sup>-regions and the channel region were approximated to have rectangular shape. The Si-Ge region was also assumed to be rectangular. The Ge ratio x in the  $Si_{1x}Ge_x$  was in most cases equal to 0.1, which was shown to correspond to a bandgap narrowing of approximately 0.1 eV [1], except in cases where the bandgap narrowing dependence of BVds improvement was investigated. In ignoring the effect of the Si-Ge layer on impact ionization near the drain region, the Si-Ge layer is only formed on the source region. The device structure was optimized in terms of the short channel effect at 0.15  $\mu$ m gate length : W / L = 0.15  $\mu$ m / 0.15  $\mu$ m ; T<sub>SOI</sub> = 30 nm; the impurity concentration in the channel region and that in the source / drain  $n^+$ -region was  $8 \times 17$  cm<sup>-3</sup> and  $1 \times 20$  cm<sup>-3</sup>, respectively. Under these conditions, the SOI MOSFETs were of the fully-depleted type. A twodimensional device simulator (MOS2C), in which physical parameters such as bandgap, mobility, impact-ionization rate, etc., were modified to deal with the Si-Ge structure, was used.

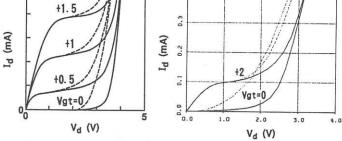

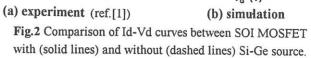

Figure 2 shows a comparison of Id-Vds curves for SOI MOSFETs with and without a Si-Ge source. Here, a Si-Ge layer was formed on the source and drain regions to enable comparison of Id-Vds characteristics between experiment and simulation. It can be seen that the drain breakdown voltage improvement ( $\Delta$ BVds) by using a Si-Ge

structure is reproduced. Hereinafter,  $\Delta BVds$  is defined at Id = 0.1 mA, Vgt = 0 V (Vgt = Vg - Vth). In the simulated structure shown in Fig. 2 (b),  $\Delta BVds$  was 0.9 V, which was close to the value obtained in the experiment.

## **3. RESULTS and DISCUSSION**

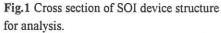

It has been found that the BVds improvement tends to saturate as the Ge content ratio x is increased, as shown in Fig. 3. This is attributed to a tendency of hole flow to saturate with bandgap narrowing, i.e., the hole current enhancement becomes smaller as the valence band shift becomes larger. This is because the energy barrier for holes at the p-n junction tends to limit hole current for a valence band shift larger than 0.2 eV. Nevertheless, it should be noted that a Ge ratio as small as 0.1 can realize an approximately 1 V improvement in BVds.

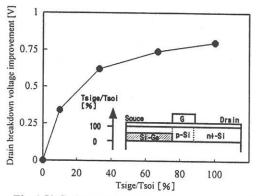

Figure 4 shows that as the Si-Ge layer thickness increases,  $\Delta$ BVds also increases. This can be explained by an increase in hole-current "conductance" as the Si-Ge layer is made thicker. However, it can be seen that even a 10 nm Si-Ge layer (T<sub>SiGe</sub> / T<sub>SOI</sub> = 33 %) realizes approximately 80 % of  $\Delta$ BVds which is achieved by a 30 nm-thick Si-Ge layer. In Fig. 4, the Si-Ge layer thickness is increased from the buried-oxide side to the gate-oxide side. Still, the same tendency has been obtained for the case of increasing the Si-Ge layer thickness to the contrary. Figure 5 demonstrates how holes are absorbed by the Si-Ge layer which is partially formed in the source region.

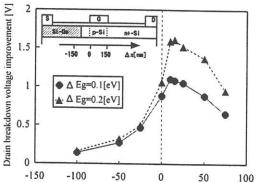

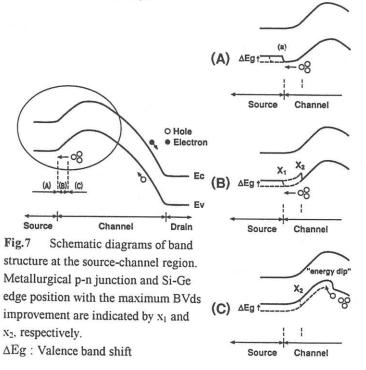

The lateral spacing between the Si-Ge layer edge and the metallurgical p-n junction, x, influences  $\Delta BVds$ significantly, as shown in Fig. 6. As the edge of Si-Ge layer approaches the p-n junction ( $\Delta x < 0$  nm),  $\Delta BVds$ increases abruptly. It should be noted that, as the Si-Ge edge further moves into the channel region (0 nm  $\leq \Delta x$ ),  $\Delta$ BVds continues to increase and reaches a maximum (at  $\Delta$ x = 10 nm for 0.1 Ge content ). When the Si-Ge edge further encroaches into the channel region, ABVds begins to decrease ( $\Delta x > 10$  nm). These phenomena are explained in Fig. 7, where three cases of lateral position for the Si-Ge layer are shown, i.e., (A)  $\Delta x < x_1 (= 0 \text{ nm})$ , (B)  $0 \le \Delta x \le x_2$ ( $\approx$  10 nm), and (C)  $\Delta x > x_2$ . In case (A), the hole current increases as the Si-Ge edge approaches the p-n junction. Here, the Si-Ge layer is considered to increase the holecurrent conductance from the channel to source regions because the intrinsic carrier density in Si-Ge ( nie ) is greater than that in Si (  $n_i$  ) as follows.

## $n_{ie}^2 = n_i^2 \exp(\Delta Eg / kT)$

Here,  $\Delta Eg$  is the amount of the valence band shift. As the

Si-Ge layer approaches the channel region, the efficiency of excess hole absorption increases, resulting in a BVds increase. In case (B), the hole current increases because the energy barrier height for the hole-current is significantly reduced. In case (C), holes come to accumulate in an "energy dip", and the hole-current decreases because the energy barrier for holes rises again at the p-n junction boundary. It should be added in Fig.6 that the  $\Delta$ Eg dependence of  $\Delta$ BVds in the case where the Si-Ge layer is inside the channel region is much larger than the case where the Si-Ge layer is in the source region.

These results indicate that it is possible to realize the greater potential of the bandgap engineering method if the Si-Ge layer can be placed in the channel region.

#### 4. CONCLUSIONS

We have analyzed the mechanism and structure dependence of the bandgap engineering technique using a Si-Ge source structure in thin-film 0.15  $\mu$ m SOI MOSFETs. The simulation revealed that using the Si-Ge formation which is self-aligned to the gate, ex. Ge implantation, an approximately 1 V improvement in BVds for 0.15  $\mu$ m SOI MOSFETs can be expected at maximum for  $\Delta Eg = 0.2$  eV. Furthermore, it was confirmed that BVds improvement can be further increased to 1.5 V if it is possible to reduce the energy barrier at the p-n junction by making the Si-Ge layer to encroach into the channel region.

## ACKNOWLEDGMENT

The authors would like to thank Mr.Y.Ushiku and Dr.T.Arikado at the ULSI Research Labs. of Toshiba Corp. for their valuable discussions and encouragement.

## REFERENCES

- [1] M.Yoshimi et al., IEEE, vol.ED-37, no.9, 1990, p.2015

- [2] K.Kato et al., IEEE, vol.ED-32, no.2, 1985, p.458

- [3] L.T.Su et al., Technical Digest of IEDM '94, San Francisco, 1994, p.649

[4] M.Yoshimi et al., Technical Digest of IEDM '94, San Francisco, 1994, p.429

[5] M.Terauchi et al., Technical Digest of Symposium on

VLSI Technology, Kyoto, 1995, p.35

Fig.3 Valence band shift versus drain breakdown voltage improvement.

Fig.4 Si-Ge layer thickness versus drain breakdown voltage improvement.