## Modeling on the Channel-To-S/D Capacitance and the Short Channel Effect for 0.1μm Fully Depleted SOI-MOSFET

Risho Koh, Haruo Kato\* and Hiroshi Matsumoto

Microelectronics Res. Labs., ULSI Device Development Labs.\* NEC Corp. 1120, Shimokuzawa, Sagamihara, Kanagawa 229, Japan

This paper proposes a simple analytical model on the short channel effect for the fully depleted SOI-MOSFET. The influence of the two dimensional effect is included based on the spatial distribution for the channel-to-S/D (source and drain ) capacitance 1)2) which is determined by an empirical expression. This treatment makes it possible to estimate the two dimensional effect without solving Poisson's equation which requires a large computation time. This model describes the short channel effect down to  $0.1\mu m$  regime.

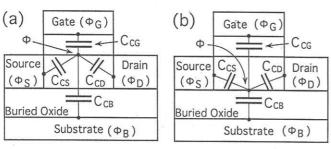

FIg.1 The capacitance net work model. (a) is for the surface conduction,(b) is for the back interface conduction

1.Model Consider a capacitance network, which determines the potential for the fully depleted SOI-MOSFET, as shown in Fig.1. We propose empirical expressions which represent channel-to-source capacitance  $C_{CS}$ , channel-to-drain capacitance  $C_{CD}$ , as in Eqs. 1 and 2.

$$C_{CS}(x) = \frac{\alpha' (T_{SOI} + \beta')}{x^2 + \gamma' x} \quad \varepsilon_0 \, \varepsilon_{OX} \quad (1)$$

$$C_{CS}(x) = \frac{\alpha' (T_{SOI} + \beta')}{x^2 + \gamma' x} \quad \varepsilon_0 \varepsilon_{OX} \quad (1)$$

$$C_{CD}(x) = \frac{\alpha' (T_{SOI} + \beta')}{(L - x)^2 + \gamma' (L - x)} \quad \varepsilon_0 \varepsilon_{OX} \quad (2)$$

Where,  $T_{SOI}$  is the SOI thickness, x is the horizontal position (x = 0 for the source junction), L is the gate length,  $\alpha'$ ,  $\beta'$  and  $\gamma'$  are fitting parameters whose values are 2.29, 70A and 50A, respectively.  $\beta'$  is a parameter which is introduced in order to include the influence of the electric field from the buried oxide. In Eqs.1 and 2, the dependence on the bias voltage and on the vertical position are neglected, since these dependencies are found to be small from device

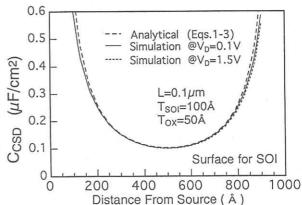

$C_{\text{CSD}}$  is determined as the sum of  $C_{\text{CS}}$  and  $C_{\text{CD}}$  as in

$$C_{\text{CSD}}(x) = C_{\text{CS}}(x) + C_{\text{CD}}(x)$$

(3)

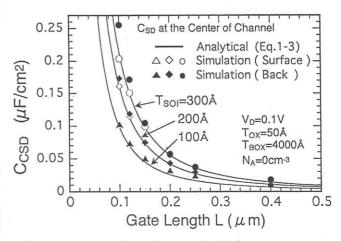

The horizontal distribution for  $C_{CSD}$  (Fig.2) and the dependence of  $C_{CSD}$  on the device structure (Fig.3) show excellent agreement with the numerical simulation results.

Fig.2 The horizontal distribution for C<sub>CSD</sub> (the sum of Ccs and CcD ). Broken line shows the result given by Eqs.1-3. Solid line and dotted line show the simulation results.

Fig.3 The C<sub>CSD</sub> dependence on the device structure.

The potential in the SOI layer  $\phi$ , threshold voltage  $V_{th}$ and subthreshold swing S are derived using  $C_{CS}$  and  $C_{\rm CD}$  as follows.  $\phi$  is given by Eq.4 by considering the capacitance network (Fig.1a and b),

$$\phi = \frac{C_{\text{CG}} \phi_{\text{G}} + C_{\text{CS}}(x) \phi_{\text{S}} + C_{\text{CD}}(x) \phi_{\text{D}} + C_{\text{CB}} \phi_{\text{B}}}{C_{\text{CG}} + C_{\text{CS}}(x) + C_{\text{CD}}(x) + C_{\text{CB}}}$$

(4)

where,  $\phi_S$  is the source potential,  $\phi_D$  is the drain potential,  $\phi_G$  is the gate potential and  $\phi_B$  is the substrate potential.

$C_{\text{CG}}$  is the channel-to-gate capacitance, which is given by Eqs.5 and 6.

$$C_{\text{CG}} = \varepsilon_0 \varepsilon_{\text{OX}} / T_{\text{CG}}$$

$$T_{\text{CG}} = T_{\text{OX}} + y \varepsilon_{\text{OX}} / \varepsilon_{\text{Si}}$$

(5)

Where,  $T_{\rm OX}$  is the gate oxide thickness and y is the depth from SOI surface. In the following discussions, y corresponds to the distance between the SOI surface and the position where the subthreshold current flows.  $C_{\rm CG}$  is assumed to be independent of horizontal position.

C<sub>CB</sub> is the channel-to-substrate capacitance, and this capacitance is neglected in the following discussion since its value is small for the SOI-MOSFET.

Since  $V_{th}$  is the gate voltage which provides the inversion potential  $\phi_{inv}$  in the SOI layer,  $V_{th}$  is derived from Eq.4 as in Eq.7 for the intrinsic SOI layer.

$$V_{\text{th}} = \frac{(C_{\text{CG}} + C_{\text{CS}}' + C_{\text{CD}}') \phi_{\text{inv}} - C_{\text{CS}}' \phi_{\text{S}} - C_{\text{CD}}' \phi_{\text{D}}}{C_{\text{CG}}} + \Phi_{\text{ms}}$$

(7)

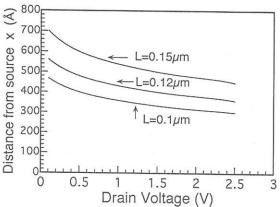

Where,  $C_{\rm CS}'$  and  $C_{\rm CD}'$  represent  $C_{\rm CS}$  and  $C_{\rm CD}$  at the position where the potential is the minimum along the channel (potential barrier position).  $C_{\rm CS}'$  and  $C_{\rm CD}'$  are determined by substituting the potential barrier position , which is calculated using Eq.4 as shown in Fig.4, into x in Eqs.1 and 2.  $\Phi_{\rm ms}$  is the difference of the work function between the gate electrode and the source electrode.

The subthreshold swing S is given by replacing  $C_{CB}$  for the usual definition of the S factor(Eq.8), by the sum of  $C_{CS}$ ' and  $C_{CD}$ ' as Eq.9, since  $C_{CB}$  is small, and  $C_{CS}$ ' and  $C_{CD}$ ' are important for the short channel fully depleted SOI-MOSFET.

$$S = (kT/q) \ln(10) (1 + C_{CB}/C_{CG})$$

$$S = (kT/q) \ln(10) (1 + (C_{CS}' + C_{CD}') / C_{CG})$$

(8)

(9)

**Fig.4** The horizontal position of the potential barrier which is calculated using Eq.4

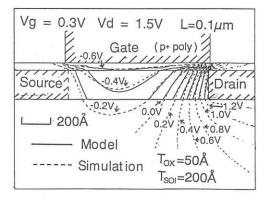

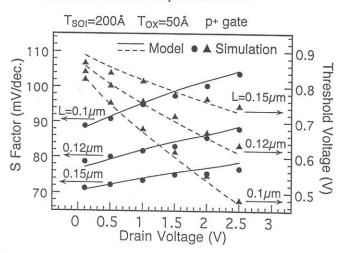

**2.Result** The two dimensional potential distribution given by Eq.4 is shown in Fig.5. The S factor given by Eq.9 and  $V_{th}$  given by Eq.7 are shown in Fig.6. Their agreement with the numerical simulation indicates that the above model is valid to deal with the short channel

effect for the fully depleted SOI-MOSFET.

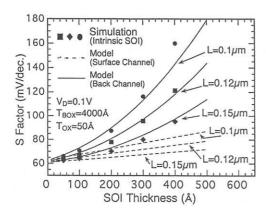

For the low drain voltage, where the potential barrier is located near the center of the channel, S can be reduced to a very simple form as shown in Eq. 10.

$$S = (kT/q)\ln(10)(1 + \frac{\alpha T_{\text{CG}}(T_{\text{SOI}} + \beta)}{L^2 + \gamma L})$$

(10)

$$T_{\text{CG}} = T_{\text{OX}} + d T_{\text{SOI}} \ \varepsilon_{\text{OX}} / \varepsilon_{\text{Si}}$$

(11)

where,  $\alpha$ ,  $\beta$  and  $\gamma$  are fitting parameters, whose value are 18.3, 70A and 100A, respectively.  $T_{CG}$  is the effective gate oxide thickness, which is given by Eq.11. where, d is a parameter for the back channel, whose value is zero for the surface channel, and unity for the back channel.

Equation 10 can provide a convenient way to estimate the S factor dependence on the device structure, as shown in Fig.7. Simulation results for intrinsic SOI body is inserted in Fig.7. The simulation results agree with the S factor for the back channel conduction.

**Fig.5** The potential distribution given by Eq.4. The depletion layer at the drain junction is determined as 20Å, and it is added for the gate length to correct the potential profile near drain. However this correction is neglected in the following discussion, since its influence is small for the potential barrier.

**Fig.6** The dependence of S factor and  $V_{th}$  on the drain Voltage for L=0.1  $\mu$  m,0.12  $\mu$  m and 0.15  $\mu$  m. The floating body effect is neglected in the device simulation to distinguish the short channel effect.

**Fig.7** S factor dependence on the device structure for the SOI-MOSFET, which is given by Eq.10. The solid lines show the result for the back interface conduction, and broken lines for the surface conduction. Simulation is done for the intrinsic SOI.

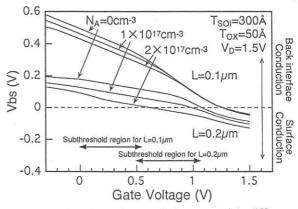

3.Discussion on the back channel influence Equations 7.9 and 10 indicate that the short channel effect depends not only on Ccs and CcD discussed above, but also on the depth of the channel in the SOI layer which determines  $T_{CG}$  and  $C_{CG}$ . Therefore, the condition for the back channel formation is investigated using device simulation. The potential difference between SOI back interface and surface ( $V_{bs}$ ) is shown in Fig.8 for L=0.1  $\mu$  m and 0.2  $\mu$  m, where the positive value represent the case where the potential of back interface is larger than the surface. The increase in the back interface potential is caused by the electric field from the source and the drain. When V<sub>bs</sub> is positive, the subthreshold current flows at the back interface where the gate controllability is worse, and the short channel effect is enhanced (TCG increases in Eqs.5 and 10, C<sub>CG</sub> decreases in Eqs.7-9).

For  $L=0.2 \mu \text{ m}$ ,  $V_{\text{bs}}$  becomes negative for higher accepter concentration at the subthreshold region, since the electric field from acceptor ions lower the back interface potential. However, it can not be negative for  $L=0.1 \mu$  m. One reason is that the channel-to-S/D capacitance increases drastically by reducing the gate length from  $0.2 \mu$  m to  $0.1 \mu$  m, as shown in Fig.3. This leads to a increase in  $V_{bs}$ . Another reason is that the static electrical coupling between the acceptor ions and the S/D electrode increases, and consequently the coupling between the acceptor ions and the gate electrode decreases, as the gate length decreases. This effect prevents the back interface from being lowered by the electric field from acceptor ions, then the  $V_{\rm bs}$ dependence on the acceptor concentration becomes smaller for  $L=0.1 \mu$  m than for  $L=0.2 \mu$  m, as shown in Fig.8. The back channel formation can be discriminated by Eq.12, where  $V_{\rm bs}$  is calculated from Eq.4 and  $\xi$  is a parameter less than unity that increases as the gate length decreases.

$$V_{\rm bs} > (1-\zeta) qN_{\rm A} T_{\rm SOI}^2 / 2 \varepsilon_{\rm OX} \varepsilon_0 \tag{12}$$

Fig.8 The dependence of the potential difference between the SOI back interface and the surface on the acceptor concentration. Positive value indicates that the back interface potential is larger than surface, and that the subthreshold current flows at the back interface.

**4.Device design for 0.1\,\mu m SOI-MOSFET** The above result indicates that a drastic increase in  $C_{\rm CSD}$  (Fig.3) enhances the short channel effect for  $0.1\,\mu$  m SOI-MOSFET (Fig.7), and that the ultra thin SOI layer ( < 200A) is efficient to eliminate this effect by compensating the increase in  $C_{\rm CSD}$  (Fig.7 and Eqs.1-3), and by increasing the gate-to-channel capacitance when the back channel is formed (Fig.7 and Eqs.7,9,10), for the fully depleted SOI-MOSFET.

**5.Conclusion** It is shown that the  $V_{th}$  shift and the degradation of S factor due to the two dimensional effect, can be derived from a simple analytical model using empirical channel-to-S/D capacitance for the fully depleted SOI-MOSFET. This method does not require to solve the Poisson's equation. A simple formula that provides the S factor dependence on the gate length, SOI thickness and the gate oxide thickness for low drain bias, is also obtained based on the model. Device design for  $0.1\,\mu$  m SOI-MOSFET is discussed based on the above model. This model is valid for describing the short channel effect down to  $0.1\mu$ m regime, where the two dimensional effect is significant even for the fully depleted SOI-MOSFET.

## References

- Koh.et.al Ext. Abs. 1994 SSDM (1994.Aug.), p.295

- 2) Koh.et.al IEICE Tech. Rep. SDM94-207 (1995.Mar.), p.17, in Japanese.