# **Oxidation of Amorphous Silicon for Superior Thin Film Transistors (OASIS TFT)**

Mitsutoshi MIYASAKA, Tadakazu KOMATSU\* and Hiroyuki OHSHIMA

SEIKO EPSON CORPORATION Base Technology Research Center / \*Analysis Center Owa 3-3-5, Suwa, Nagano, 392 JAPAN TEL: 81(Japan)-266-52-3131 FAX: 81(Japan)-266-52-7409

The conditions under which silicon film is deposited by low pressure chemical vapour deposition change crystalline nucleation rate of the deposited film during thermal oxidation, resulting in crystallized silicon films having different grain sizes. Therefore, we can improve the electric properties of poly-crystalline silicon thin film transistors merely by controlling the deposition process.

## 1. Introduction

Poly-crystalline silicon (Polysilicon) thin film transistors (TFTs) are interesting devices, not only because they are used to form simple integrated circuits, such as static shift registers, but also because they have enormous potential for use in forming more complicated circuits. If the electric characteristics of the devices are much higher than those of currently popular polysilicon TFTs, TFTs will certainly be able to expand their position in the microelectronics industry, competing with silicon-on-insulator (SOI) devices. A lot of effort has, therefore, been expended to improve the properties of polysilicon TFTs<sup>1)-4</sup>, though nearly all attempts at improvement have made the fabrication process long and difficult. This paper will examine the silicon film formation process so as to lead to a simple and easy way of fabricating high performance polysilicon TFTs.

## 2. Experiment

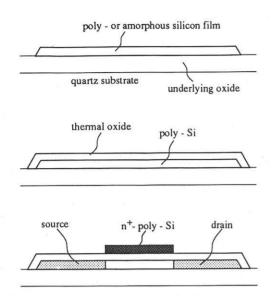

Polysilicon TFTs are fabricated entirely through a standard high temperature process with the exception of the silicon film deposition (Fig. 1). Various kinds of silicon films have been deposited by low pressure chemical vapour deposition (LPCVD), mainly by changing the temperature and the pressure. Mono-silane (SiH<sub>4</sub>) is used as a reactant gas for all the experiments, so the poly-crystalline films are deposited below 570° C. The transition from amorphous to poly-crystalline in the as-deposited state is observed at 575° C. The as-deposited amorphous and poly-crystalline films are, then, furnace-annealed under oxygen ambient at 1160° C to make the polysilicon semiconductor layer and gate oxide

layer. No process to improve crystallinity of the silicon film is required prior to this oxidation. After the gate electrode is formed with n<sup>+</sup> polysilicon film, ion implantation and subsequent activation annealing at 1000°C complete a selfaligned polysilicon TFT.

Film properties have been examined by some physical analyses, such as scanning electron microscopy (SEM) and atomic force microscopy (AFM).

## 3. Results

Figure 2 shows the mobility dependence on the silicon film deposition temperature. The mobility value generally increases as the deposition temperature decreases in the temperature range of over 500°C. This phenomenon is explained by the fact that the grains of the polysilicon film, which serves as an active layer of the transistor, enlarge in size as the temperature is lowered. Figures 3a and 3b are SEM photographs of the polysilicon films obtained after the thermal oxidation of as-deposited films which are originally deposited at 650°C and 525°C, respectively. Polysilicon films obtained by the thermal oxidation of amorphous silicon films (Fig. 3b) include larger grains than do the films obtained by the thermal oxidation of polysilicon films (Fig. 3a). This is quite consistent with theory<sup>5)</sup> and previous work<sup>6</sup>) that the grain size has a close positive relation to the mobility value.

#### 4. Discussion

The process of crystallization is a competition between crystalline growth and nucleation. As a result, the relative magnitude of crystalline growth rate to crystalline nucleation rate determines the average grain size of the polysilicon film<sup>7),8)</sup>. Since the crystallization temperature, i.e. the temperature of the thermal oxidation, is fixed throughout the experiment, the crystalline growth rate is the same for all the samples. The different grain sizes observed in the SEM photographs are, therefore, attributable to the different crystalline nucleation rates. The crystalline nucleation rate in the as-deposited films decreases as the deposition temperature is lowered from 650° C to 500° C.

Regardless of what kind of silicon film it is, the initial stage of the silicon deposition in LPCVD consists of nucleation on the substrate surface and nucleus growth for film formation<sup>9)</sup>. (To distinguish from crystalline nucleation and crystalline growth we call these film nucleation and film growth, respectively.) The film nucleation and film growth compete with one another until the whole surface area is covered with silicon film. If the film nucleation rate is relatively fast compared to the film growth rate, the silicon film is composed of many small regions. Conversely if the film growth rate is relatively fast compared to the film nucleation rate, the silicon film is composed of a few large regions. These regions are normally called grains when the as-deposited silicon film is in the poly-crystalline state. AFM photographs of figures 4a and 4b reveal that as-deposited amorphous silicon films are also composed of these regions and that decreasing deposition temperature reduces the relative magnitude of film nucleation rate to film growth rate to increase the size of the regions.

It is deduced that amorphous films that are composed of large regions can be converted to poly-crystalline films that are composed of large grains. In other words, the size of regions in an as-deposited amorphous film is in proportion to the size of crystalline grains in the thermally-oxidized poly-crystalline film; that is, crystalline nucleation rate in an amorphous film has a strong correlation with the film nucleation of the amorphous film. Changing the deposition conditions leads to the different size of the regions of asdeposited film. This results in the different sizes of the polysilicon grains after thermal oxidation and, therefore, alters the mobility value of the corresponding TFTs.

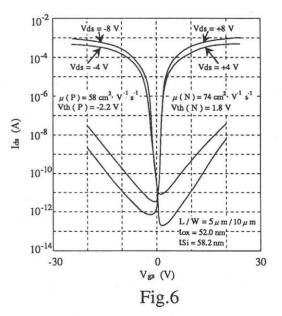

The deposition temperature is not the only factor that controls film nucleation rate and film growth rate; these are controlled by the deposition pressure as well. Increasing the deposition pressure mainly speeds up the film growth rate so that the high pressure deposition of amorphous silicon film has a positive effect on the polysilicon TFT (Fig. 5). Because this process utilizes the direct oxidation of amorphous <u>si</u>licon for obtaining a <u>superior TFT</u>, we have named it OASIS TFT. Figure 6 shows the transfer characteristics of OASIS TFTs which are fabricated under the maximum temperature (thermal oxidation) of 1000°C. Superior TFTs are easily fabricated merely by controlling the deposition conditions.

## 5. Conclusion

The silicon film deposition conditions in LPCVD obviously influence the crystalline nucleation rate in the asdeposited film during thermal oxidation by changing the film nucleation rate and film growth rate, thereby enabling an increase in the mobility value of the polysilicon TFTs. Low temperature and high pressure deposition of amorphous silicon is found to be preferable for obtaining high quality polysilicon film. Since the OASIS TFT, which shows good electric characteristics, utilizes this mechanism, it is fabricated through a simple and easy, standard high temperature process. No extra process to improve the polysilicon film quality is required; all that is required is the precise control of the nucleation rate and the growth rate of silicon film that is deposited on the substrate in a LPCVD reactor.

### Acknowledgments

The authors gratefully acknowledge Mr. W. Miyazawa and all members of the pilot line for TFT fabrication. The authors also appreciate Mr. W. Itoh for his excellent physical analysis, as well as Mrs. M. Uehara for her help in preparing the manuscript.

1) T. Ohshima, T. Noguchi and H. Hayashi: Jpn. J. Appl. Phys. 25 (1986) L291.

2) T. Noguchi, H. Hayashi and T. Ohshima: J. Electrochem. Soc. 134 (1987) 1771.

3) S. Takenaka, M. Kunii, H. Oka and H. Kurihara: Jpn. J. Appl. Phys. 29 (1990) L2380.

4) Y. Fukushima, T. Ueda and H. Komiya: Ext. Abstr. 1993 Int. Conf. Solid State Devices and Materials (Business Center for Academic Societies Japan, Tokyo, 1993) p. 993.

5) J. Y. W. Seto: J. Appl. Phys. 46 (1975) 5247.

6) M. Miyasaka, T. Komatsu, W. Itoh, A. Yamaguchi and H. Ohshima: Jpn. J. Appl. Phys. 35 (1996) 923.

7) R. B. Iverson and R. Reif: J. Appl. Phys. 62 (1987) 1675

8) M. K. Hatalis and D. W. Greve: J. Appl. Phys. 63 (1988) 2260.

9) M. Miyasaka, W. Itoh, T. Komatsu, I. Yudasaka and H. Ohshima: Jpn. J. Appl. Phys. 33 (1994) 444.

Fig.1

Fig.3a 100nm Tdepo = 650 °C

Fig.4a Tdepo = 570℃

# Fig.4b Tdepo = 510℃