# Low Contact Resistance Poly-Metal Gate CMOS Using TiN/Thin TiSi<sub>2</sub>/Poly-Si Structure

## Fumio Ohtake and Yasuo Nara Fujitsu Laboratories Ltd.,10-1 Morinosato-Wakamiya Atsugi ,243-0197 Japan Phone:+81-462-50-8238, Fax:+81-462-48-3473, E-mail:ohtake@han.flab.fujitsu.co.jp

### 1. Introduction

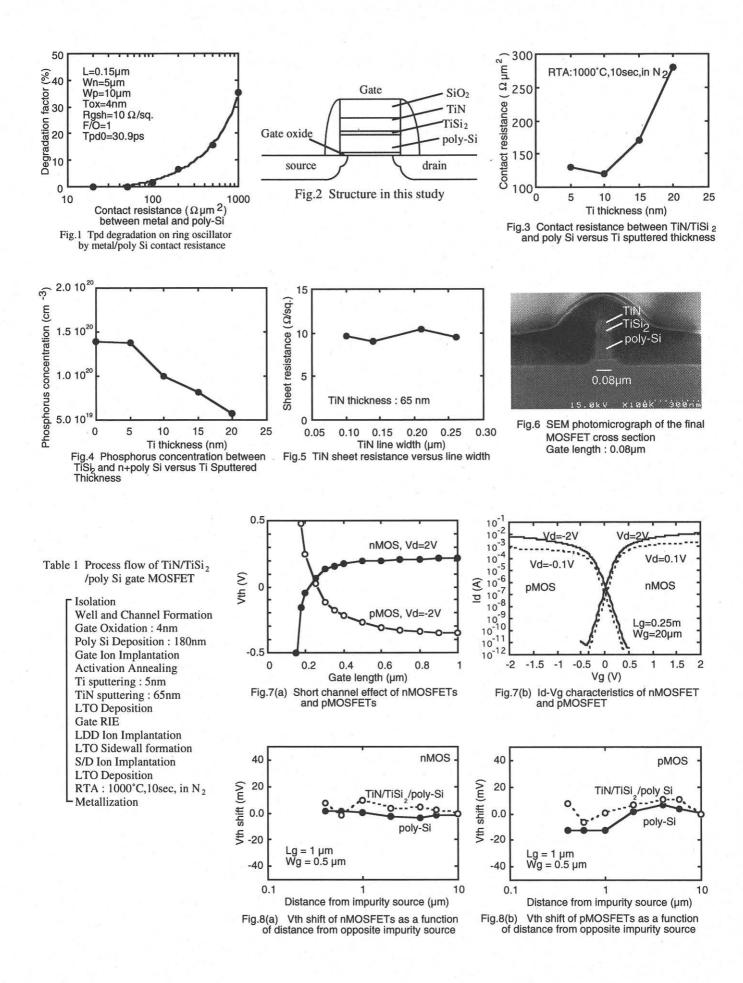

For deep submicrometer MOSFETs with low gate sheet resistance and high heat resistance, poly-metal gate electrode structures, such as W/WN/poly-Si[1],W/TiN/poly-Si[2] and TiN/poly-Si[3] have been demonstrated. Contact resistance between metal and poly-Si is a key issue in these poly-metal gate structures. It is known that gaining the ohmic contact between TiN and silicon is especially difficult[4]. This high contact resistance causes a degradation of the MOSFETs' performance[5]. From simulations of CMOS ring oscillators, a contact resistance of less than 300  $\Omega\mu$ m<sup>2</sup> is necessary to suppress a delay time degradation of less than 10 % as shown in Fig.1.

In this paper, we propose a low contact resistance polymetal gate structure by inserting a thin TiSi<sub>2</sub> layer between TiN and poly-Si. In order to confirm this structure's feasibility, nMOSFETs and pMOSFETs with this type of gate electrode were fabricated.

#### 2. Experimental Results

The structure of this new gate electrode is shown in Fig .2. After gate doping by ion implantation and activation annealing, thin Ti was sputtered for improving the contact resistance between TiN and poly-Si. TiSi<sub>2</sub> was formed during gate cap LTO and RTA process.

To investigate a suitable thickness for inserted Ti, the contact resistance between TiN/TiSi<sub>2</sub> and n<sup>+</sup>poly-Si was measured with a parameter of Ti sputtered thickness. This result is shown in Fig.3. The thinner the Ti sputtered thickness is, the lower is the contact resistance. For a Ti thickness of 5 nm, a contact resistance as low as 130  $\Omega\mu$ m<sup>2</sup> was obtained. In order to find the reason for this result, SIMS measurements were made. The results are shown in Fig.4. The thicker TiSi<sub>2</sub> layer absorbs a higher amount of phosphorus that was implanted in poly-Si, and the decreased phosphorus concentration of the interface induced a high contact resistance.

Then, nMOSFETs and pMOSFETs with this gate structure were fabricated with 65 nm TiN layer. The process flow is shown in Table 1. For 65 nm TiN thickness, the sheet resistance was  $10\Omega/sq$ . and stayed constant for gate lengths down to 0.1  $\mu$ m as shown in Fig.5. As shown in

Fig.3 the sputtered Ti thickness in this fabrication process was 5 nm. BCl<sub>3</sub> and Cl<sub>2</sub> for the TiN/TiSi<sub>2</sub> layer, and HBr and O<sub>2</sub> for poly-Si were the gate etching chemis try,respectively. Fig.6 shows a SEM photomicrograph of the final MOSFET cross section. A 0.08 $\mu$ m long gate was successfully etched on 4 nm gate oxide.

Fig.7(a) shows the short channel effect of nMOSFETs and pMOSFETs. Fig7(b) shows Id-Vg characteristics. These characteristics were almost the same as for the conventional poly-Si gate structure. In order to evaluate lateral dopant diffusion through the TiSi<sub>2</sub> layer, we measured Vth shift as a function of the distance from the opposite impurity source. The results are shown in Fig.8(a),(b). The dopant lateral diffusion of this gate structure was comparable with a conventional poly-Si gate for both nMOSFETs and pMOSFETs. This is because TiSi<sub>2</sub> thickness is thin enough to prevent the dopant from moving through the TiSi<sub>2</sub> layer.

## 3. Conclusion

A new gate electrode structure of TiN/TiSi<sub>2</sub>/poly-Si was proposed. By using 5 nm Ti in order to form a thin TiSi<sub>2</sub> layer, the contact resistance between TiN and poly-Si can be sufficiently lowered to be accepted. nMOSFETs and pMOSFETs with the proposed gate structure that have a 4 nm gate oxide were fabricated. We showed that these MOSFETs have the same characteristics as a conventional poly-Si gate.

#### Acknowledgments

We wish to thank the members of the ULSI technology Laboratory of Fujitsu Labs. and the Process Development Division of Fujitsu for fabricating the devices.

#### References

M.T.Takagi et al., IEDM. Tech.Dig., pp.455-458, 1996

H. Wakabayashi et al., IEDM. Tech. Dig., pp. 447-450, 1996

[3] James R. Phiester et al., IEDM. Tech. Dig., pp. 241-244, 1990

[4] Y. Harada et al., Ext. Abstr.SSDM., pp. 174-176, 1993

[5] K.A. Jenkins et al., IEDM. Tech. Dig., pp. 891-894, 1993