# Improvement of SiO2/4H-SiC Interface by Using High Temperature Hydrogen Annealing at 1000°C

Kenji Fukuda <sup>1, 2</sup>, Kiyoko Nagai <sup>2</sup>, Toshihiro Sekigawa <sup>2</sup>, Sadafumi Yoshida <sup>2</sup>, Kazuo Arai <sup>2</sup>,

and Masahito Yoshikawa 3

<sup>1</sup> New Energy and Industrial Technology Development Organization, <sup>2</sup> Electrotechnical Laboratory, 1-1-4 Umezono, Tsukuba, Ibaraki 305-8568, Japan Phone/Fax: +81-298-54-3320, E-mail: kfukuda@etl.go.jp

<sup>3</sup> Japan Atomic Energy Research Institute, 1233 Watanuki, Takasaki, Gunma 370-1292, Japan

# 1. Introduction

Recently, high temperature, high power, and high frequency electronic devices fabricated from 6H- and 4H-SiC have been investigated intensely because of the excellent physical properties of SiC; i.e. high electric filed breakdown strength, high saturated electron velocity, and high thermal conductivity [1]. Especially, 4H-SiC MOSFET is one of the most influential candidates for these devices. However, the channel mobilites of 4H-SiC MOSFETs reported are lower than those of 6H-SiC MOSFETs although the mobility of 4H-SiC estimated from the Hall measurement is higher than that of 6H-SiC [2],[3]. One of reasons of the low channel mobility of 4H-SiC MOSFETs is thought that the interface state density D<sub>it</sub> is higher than that of 6H-SiC MOSFET.

We have fabricated 4H-SiC MOS capacitors and succeeded in the large improvement of SiO<sub>2</sub>/4H-SiC interface by using high temperature hydrogen annealing at 1000°C.

## 2. Experimental

$8^{\circ}$  off-angled n-type 4H-SiC (0001) wafers with a n-type epitaxial layer were obtained from Cree Reserch. After the standard RCA cleaning, a sacrifice oxide film was removed by HF solution. A 50nm thick gate oxide film was thermally grown at 1100°C in dry O<sub>2</sub>. Samples were annealed in H<sub>2</sub> (10 torr) at temperatures between 400°C and 1000°C for 30 minutes after the oxidation. Aluminum was evaporated on the top of the oxide film and on the back of the sample to make gate electrodes and ohmic contacts of MOS capacitors.

#### 3. Results and Discussion

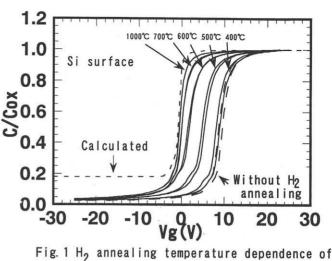

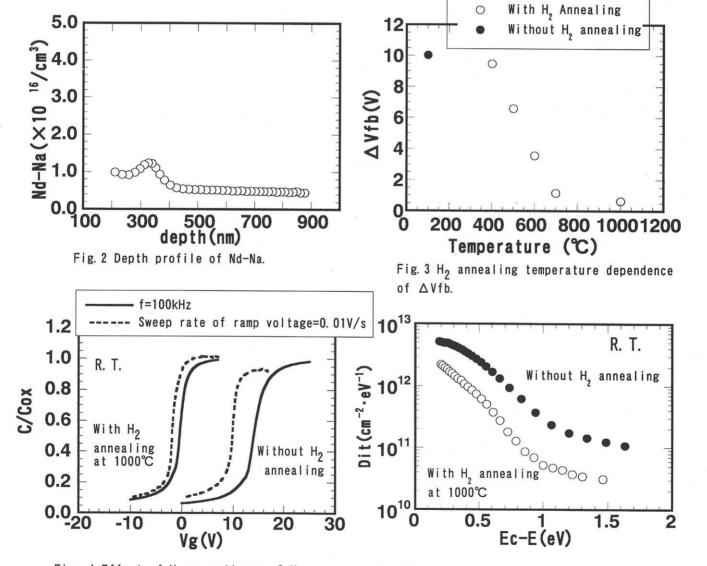

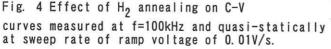

Fig. 1 shows H<sub>2</sub> annealing temperature dependence of 4H-SiC MOS C-V curves. The dotted line was calculated using the capacitance at 25V as the oxide capacitance and  $1 \times 10^{16}$  cm<sup>-3</sup> at 200nm in depth as the value of Nd-Na as shown in Fig. 2, where Nd is the donor density and Na is the acceptor density, respectively. The depth profile of Nd-Na was estimated from the C-V curve of the sample annealed in H<sub>2</sub> at 1000°C. In Fig. 1, the measured capacitances at Vg < -5V are lower than the calculated value due to the deep depletion. The measured C-V curve is very close to the ideal C-V one except for the deep depletion region, the hysteresis in C-V curve disappears, and the slope of C-V curve near the flat band voltage V<sub>fb</sub> is the steepest after H<sub>2</sub> annealing at 1000 °C. Fig. 3 shows H<sub>2</sub> annealing temperature dependence of the flat voltage shift  $\Delta V_{fb}$ . The value of  $\Delta V_{fb}$  hardly changes till 400°C, decreases drastically above 400°C, and tend to saturate around 1000°C. The value of  $\Delta V_{fb}$  of the sample with H<sub>2</sub> annealing at 1000°C is 0.64V. These mean that Dit and the negative charges which exist at the SiO<sub>2</sub>/4H-SiC interface or in SiO<sub>2</sub> film decrease with H<sub>2</sub> annealing temperature. Fig. 4 shows C-V curves measured by two methods to investigate the effect of H<sub>2</sub> annealing on the distribution of D<sub>it</sub> in the energy band-gap. The solid C-V curves were measured quasi-statically at the sweep rate of ramp voltage=0.01V/s. The value of D<sub>it</sub> is described as

$$D_{it} = \frac{1}{e} \left( \left( \frac{1}{C_q} - \frac{1}{C_{ox}} \right)^{-1} \left( \frac{1}{C_h} - \frac{1}{C_{ox}} \right)^{-1} \right).$$

(1)

where e is the electronic charge,  $C_q$  is the quasi static capacitance,  $C_h$  is the capacitance measured at f=100kHz, and  $C_{OX}$  is the oxide capacitance, respectively [4]. The difference of capacitance measured by two methods decreases after H<sub>2</sub> annealing at 1000°C, which means that D<sub>it</sub> was reduced. The distributions of D<sub>it</sub> in the energy band-gap estimated from eq. (1) are shown in Fig 5 as a function of energy(Ec-E) from the conduction band edge. The value of Dit is underestimated more than about 0.6 eV because the measurement was conducted at room temperature[5]. However, the value of D<sub>it</sub> after H<sub>2</sub> annealing at 1000°C is about one-fifth of that of the sample without H<sub>2</sub> annealing. This distribution of D<sub>it</sub> nearly equals to that of 6H-SiC MOS capacitor [6].

#### 4. Conclusion

We have succeeded in the formation of excellent SiO<sub>2</sub>/4H-SiC interface by using high temperature H<sub>2</sub> annealing at 1000°C. The hysteresis in C-V curve disappears, the value of  $\Delta V_{fb}$  is 0.64V, and D<sub>it</sub> is reduced to about one-fifth by H<sub>2</sub> annealing at 1000°C after the oxidation.

## References

- 1) Chapter 7 of proceedings of ICSCIII-N'97, Stockholm, Sweden (1997).

- T.Kimoto, A. Itoh, and H. Matsunami: physica status solidi(b) 202,No1(1997),p.247.

- Ravi K. Chilukuri, Praveen M. Shenoy and B.Jayant Baliga:proceedings of ISPSD'98, (1998),p.115.

- E.H.Nicollian and J.R.Brew: MOS (Metal Oxide Semiconductor)Physics and Technology,p.332.

- 5) J. A. Cooper, jr: physica status solidi(a) 162,No1(1997),p.305.

- 6) V.V.Afanasev,M.Bassler,G.Pensl, and M.Schulz: physica status solidi(a)162, No1(1997),p.321.

C-V curve of 4H-SiC MOS capacitor. Cox is the oxide capacitance and Vg is the gate voltage.

Fig. 5 Distribution of Dit in energy band-gap as a function of energy from the conduction band edge.