# Sub 1.3nm Amorphous Ta<sub>2</sub>O<sub>5</sub> Gate Dielectrics for Damascene Metal Gate Transistor

Seiji Inumiya, Atsushi Yagishita, Tomohiro Saito, Masaki Hotta, Yoshio Ozawa, Kyoichi Suguro, Yoshitaka Tsunashima and Tsunetoshi Arikado

Microelectronics Engineering Laboratory, Semiconductor Company, Toshiba Corporation 8 Shinsugita-cho, Isogo-ku, Yokohama 235-8522, Japan Phone:+81-45-770-3661 Fox:+81-45-770-2577 constitution

Phone:+81-45-770-3661 Fax:+81-45-770-3577 e-mail: inumiya@amc.toshiba.co.jp

## 1. Introduction

Recently, Ta2O5 has attracted much attention as an alternative gate dielectrics for sub 0.1µm devices. In most of the recent studies of Ta2O5 gate dielectrics, poly-crystalline Ta<sub>2</sub>O<sub>5</sub> was used in order to obtain higher dielectric constant and to reduce leakage current [1], or to activate impurities in source/drain [2,3]. However, regarding the application of poly-crystalline Ta2O5 for gate dielectrics, there has been concern about Vth fluctuation [4] according to the anisotropy of dielectric constant [5] and increase of total equivalent oxide thickness due to the interaction at Ta2O5/Si interface in crystallization step. Our damascene metal gate transistor process [6] makes application of amorphous Ta2O5 for the gate dielectrics possible. In this paper, the characteristics of amorphous Ta2O5 gate dielectrics were investigated, and a simple and desirable formation process was proposed for application to sub 0.1µm devices.

### 2. Results and Discussions

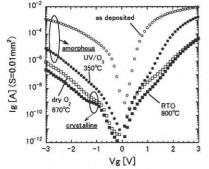

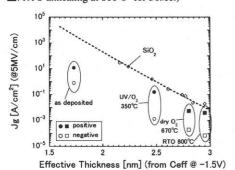

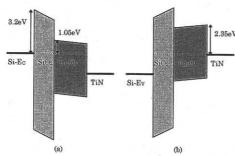

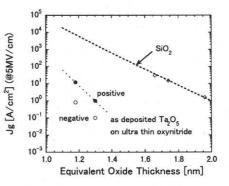

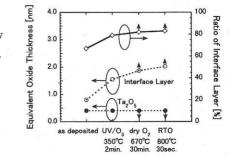

Figure 1 shows the I-V characteristics of  $Ta_2O_5$  gate dielectrics which were deposited ( $\sim 3.5$ nm) on ultrathin oxynitride (T<sub>eq\_ox</sub>~0.8nm) at 550°C with Ta(OC<sub>2</sub>H<sub>5</sub>)<sub>5</sub> and O2. Various kinds of post-deposition annealing were performed on some of the samples. The leakage current under positive gate bias is higher than negative gate bias for all samples. Therefore, it is necessary to discuss the leakage current reduction under positive gate bias condition, whereas in most reports only the leakage current under negative gate bias were discussed. Under the positive gate bias, low-k material such as SiO2 exists at the cathode side, thus the . barrier height of Ta2O5 (high-k material) drops throughout the film (Fig. 2). Obviously, the barrier height drop becomes large with the increase of low-k film's thickness ratio. Figure 3 shows estimated equivalent thickness of Ta2O5 and interface low-k films, and it's ratio for every sample in Fig. 1. During post-deposition annealing the interface layer thickness become thick by interface oxidation, and it's ratio for total thickness increases. All samples, with the exception of as-deposited one, are too thick for application to sub 0.1µm devices. The As-deposited sample can only realize sub 2nm effective thickness and the merit of high-k is expected to be available. Figure 4 shows a comparison of leakage current with the case of SiO2 under the same electric field. Under positive gate bias, only as-deposited Ta2O5 can reduce leakage current effectively. Figure 5 shows leakage current density of different thickness Ta2O5 deposited on the same interface layer. The horizontal axis indicates equivalent oxide thickness which is calculated from C-V characteristics of TiN

gate MOS capacitor. Ultrathin (<1.3nm) equivalent oxide thickness was attained with reduction of leakage current to about 3 orders lower than in case of conventional  $SiO_2$  even under positive gate bias.

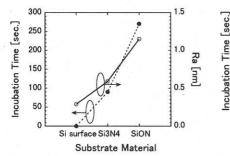

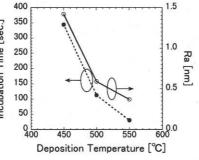

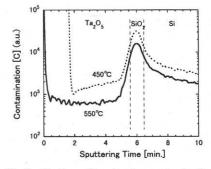

In DRAM capacitor process, Ta2O5 is deposited at 400-450℃ in order to obtain good step coverage. In the case of deposition at low temperature, as-deposited films contain a large amount of hydrocarbon contamination from the organic source materials. In order to reduce leakage current, postdeposition annealing is necessary, such as UV/O3, plasma oxygen or high-temperature O<sub>2</sub> annealing. On the other hand, as mentioned above, post-deposition annealing is not desirable in the case of gate application due to the absence of the barrier ability for interface oxidation. However, hightemperature deposited Ta2O5 films contain less organic contamination as shown in Fig. 6, thus reduction of leakage current is realized regardless of no post-deposition annealing. To realize Ta2O5/SiON stacked dielectrics, the surface morphology of Ta2O5 films on SiO2 or SiON becomes poor due to long incubation time in the initial stage of lowtemperature deposition (Fig. 7). Another merit of hightemperature deposition is improvement of surface morphology. The incubation time becomes short and the surface roughness becomes small with the increase of temperature, even in the case of deposition on SiO2 or SiON (Fig. 8).

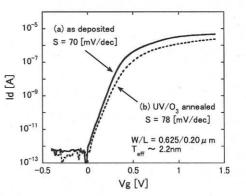

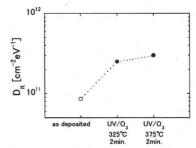

The interface characteristic is one of the most important feature for gate dielectrics. Interface trap density (Dit) is increased by low-temperature additional oxidation such as UV/O<sub>3</sub> annealing (Fig. 9). Although the Dit is decreased by RTA at 800°C for 30min, high-temperature annealing is not desirable because of crystallization and thickness increase. Figure 10 shows subthreshold characteristics of NMOSFET fabricated by damascene gate process with Al/TiN gate electrode. Superior sub-threshold swing (S-factor:70mV/dec) is obtained for sample with as-deposited Ta<sub>2</sub>O<sub>5</sub>, as expected from the above interface characteristics.

### 3. Conclusions

We propose sub 1.3nm amorphous  $Ta_2O_5$  gate dielectrics process for sub 0.1µm CMOS devices for the first time.  $Ta_2O_5$  deposition at high temperature makes the surface roughness small and decreases the contamination in films. Increase of interface layer thickness is suppressed by not applying post-deposition oxidation, and therefore, ultrathin equivalent oxide thickness is realized and good interface characteristics are realized. In combination with damascene metal gate process, high-performance MOSFET was realized.

#### Acknowledgments

The authors would like to thank Mr. S. Takagi for valuable discussion. They are also grateful to Mr. T. Shimizu and the staff of Tokyo Electron Ltd. for their cooperation.

#### References

[1] A. Chatterjee, et al., IEDM Technical Digest, p.777, 1998.

Fig. 1 I-V characteristics of  $Ta_2O_5/SION$  capacitors with CVD TiN electrode. N-type and P-type Si substrates were used for positive and negative gate bias measurement, respectively. ( $\bigcirc$ : no annealing,  $\oplus$ : UV/O<sub>3</sub> annealing at 350°C for 2min.,  $\square$ : dry O<sub>2</sub> annealing at 670°C for 30min.,  $\blacksquare$ : RTO annealing at 800°C for 30sec.)

Fig. 4 Leakage current comparison of Ta<sub>2</sub>O<sub>5</sub>/SiON stacked and SiO<sub>2</sub> under the same effective electric field. Broken line indicates calculation of tunneling current for SiO<sub>2</sub> using m\*=0.46m,  $\phi_B$ =3.2 and  $\epsilon_r$ =3.9 fitting to the measured date.

Fig. 2 Band diagrams of  $Ta_2O_5/SiO_2$  stacked dielectrics under (a) positive gate bias and (b) negative gate bias. Equivalent oxide thickness of SiO<sub>2</sub> and Ta<sub>2</sub>O<sub>5</sub> is 1.5nm and 0.5nm, respectively.

Fig. 5 Leakage current of different thickness  $Ta_2O_5$  deposited on the same interface layer. Horizontal axis indicates equivalent oxide thickness which is calculated from accumulation capacitance at Ns=5E12cm<sup>-2</sup> by extracting the effect of surface capacitance[7].

Fig. 8 Deposition temperature dependence of incubation time and the surface roughness Ra. (deposition on SiO<sub>2</sub>)

Fig.10 Subtreshold characteristic of damascene Al/TiN gate transistor with  $Ta_2O_5$  /SiO<sub>2</sub> gate dielectrics. (a)  $Ta_2O_5$  is deposited on SiO<sub>2</sub> interface layer. (b)  $Ta_2O_5$  is deposited on Si surface and SiO<sub>2</sub> formed by UV/O<sub>3</sub> annealing at the interface between Si and  $Ta_2O_5$ .

- [2] Y. Momiyama, et al., Symp. VLSI Tech., p.135, 1997.

- [3] D. Park, et al., IEDM Technical Digest, p.381, 1998.

- [4] C. Chaneliere, et al., J. Appl. Phys. 83, 4823 (1998)

- [5] Y. Nakagawa, et al., J. Appl. Phys. 68, 556 (1990)

- [6] A. Yagishita, et al., IEDM Technical Digest, p.785, 1998.

- [7] S. Takagi, et al, to be published.

Fig. 3 Equivalent oxide thickness of  $Ta_2O_5$ layers and interface layers, and ratio of interface layers for samples shown in Figure 1. Equivalent oxide thickness of crystalline  $Ta_2O_5$ will be thinner than that of amorphous  $Ta_2O_5$ .

Fig. 6 . Depth profiles of carbon contamination in  $Ta_2O_5$  films deposited at  $450\,^\circ\!\!C$  and  $550\,^\circ\!\!C.$

Fig. 9 Interface trap density of Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub>/Si system with or without post-deposition annealing.