# TaO<sub>x</sub>N<sub>y</sub> Gate Dielectric with Improved Thermal Stability

Heung-Jae Cho, Dae-Gyu Park, In-Seok Yeo, Jae-Sung Roh, and Jeong-Mo Hwang

Advanced Process Team, Memory R&D Division, Hyundai Electronics Industries Co. Ltd.,

Ichon P.O. Box 1010, Ichon-si, Kyoungki-do, Korea 467-701

Phone: +82-336-630-4466 Fax: +82-336-630-4545 e-mail: hjaecho@sr.hei.co.kr

#### ABSTRACT

We report characteristics of  $TaO_xN_y$  gate dielectric with improved thermal stability and favorable flat band shift over  $Ta_2O_5$  for giga scale memory devices. Compared with  $Ta_2O_5$ , W/WN/TaO\_xN\_y/SiO\_2/Si *n*MOS capacitors demonstrated negative  $V_{fb}$  shift (-0.17 V) and robust reliability against selective oxidation at 950 °C. Interface state density ( $D_{it}$ ) as low as  $8.5 \sim 15 \times 10^{10} \text{ eV}^{-1} \text{cm}^{-2}$  near the midgap and excellent reliability characteristics with low gate leakage current are encouraging for future memory devices.

#### **INTRODUCTION**

$Ta_2O_5$  has attracted lots of attention for MOS device applications such as storage capacitors[1] and gate dielectrics[2-5] because of high dielectric constant (k~25) and good leakage current. There are some problems, however, such as chemical reaction between  $Ta_2O_5$  and poly-Si, which led to the employment of stable electrodes such as refractory metal or metal nitrides [1-4]. Owing to the high work function of metal nitrides, it is difficult to obtain low threshold voltage in MOSFET device [4,5]. In addition, the fragility of metal/ $Ta_2O_5$  structure against post thermal budget in oxidation ambient becomes a serious issue for device reliability and requires new fabrication scheme. In the present work, we implemented a novel process to overcome the problems associated with threshold voltage and thermal stability using  $TaO_xN_y$  gate dielectric.

#### **EXPERIMENTAL**

nMOS capacitors and transistors having W/barrier metal/ Ta2O5/SiO2/p-Si structure were fabricated. Ta2O5 was deposited on the ultrathin (~5-10Å) SiO<sub>2</sub> using Ta(OC<sub>2</sub>H<sub>5</sub>)<sub>5</sub> and O2 at 400°C, whereas TaOxNy was prepared using Ta(OC<sub>2</sub>H<sub>5</sub>)<sub>5</sub> and NH<sub>3</sub>[6]. Gate dielectric improvement anneals were carried out in ultraviolet-ozone at 350 °C and in O2 at 800°C. Then, W/barrier metal (TiN or WN) electrodes were sputter-deposited on gate dielectric and annealed in N2 at 700-800 °C for 30 minute. In order to investigate the effect of selective oxidation (SO) on gate dielectric, samples were oxidized in H₂-rich oxidant ambient at 950 °C for 2 minute. Fundamental film properties were probed by X-ray photoelectron spectroscopy (XPS) and auger electron spectroscopy (AES). Interfacial and electrical properties of W/barrier/TaOxNv/SiO2/Si MOS capacitors were measured using C-V, conductance, I-V, breakdown voltage (BV), and time dependent dielectric breakdown (TDDB) methods.

#### **RESULTS AND DISCUSSIONS**

## A. W/Metal barrier/Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub>/Si nMOS System

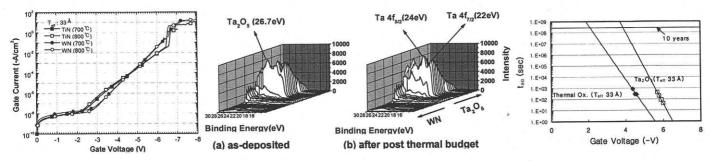

Shown in Fig. 1 is leakage current density of  $Ta_2O_5$  film with different metal gate electrode, where WN exhibited lower gate leakage than TiN near 2-3 V range after anneal at 700°C ~ 800°C. Fig. 2 shows sharp WN/Ta<sub>2</sub>O<sub>5</sub> interface as

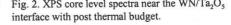

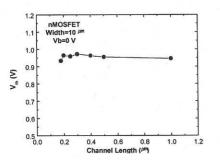

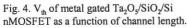

detected by XPS core level spectra, confirming stable WN with  $Ta_2O_5$  at elevated temperature. We observed interfacial reaction at TiN/Ta<sub>2</sub>O<sub>5</sub> interface, however, due to the solubility of Ta in TiN [1]. A projected 10-year lifetime of WN/Ta<sub>2</sub>O<sub>5</sub> (Fig.3) as determined by TDDB under the constant stress reveals superior lifetime to the thermal oxide. An electric field of over ~10 MV/cm may be used at room temperature using WN/Ta<sub>2</sub>O<sub>5</sub>. Fig. 4 displays the threshold voltage (V<sub>th</sub>) of metal gated Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub>/Si nMOSFET with high V<sub>th</sub>(~1V), which is consistent with the earlier works [4,5].

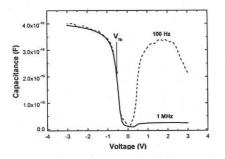

## B. W/WN/TaOxN/SiO2/Si nMOS System

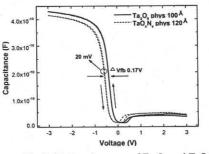

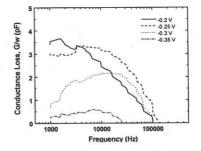

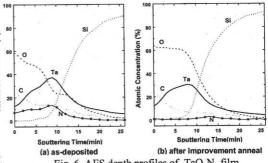

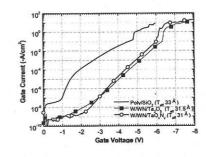

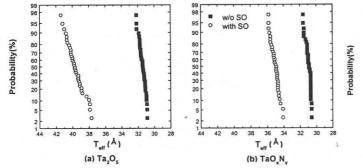

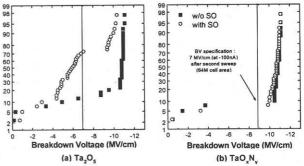

In order to reduce V<sub>th</sub> by controlling charges in gate dielectrics, we developed  $TaO_xN_y$  gate dielectric. Fig. 5 depicts high frequency C-V plots with  $TaO_xN_y$ , plots with TaO, N,, demonstrating negative shift (-0.17 V) in flat band condition with respect to Ta<sub>2</sub>O<sub>5</sub> and small hysteresis (20 mV). The AES depth profiles of TaO<sub>x</sub>N<sub>y</sub> films in Fig. 6 indicate that nitrogen was diffused out or piled up at SiO<sub>2</sub>/Si interface after improvement anneal. The negative flat band shift is attributed to the N induced positive charges, resulting in a favorable Vth for high performance nMOSFET. Figs. 7-8 are high-low C-V and G/ $\omega$ -log $\omega$  plots of W/WN/TaO<sub>x</sub>N<sub>y</sub>/ SiO<sub>2</sub>/Si nMOS capacitors after anneal in forming gas. Excellent frequency dispersion between 1 MHz and 100Hz except the midgap region is observed. The D<sub>it</sub> as determined by conductance loss  $(G/\omega)$  near the midgap including small hump region is in the order of  $8.5 \sim 15 \times 10^{10} \text{ eV}^{-1} \text{ cm}^{-2}$ . Fig. 9 displays J-V characteristics of TaOxNy and Ta2O5 at the same  $T_{eff} \sim 31 \text{ Å}$ , where the gate leakage of  $TaO_x N_y$  is ~5 orders of magnitude lower than that of poly-gated SiO<sub>2</sub> at -2.5 V. The highlight of this work is improved thermal stability using  $TaO_xN_v$  even after SO at 950 °C (Figs.10-11). TaO<sub>x</sub>N<sub>v</sub> showed durable reliability characteristics over Ta2O5 in terms of less increase in  $T_{eff}$  (Fig.10) and higher BV pass rate on 64 million memory cell capacitors (Fig.11). Excellent BV distribution (11 MV/cm) of TaO<sub>x</sub>N<sub>y</sub> film even after selective oxidation indicates that TaO<sub>x</sub>N<sub>y</sub> film may allow us to keep up the standard CMOS fabrication process and technology.

#### CONCLUSIONS

WN gate electrode demonstrated stable interface with  $Ta_2O_5$ at the elevated temperature over TiN. Compared with  $Ta_2O_5$ ,  $TaO_xN_y$  gate dielectric exhibited good-natured negative  $V_{fb}$ shift and durability against high temperature selective oxidation. Characteristics such as low  $D_{it}$  low gate leakage current, and excellent reliability are promising for future DRAM devices.

## REFERENCES

- [1] M.-B. Lee et al., J. Appl. Phys. p.139 (1998).

- [2] D. Park et al., IEDM Tech. Digest. p.381 (1998).

- [3] A. Chatterjee et al., IEDM Tech. Digest. p.777 (1998).

- [4] T. Devoivre et al., VLSI Tech. Dig., p.131 (1999).

- [5] I.C.Kizilyalli, et al IEEE Electron Devices Lett., 19, 423 (1998).

- [6] H.-J. Cho, et al., Patent Pending.

Fig. 1. J-V characteristics of  $Ta_2O_5$  with TiN and WN Fig. 2. XPS core level spectra near the WN/ $Ta_2O_5$ barrier metal as a function of post thermal budget.

(%)

ration

Conce

Atomic

Fig. 3. Time to 50% cumulative failure of W/WN/Ta2O5/SiO2/Si nMOS capacitor.

Fig. 7. High-low C-V characteristics of WN/W TaO<sub>x</sub>N<sub>y</sub> /SiO<sub>2</sub>/Si nMOS capacitor.

Fig. 5. Hysteresis curves of Ta2O5 and TaOxNy nMOS capacitors.

Fig. 8. Conuctance loss  $(G/\omega)$  - log  $\omega$  plot as a function of gate voltage near the midgap.

Fig. 9. J-V characteristics of Ta2O5 and TaOxNy films compared with controlled oxide.

Fig. 10. T<sub>eff</sub> change after selective oxidation.

Fig. 11. Cumulative probability of breakdown field on 64 M cell area.