## C-4-3 The Influence of the Device Miniaturization on the I<sub>on</sub> Enhancement in the Intrinsic Silicon Body (*i-body*) SOI-MOSFET's

Risho Koh, Hisashi Takemura, Kiyoshi Takeuchi and Tohru Mogami

Silicon Systems Research Laboratories, NEC Corporation Shimokuzawa 1120, Sagamihara, Kanagawa, 229-1198, Japan phone:+81- 42-779-6193, Fax: +81-42-771-0886, E-mail: r-koh@ah.jp.nec.com

**1.Introduction** An SOI-MOSFET with intrinsic Si body (*i-body*) has a very attractive feature that a small effective vertical electric field ( $E_{\rm eff}$ ) enhances the carrier mobility ( $\mu$ )[1]. However, it is not clear whether the device miniaturization[2], in which the device parameters such as the gate length (L), the supplied voltage ( $V_{\rm DD}$ ) and the gate oxide thickness ( $T_{\rm OX}$ ) are scaled down, enhances or reduces the advantage. Therefore, a systematical simulation is performed for device generations from L=0.25 to 0.05  $\mu$  m. It was found that  $\mu$  enhancement and ON current ( $I_{\rm ON}$ ) enhancement in *i-body* SOI-MOSFETs become significant as the device generation advances (e.g., 38%  $I_{\rm ON}$  improvement for L=0.25  $\mu$  m and 55% for 0.1  $\mu$  m, for a low power device), since the device has an ability to suppress  $E_{\rm eff}$  which increases in a small bulk MOSFET.

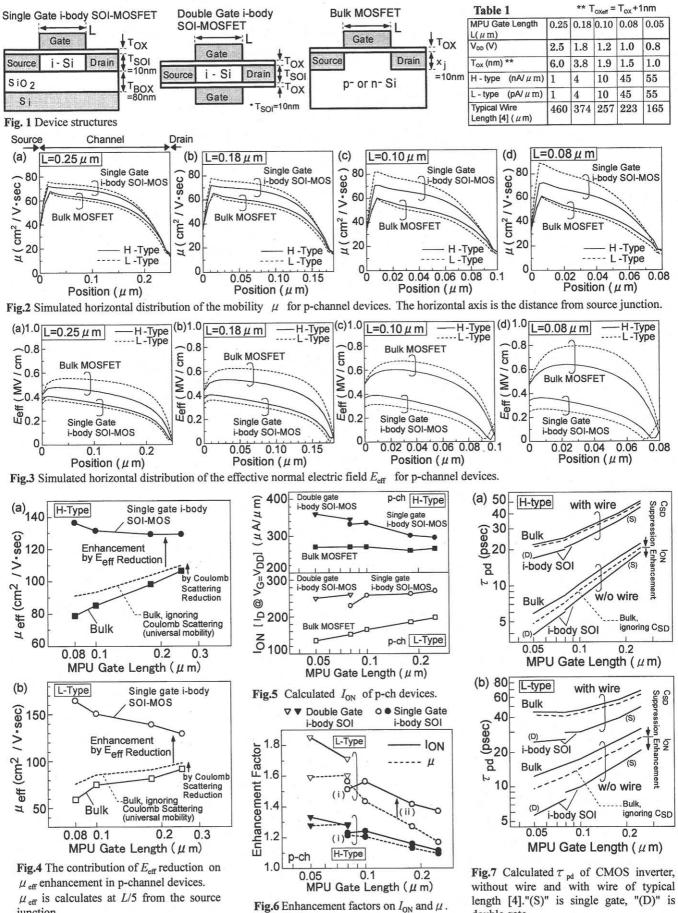

**2.Simulation** Single gate and double gate *i-body* SOI-MOSFETs are assumed, and a uniformly doped Bulk MOSFETs as well (Fig.1). The threshold voltages ( $V_{th}$ ) of *i-body* device are controlled by the work function of gate electrode.  $T_{SOI}$  and  $T_{BOX}$  (see Fig.1) are fixed at 10nm and 80nm, respectively. The device generation is represented by the MPU gate length *L* (Table.1).  $V_{DD}$  and  $T_{OX}$  are determined after ITRS[2] and SIA[3] roadmap. The OFF current ( $I_{OFF}$ ) for low power device (L-type) is 3 orders of magnitude smaller than that of high performance device (H-type). The typical wire length for each generation is determined after[4]. Since a drift and diffusion 2D simulator used here can not model the velocity overshoot which is significant in n-channel devices, p-channel devices are mainly discussed.

3.  $\mu$  and  $I_{\rm ON}$  Figure 2 shows the position dependence of  $\mu$  for p-channel devices, which is a function of the low field mobility  $\mu_{\rm eff}$  [5] and the horizontal field. It is evident that the  $\mu$  enhancement in *i-body* SOI-MOSFETs becomes remarkable as the devices are miniaturized. Since it is known that an increase in effective vertical electric filed ( $E_{\rm eff}$ ) degrades  $\mu_{\rm eff}$  [5],  $E_{\rm eff}$  is calculated as shown in Fig.3. The results show that  $E_{\rm eff}$  increases only in the bulk MOSFETs when the generation advances. Therefore,  $E_{\rm eff}$  reduction in *i-body* device becomes remarkable as the devices are miniaturized. This leads to the enhancement in  $\mu_{\rm eff}$  (Fig.4),  $I_{\rm ON}$  and  $\mu$  (Figs. 5 and 6) in a small *i-body* device.

The  $I_{\rm ON}$  enhancement in H-type devices almost follows that of  $\mu$  (Fig.6), with the exception of 0.08  $\mu$  m single gate device "(i)" which is affected by the short channel effect (a similar degradation appears in L-type).  $I_{\rm ON}$  enhancement in L-type devices is much larger. One reason is that the  $E_{\rm eff}$ reduction is more remarkable, since higher  $V_{\rm th}$  increases the  $E_{\rm eff}$  of bulk devices and low inversion charge density is efficient for decreasing  $E_{\rm eff}$  of *i-body* devices. An additional effect which is attributed to the S factor improvement and a horizontal field enhancement due the SOI structure, is also significant in the L-type devices ("(ii)" in the figure ).

**4.Discussions on the**  $\mu$  enhancement  $E_{\text{eff}}$  in p-channel bulk device is given by

$$E_{\rm eff} = qN_{\rm s}/3\varepsilon_{\rm Si}\varepsilon_{\rm 0} + qN_{\rm dpl}/\varepsilon_{\rm Si}\varepsilon_{\rm 0}$$

(1)

where, q is the elementary charge,  $N_{dpl}$  is the depletion charge area density,  $N_s$  is inversion charge area density,  $\varepsilon_{si}$  is dielectric constant of Si and  $\varepsilon_0$  is that of vacuum. By substituting usual equation on  $V_{th}$  for eq.(1), one obtains

$$E_{\rm eff} = qN_{\rm s}/3\varepsilon_{\rm Si}\varepsilon_0 + q(V_{\rm th}-\Phi_{\rm ms}-2\Phi_{\rm F})\varepsilon_{\rm OX} / \varepsilon_{\rm Si}T_{\rm ox}$$

(2)

where,  $\phi_{\rm ms}$  is the work function difference between gate and source,  $\phi_{\rm F}$  is the Fermi potential. Through the miniaturization, a large variation in  $T_{\rm OX}$  is required to achieve appropriate  $I_{\rm ON}$ , however, in order to suppress  $I_{\rm OFF}$ ,  $V_{\rm th}$  can not be largely scaled down. Therefore, the second term in eq.2 increases and consequently  $E_{\rm eff}$  increases as the generation of bulk device advances.

In contrast,  $E_{\rm eff}$  of i-body SOI-MOSFET is given by  $E_{\rm eff} = q N_{\rm s} / 3 \varepsilon_{\rm Si} \varepsilon_0$ . The equation does not have the second term which appears in the equation for bulk device [eqs.(1) or (2)]. Therefore, the difference in  $E_{\rm eff}$  between the bulk and *i-body* devices is enhanced in small devices.

5.Comparizon in the switching speed Figure 7 shows the comparison on the switching speed of CMOS inverter, calculated by using a relation  $\tau_{pd} = (C_{OX}+C_{SD}+C_{load})V_{DD} / I_{ON}$ . A large  $I_{ON}$  of *i-body* device, which is originated from a small  $E_{eff}$ , greatly improves  $\tau_{pd}$  of a small device. L-type 0.05  $\mu$  m *i-body* double gate device shows nearly half  $\tau_{pd}$ compared to that of bulk device.

**6.Conclusions** From a set of simulation, it was found that  $\mu$  and  $I_{ON}$  enhancement in *i-body* SOI-MOSFET becomes remarkable as the device is miniaturized, since the  $E_{eff}$  of the device does not increase through the miniaturization. It was also shown that the advantages of *i-body* device are more remarkable in low stand-by power devices having large  $V_{th}$ .

Acknowledgment This work was partly supported by the New Energy and Industrial Technology Development Organization (NEDO).

- [1] M.Yoshimi, et.al, Electron Lett. Vol.24, p.1078 (1988)

- [2] International technology roadmap for semiconductors (1999)

- [3] The national technology roadmap for semiconductors (1997)

- [4] W.E.Donath, et.al, IEEE CAS-26, p.272

- [5] S.Takagi,, et.al, 1998 IEDM Tech. Dig., p.398

$\mu_{\rm eff}$  is calculates at L/5 from the source junction.

double gate.